在22nm,或許是16nm節(jié)點,我們將需要全新的晶體管。而在這其中,爭論的焦點在于究竟該采用哪一種技術(shù)。這場比賽將關(guān)乎到晶體管的重新定義。在22/20nm邏輯制程的開發(fā)中,業(yè)界都爭先

2012-03-06 10:08:16 2292

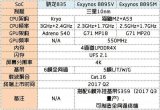

2292 今日,三星電子正式宣布已經(jīng)開始大規(guī)模生產(chǎn)基于10nm FinFET技術(shù)的SoC,這是業(yè)界內(nèi)首家提供10nm工藝代工廠商。新工藝下的SoC性能可以提供27%,功耗將降低40%。

2016-10-17 14:07:01 1208

1208 隨著半導(dǎo)體制造工藝的提升,晶體管密度提升越來越困難,摩爾定律的存廢也引起了很大的爭議。14nm工藝的延期打亂了Intel的Tick-Tock戰(zhàn)略,后面的產(chǎn)品也不得不跟著變化,首款14工藝產(chǎn)品

2017-01-02 21:14:08 1298

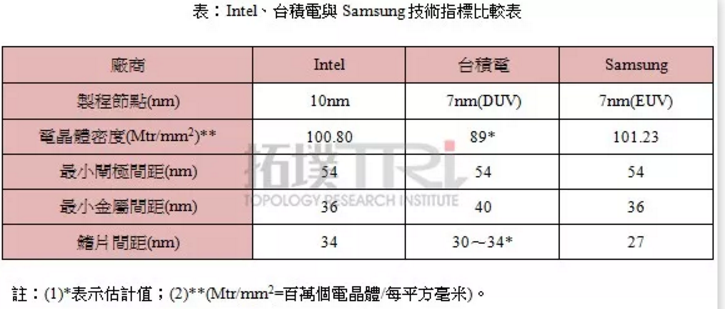

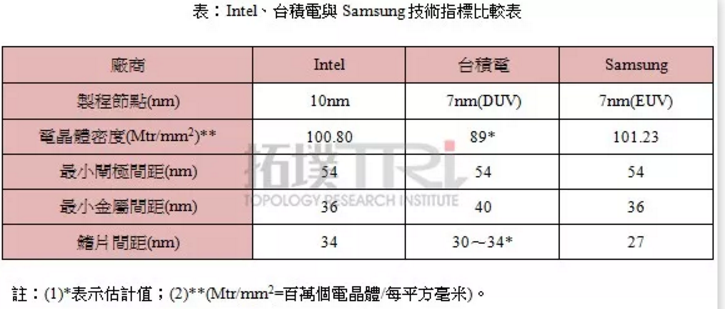

1298 近日,有臺媒對比了半導(dǎo)體工藝10nm及以下制程的技術(shù)指標演進對比圖,其中技術(shù)指標主要是看晶體管密度,也就是每平方毫米的晶體管數(shù)量。由于目前僅有Intel、臺積電、三星等少數(shù)幾家廠商掌握了10nm以下

2021-07-17 07:14:00 5704

5704 GPU和CPU產(chǎn)品依舊在使用五年前的14nm工藝或者其改進版本。新的10nm、7nm工藝雖然已經(jīng)上市,但是綜合頻率、功耗、晶體管密度等因素來看,其表現(xiàn)依舊不能令人滿意。進入2020年,也就是21世紀20

2020-07-07 11:38:14

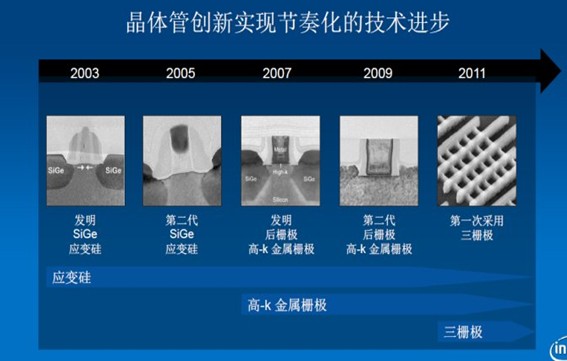

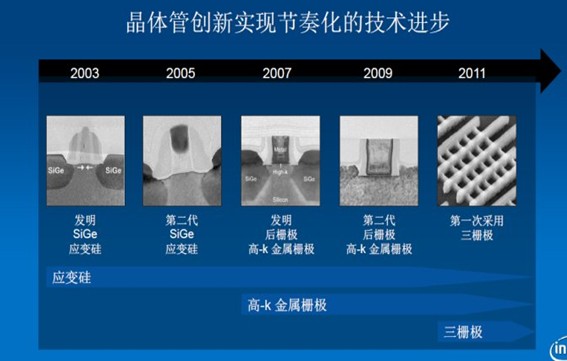

其實早在2002年Intel即發(fā)現(xiàn)了這一技術(shù),一直處于試驗演示階段,現(xiàn)在終于把它變成了現(xiàn)實,Intel打算把它融入到22nm的“Ivy Bridge”芯片,Ivy Bridge晶體管的數(shù)量將達到10億。

2020-04-07 09:01:21

8050的情況下,補碼通常是8550。8050和8550晶體管的技術(shù)額定值通常是相同的。區(qū)別在于它們的極性。它們共同允許電流安全地流過無線電和無線電,從而為傳輸提供動力,并允許在用戶端實現(xiàn)多種功能

2023-02-16 18:22:30

很多晶體管組成的。芯片制程是指在芯片中,晶體管的柵極寬度。因為在整個芯片中,晶體管的柵極是整個電路中最窄的線條。如果柵極寬度為10nm,則稱其為10nm制程。納米數(shù)越小,比如從10nm到 7nm,就可以

2019-12-10 14:38:41

晶體管技術(shù)方案面臨了哪些瓶頸?

2021-05-26 06:57:13

的B和C對稱、和E極同樣是N型。也就是說,逆接C、E也同樣有晶體管的功效。即電流由E→C流動。3. 逆向晶體管有如下特點。hFE低(正向約10%以下)耐壓低 (7 to 8V 與VEBO一樣低)↑通用

2019-04-09 21:27:24

晶體管之間的差異性:就三極管,mos管和可控硅之間的差別和相同點的相關(guān)概念有點模糊,請各位大俠指點!!!

2016-06-07 23:27:44

晶體管分類 按半導(dǎo)體材料和極性分類 按晶體管使用的半導(dǎo)體材料可分為硅材料晶體管和鍺材料晶體管。按晶體管的極性可分為鍺NPN型晶體管、鍺PNP晶體管、硅NPN型晶體管和硅PNP型晶體管。 按結(jié)構(gòu)

2010-08-12 13:59:33

晶體管參數(shù)測量技術(shù)報告摘 要晶體管的參數(shù)是用來表征管子性能優(yōu)劣和適應(yīng)范圍的指標,是選管的依據(jù)。為了使管子安全可靠的工作,必須注意它的參數(shù)。本文主要論述以AduC812為核心的晶體管參數(shù)測試系統(tǒng),該系

2012-08-02 23:57:09

` 《晶體管電路設(shè)計(下)》是“實用電子電路設(shè)計叢書”之一,共分上下二冊。本書作為下冊主要介紹晶體管/FET電路設(shè)計技術(shù)的基礎(chǔ)知識和基本實驗,內(nèi)容包括FET放大電路、源極跟隨器電路、功率放大器

2019-03-06 17:29:48

,發(fā)射極E接紅表筆;PNP管的集電極C接紅表筆,發(fā)射極E接黑表筆。正常時,鍺材料的小功率晶體管和中功率晶體管的電阻值一般大于10Kω(用R×100檔測,電阻值大于2kΩ),鍺大功率晶體管的電阻值為1.5k

2012-04-26 17:06:32

晶體管測量模塊的基本特性有哪些?晶體管測量模塊的基本功能有哪些?

2021-09-24 07:37:23

從事電子設(shè)計7年了,發(fā)覺這兩本書挺好的,發(fā)上來給大家分享一下附件晶體管電路設(shè)計(上)放大電路技術(shù)的實驗解析.pdf42.5 MB晶體管電路設(shè)計(下)FET_功率MOS_開關(guān)電路的實驗解析.rar.zip47.2 MB

2018-12-13 09:04:31

`非常不錯的晶體管電路設(shè)計書籍!`

2016-11-08 14:12:33

晶體管的主要參數(shù)有哪些?晶體管的開關(guān)電路是怎樣的?

2021-06-07 06:25:09

本篇開始將為大家介紹“Si晶體管”。雖然統(tǒng)稱為“Si晶體管”,不過根據(jù)制造工藝和結(jié)構(gòu),還可分為“雙極”、“MOSFET”等種類。另外,還可根據(jù)處理的電流、電壓和應(yīng)用進行分類。下面以“功率元器件”為主

2018-11-28 14:29:28

100V到700V,應(yīng)有盡有.幾年前,晶體管的開關(guān)能力還小于10kW。目前,它已能控制高達數(shù)百千瓦的功率。這主要歸功于物理學(xué)家、技術(shù)人員和電路設(shè)計人員的共同努力,改進了功率晶體管的性能。如(1)開關(guān)晶體管

2018-10-25 16:01:51

晶體管概述的1. 1948年、在貝爾電話研究所誕生。1948年,晶體管的發(fā)明給當時的電子工業(yè)界來帶來了前所未有的沖擊。而且,正是這個時候成為了今日電子時代的開端。之后以計算機為首,電子技術(shù)取得急速

2019-05-05 00:52:40

1.晶體管的結(jié)構(gòu)晶體管內(nèi)部由兩PN結(jié)構(gòu)成,其三個電極分別為集電極(用字母C或c表示),基極(用字母B或b表示)和發(fā)射極(用字母E或e表示)。如圖5-4所示,晶體管的兩個PN結(jié)分別稱為集電結(jié)(C、B極

2013-08-17 14:24:32

300V,一般可選用3DG182N、2SC2068、2SC2611、2SC2482等型號的晶體管。 3.行推動管的選用彩色電視機中使用的行推動管,應(yīng)選用中、大功率的高頻晶體管。其耗散功率應(yīng)大于或等于10

2012-01-28 11:27:38

的B和C對稱、和E極同樣是N型。也就是說,逆接C、E也同樣有晶體管的功效。即電流由E→C流動。3. 逆向晶體管有如下特點。hFE低(正向約10%以下)耐壓低 (7 to 8V 與VEBO一樣低)↑通用

2019-05-09 23:12:18

電子,雷達和微波應(yīng)用生產(chǎn)全系列AM晶體管。 這些AM晶體管最初由Microwave Semiconductor Corp.和S.T.制造。 ASI的AM晶體管覆蓋60 MHz至3.0 GHz的范圍,功率

2018-07-17 15:08:03

Finfet技術(shù)(3D晶體管)詳解

2012-08-19 10:46:17

一、引言PNP 晶體管是雙極結(jié)型晶體管(BJT)。PNP晶體管具有與NPN晶體管完全不同的結(jié)構(gòu)。在PNP晶體管結(jié)構(gòu)中,兩個PN結(jié)二極管相對于NPN晶體管反轉(zhuǎn),使得兩個P型摻雜半導(dǎo)體材料被一層薄薄的N

2023-02-03 09:44:48

晶體管(transistor)是一種固體半導(dǎo)體器件,可以用于檢波、整流、放大、開關(guān)、穩(wěn)壓、信號調(diào)制和許多其它功能

2010-08-13 11:36:51

multisim仿真中高頻晶體管BFG35能用哪個晶體管來代替,MFR151管子能用哪個來代替?或是誰有這兩個高頻管子的原件庫?求大神指教

2016-10-26 11:51:18

。這場戰(zhàn)役兩家大廠互有消長,首先是三星的14nm較臺積電的16nm搶先半年投入量產(chǎn),因兩家大廠的鰭式晶體管(FinFET)設(shè)計也確有雷同之處,后續(xù)又衍生了競業(yè)禁止官司訴訟等故事,無論如何,最終臺積電還是

2018-06-14 14:25:19

三星電子近日在國際學(xué)會“IEDM 2015”上就20nm工藝的DRAM開發(fā)發(fā)表了演講。演講中稱,三星此次試制出了20nm工藝的DRAM,并表示可以“采用同樣的方法,達到10nm工藝”。 國際電子器件

2015-12-14 13:45:01

提高了器件的性能。據(jù)IMEC的研究,叉片晶體管相比納米片晶體管可以實現(xiàn)約10%的性能提升。

叉片晶體管被認為是未來1nm及以下技術(shù)節(jié)點的有力候選架構(gòu)。它能夠?qū)⒓{米片晶體管的可微縮性進一步延伸,為半導(dǎo)體

2025-06-20 10:40:07

互補晶體管的匹配

2019-10-30 09:02:03

調(diào)制和振蕩器。晶體管可以獨立封裝,也可以封裝在非常小的區(qū)域內(nèi),容納1億個或更多晶體管集成電路的一部分。(英特爾 3D 晶體管技術(shù))嚴格來說,晶體管是指基于半導(dǎo)體材料的所有單一元件,包括由各種半導(dǎo)體材料

2023-02-03 09:36:05

晶體管通道完全閉合;二維過渡金屬二硫化物受損于其比透明導(dǎo)電氧化物還低的載流子遷移率。 在新加坡-麻省理工學(xué)院研究與技術(shù)聯(lián)盟,正在先行研發(fā)一種有前景的替代材料:GaN。從光學(xué)角度看,GaN的帶隙為

2020-11-27 16:30:52

達林頓晶體管是一對雙極晶體管,連接在一起,從低基極電流提供非常高的電流增益。輸入晶體管的發(fā)射極始終連接到輸出晶體管的基極;他們的收藏家被綁在一起。結(jié)果,輸入晶體管放大的電流被輸出晶體管進一步放大

2023-02-16 18:19:11

場效應(yīng)管的演變 鰭式場效應(yīng)晶體管的未來發(fā)展前景 FinFET在5nm之后將不再有用,因為它沒有足夠的靜電控制,需要晶體管的新架構(gòu)。然而,隨著技術(shù)節(jié)點的進步,一些公司可能會出于經(jīng)濟原因決定在同一節(jié)點上

2023-02-24 15:25:29

的寬度,也被稱為柵長。柵長越短,則可以在相同尺寸的硅片上集成更多的晶體管。目前,業(yè)內(nèi)最重要的代工企業(yè)臺積電、三星和GF(格羅方德),在半導(dǎo)體工藝的發(fā)展上越來越迅猛,10nm制程才剛剛應(yīng)用一年半,7n...

2021-07-29 07:19:33

請教:單結(jié)晶體管在什么位置,有人說是UJT,但好象用不了呀?

2013-09-26 16:55:49

各位高手,小弟正在學(xué)習單結(jié)晶體管,按照網(wǎng)上的電路圖做的關(guān)于單結(jié)晶體管的仿真,大多數(shù)都不成功,請問誰有成功的單結(jié)晶體管的仿真仿真啊,可以分享下嗎。

2016-03-04 09:15:06

晶體管開關(guān)對電子產(chǎn)品至關(guān)重要。了解晶體管開關(guān),從其工作區(qū)域到更高級的特性和配置。 晶體管開關(guān)對于低直流開/關(guān)開關(guān)的電子設(shè)備至關(guān)重要,其中晶體管在其截止或飽和狀態(tài)下工作。一些電子設(shè)備(如 LED

2023-02-20 16:35:09

什么是微波功率晶體管?如何提高微波功率晶體管可靠性?

2021-04-06 09:46:57

~3.3nf。當Nb上端產(chǎn)生一個正的驅(qū)動電壓時,由于電容兩端電壓不能突變,上電瞬間電容如同短路,因此可認為為VT1提供了很大的正向基極電流,使晶體管迅速導(dǎo)通。之后,電容CB被充電至激勵電壓的峰值而進入穩(wěn)態(tài)

2020-11-26 17:28:49

來至網(wǎng)友的提問:如何選擇分立晶體管?

2023-11-24 08:16:54

晶體管依照用途大致分為高頻與低頻,它們在型號上的大致區(qū)別是什么?例如《晶體管電路設(shè)計》中列舉的:高頻(2SA****,2SC*****)、低頻(2SB****,2SD****)。現(xiàn)在產(chǎn)品設(shè)計中最常用的型號是哪些?

2017-10-11 23:53:40

bandgap中晶體管的熱噪聲比較大,通過什么手段能解決?

2021-06-24 07:29:25

判斷為不合格。正確觀點A:首先為了啟動數(shù)字晶體管,加入足夠的輸入電壓Vin(如10V)B:漸漸降低電壓,到規(guī)格書規(guī)定的3V時停止。因仍保持ON狀態(tài),故該產(chǎn)品為合格。C:如果繼續(xù)降低基極電壓,不能完全保持

2019-04-09 21:49:36

:首先為了啟動數(shù)字晶體管,加入足夠的輸入電壓Vin(如10V)B:漸漸降低電壓,到規(guī)格書規(guī)定的3V時停止。因仍保持ON狀態(tài),故該產(chǎn)品為合格。C:如果繼續(xù)降低基極電壓,不能完全保持ON狀態(tài),而向OFF狀態(tài)

2019-04-22 05:39:52

10月7日,沉寂已久的計算技術(shù)界迎來了一個大新聞。勞倫斯伯克利國家實驗室的一個團隊打破了物理極限,將現(xiàn)有最精尖的晶體管制程從14nm縮減到了1nm。晶體管的制程大小一直是計算技術(shù)進步的硬指標。晶體管

2016-10-08 09:25:15

晶體管的代表形狀晶體管分類圖:按照該分類,掌握其種類1. 按結(jié)構(gòu)分類根據(jù)工作原理不同分類,分為雙極晶體管和單極晶體管。雙極晶體管雙是指Bi(2個)、極是指Polar(極性)。雙極晶體管,即流經(jīng)構(gòu)成

2019-05-05 01:31:57

效率和功率密度。GaN功率晶體管作為一種成熟的晶體管技術(shù)在市場上確立了自己的地位,但在軟開關(guān)應(yīng)用中通常不被考慮使用。雖然在硬開關(guān)應(yīng)用中使用GaN可以顯著提高效率,但軟開關(guān)轉(zhuǎn)換器(如LLC)對效率和頻率

2023-02-27 09:37:29

是最主要的。NVIDIA的Huang先生的觀點可能是正確的:隨著成本的大幅攀升,對于同樣數(shù)量的晶體管,20 nm一直要比28 nm昂貴得多。對于采用了大量非線性電路的SoC,例如,RF或者其他模擬晶體管

2014-09-01 17:26:49

近日,SIA發(fā)了個聳人聽聞的新聞,說intel放棄了10nm工藝的研發(fā),當然這肯定是假消息就是了,今天intel也出面辟謠。不過相信很多人也會覺得奇怪,那邊TSMC 7...

2021-07-26 08:10:47

大家都在談?wù)揊inFET——可以說,這是MOSFET自1960年商用化以來晶體管最大的變革。幾乎每個人——除了仍然熱心于全耗盡絕緣體硅薄膜(FDSOI)的人,都認為20 nm節(jié)點以后,F(xiàn)inFET將成為SoC的未來。但是對于要使用這些SoC的系統(tǒng)開發(fā)人員而言,其未來會怎樣呢?

2019-09-27 06:59:21

來至網(wǎng)友的提問:如何選擇分立晶體管?

2018-12-12 09:07:55

這個達林頓晶體管廠家是哪家

2022-05-30 16:36:56

本帖最后由 eehome 于 2013-1-5 10:10 編輯

高清圖詳解英特爾最新22nm 3D晶體管

2012-08-05 21:48:28

高清圖詳解英特爾最新22nm_3D晶體管

2012-08-02 23:58:43

晶體管出現(xiàn)的意義

晶體管的出現(xiàn),是電子技術(shù)之樹上綻開的一朵絢麗多彩的奇葩。 同電子管相比,晶體管具有諸多優(yōu)越性: ①晶體管的構(gòu)

2009-11-05 10:46:47 3960

3960 晶體管分類

按半導(dǎo)體材料和極性分類 按晶體管使用的半導(dǎo)體材料可分為硅材料晶體管和鍺材料晶體管。按晶體

2009-11-05 10:48:53 4989

4989 愛爾蘭科學(xué)家開發(fā)出業(yè)內(nèi)首款非節(jié)型晶體管

愛爾蘭丁鐸爾國家研究院的科學(xué)家最近宣稱他們成功制出了業(yè)內(nèi)首款非節(jié)型晶體管,并稱此項發(fā)明對10nm級別制程意義重大

2010-02-24 10:08:25 839

839 PNP晶體管,PNP晶體管是什么意思

PNP晶體管是另一種類型晶體管.它的結(jié)構(gòu)如圖1所示。

2010-03-05 11:18:05 6814

6814 雙極晶體管,雙極晶體管是什么意思

雙極晶體管

雙極型晶體管內(nèi)部電流由兩種載流子形成,它是利用電流來控制。場效應(yīng)管是電壓控制器

2010-03-05 11:48:46 6586

6586 電力晶體管(GTR),電力晶體管(GTR)是什么意思

電力晶體

電力晶體管管按英文GiantTransistor直譯為巨型晶體

2010-03-05 13:32:30 14825

14825 CMOS晶體管,CMOS晶體管是什么意思

金屬-氧化物-半導(dǎo)體(Metal-Oxide-Semiconductor)結(jié)構(gòu)的晶體管簡稱MOS晶體管,有P型MOS管和N型MOS管之分

2010-03-05 15:22:51 4129

4129 晶體管耗散功率,晶體管耗散功率是什么意思

晶體管耗散功率也稱集電極最大允許耗散功率PCM,是指晶體管參數(shù)變化不超過規(guī)定允許值時的最大

2010-03-05 17:34:10 8979

8979 22nm以后的晶體管技術(shù)領(lǐng)域,靠現(xiàn)行Bulk MOSFET的微細化會越來越困難的,為此,人們關(guān)注的是平面型FD-SOI(完全空乏型SOI)元件與基于立體通道的FinFET。由于這些技術(shù)都不需要向通

2010-06-23 08:01:42 888

888 在今天的IEEE國際電子設(shè)備會議上,IBM的科學(xué)家們展示了一系列突破性的科研成果,IBM拿出了全球第一個通道長度(柵極長度)不足10nm的碳納米晶體管,代表了未來計算技術(shù)的重大突破

2011-12-08 09:23:55 1612

1612

《晶體管精華集錦》技術(shù)專題主要介紹了晶體管新品資訊、晶體管原理、晶體管手冊、晶體管電路圖、晶體管電路設(shè)計、晶體管應(yīng)用(主要含晶體管收音機、晶體管測試儀)以及常見的晶體管(如:場效應(yīng)晶體管,mos晶體管,絕緣柵雙極晶體管等)。本專題內(nèi)容豐富、包羅萬象,希望對各位有所幫助!

2012-08-03 09:12:48

本文通過高清圖詳解Intel最新22nm 3D 晶體管 。業(yè)界一直傳說3D三柵級晶體管技術(shù)將會用于下下代14nm的半導(dǎo)體制造,沒想到英特爾竟提前將之用于22nm工藝,并且于上周四向全世界表示將在

2012-08-03 17:09:18 0

0 本文核心議題: 通過本文介紹,我們將對Intel 22nm 3D三柵極晶體管技術(shù)有著詳細的了解。業(yè)界一直傳說3D三柵級晶體管技術(shù)將會用于下下代14nm的半導(dǎo)體制造,沒想到英特爾竟提前將之用

2012-08-15 10:45:27 8565

8565

近日消息,英特爾計劃將“3D晶體管”工藝應(yīng)用到SoC移動芯片上,以獲得產(chǎn)品性能飛躍性提升,但對于“3D晶體管”技術(shù)是否適用于SoC芯片的制造,參與舊金山國際電子產(chǎn)品大會的專家們

2012-12-11 09:05:45 1434

1434 ? Analog FastSPICE? 電路驗證平臺已完成了電路級和器件級認證,Olympus-SoC? 數(shù)字設(shè)計平臺正在進行提升,以幫助設(shè)計工程師利用 TSMC 10nm FinFET 技術(shù)更有效地驗證和優(yōu)化其設(shè)計。10nm V1.0 工藝的認證預(yù)計在 2015 年第 4 季度完成。

2015-09-21 15:37:10 1664

1664 為什么說7nm是物理極限?縮短晶體管柵極的長度可以使CPU集成更多的晶體管或者有效減少晶體管的面積和功耗,并削減CPU的硅片成本。不過這種做法也會使電子移動的距離縮短,容易導(dǎo)致晶體管內(nèi)部電子自發(fā)通過

2016-10-10 16:49:39 6418

6418 雖然摩爾定律即將走向終結(jié),但半導(dǎo)體制程工藝推進的腳步卻一直沒有停下過。臺積電和三星作為ARM芯片代工陣營的領(lǐng)軍企業(yè),雙方你追我趕大打制程戰(zhàn),已將制程工藝推進至10nm,而高通聯(lián)發(fā)科等我們所熟知的IC

2017-01-11 10:49:11 4294

4294

英特爾此前已經(jīng)談?wù)撨^多次 10 納米的 Cannon Lake 芯片了,超級10nm領(lǐng)先一切對手,性能升25%功耗降45%,英特爾已經(jīng)有能力在1平方毫米中塞下1億個晶體管,絕對是行業(yè)歷史上史無前例的。

2017-04-05 18:01:14 2446

2446 作為科技行業(yè)著名的“牙膏廠”,英特爾一直走在所有廠商前面。因為它的10nm制程已經(jīng)跳票三年之久,每當一款新的處理器發(fā)布,眾人翹首以待10nm的到來,可英特爾還是給用戶潑冷水,繼續(xù)跳票10nm工藝。

2018-06-15 15:53:00 6091

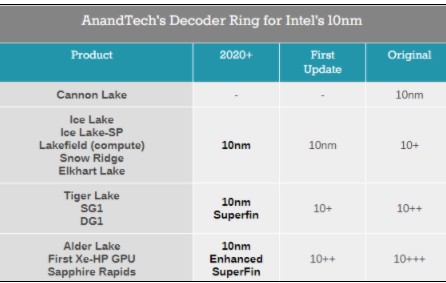

6091 由于晶體管制造的復(fù)雜性,每代晶體管制程針對不同用途的制造技術(shù)版本,不同廠商的代次間統(tǒng)計算法也完全不同,單純用代次來比較并不準確。根據(jù)目前業(yè)界常用晶體管密度來衡量制程水平,英特爾最新10nm制程的晶體管密度堪比三星 EUV版本7nm制程。

2018-07-10 16:31:00 4668

4668

Cannonlake架構(gòu)的Core i3-8121處理器,通過分析英特爾的10nm工藝晶體管密度達到了100MTr/mm2,是14nm節(jié)點的2.7倍,而且英特爾首次使用了貴金屬釕。

2018-06-14 11:08:00 6886

6886 無疑這收獲了業(yè)界潮水般的質(zhì)疑,為何其10nm一直難以出師?有分析稱,10nm工藝之難產(chǎn)的一個關(guān)鍵是最初指標定的太高。相比14nm工藝,10nm工藝的晶體管密度是前者的2.7倍,也就是2.7x的縮放

2018-12-18 10:37:33 3103

3103 今天有多家媒體報道了中國科研人員實現(xiàn)了3nm半導(dǎo)體工藝的突破性進展,香港《南華早報》稱中科院微電子所團隊的殷華湘等人研究出了3nm晶體管,相當于人類DNA鏈條寬度,這種晶體管解決了玻爾茲曼熱力學(xué)的限制。

2019-05-29 16:48:09 5127

5127 CPU使用數(shù)十億個微型晶體管,電子門打開和關(guān)閉以執(zhí)行計算。晶體管越小,所需的功率就會越小。7nm和10nm是這些晶體管尺寸的測量尺寸。nm是納米和微小長度的縮寫,以此來判斷特定CPU有多強大的有用指標。

2019-08-18 10:02:17 7884

7884 目前全球最先進的半導(dǎo)體工藝已經(jīng)進入 7nm,下一步還要進入 5nm、3nm 節(jié)點,制造難度越來越大,其中晶體管結(jié)構(gòu)的限制至關(guān)重要,未來的工藝需要新型晶體管。

2019-12-10 15:40:49 7723

7723 本文首先闡述了晶體管的概念,其次介紹了晶體管的優(yōu)越性,最后闡述了晶體管的控制方式。

2020-03-14 09:47:12 13941

13941 Mate 40系列來了,麒麟9000也終于來了!這是全球第一顆、也是唯一一顆5nm工藝制造的5G SoC,集成多達153億個晶體管,首次突破150億大關(guān),是目前晶體管最多、功能最完整的5G SoC。

2020-10-23 10:37:18 5336

5336 Intel正在各個領(lǐng)域?qū)崿F(xiàn)從14nm向10nm的過渡:輕薄本上代還是14/10nm混合,現(xiàn)在已經(jīng)完全是10nm;游戲本、服務(wù)器馬上就都會首次嘗鮮10nm;桌面則要等到明年底的12代最終實現(xiàn)交接。

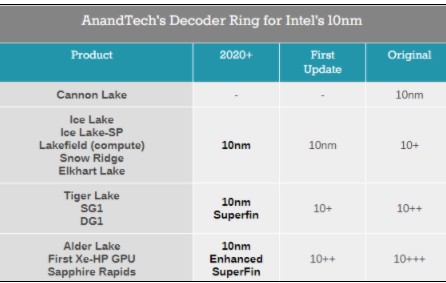

2020-12-07 10:00:07 2568

2568 隨著Tiger Lake處理器的量產(chǎn),Intel的10nm工藝已經(jīng)解決了產(chǎn)能、性能等問題,現(xiàn)在使用的是10nm SuperFin(以下簡稱10nm SF)工藝,下半年則會有更新的增強版10nm SF工藝,12代酷睿會首發(fā)。

2021-01-14 09:48:28 3786

3786

現(xiàn)在的芯片技術(shù)越來越先進,人們常常能夠聽到某某公司又研發(fā)出5nm、4nm芯片的消息,而目前全球所研發(fā)出的最先進的芯片是IBM公司的2nm芯片,我們都知道芯片內(nèi)部有很多晶體管,那么2nm芯片的晶體管

2022-07-04 09:15:36 5743

5743 數(shù)字晶體管因集電極電流和連接至基極的電阻的不同而分為不同類型。數(shù)字晶體管的選擇方法和確定使用普通晶體管作為開關(guān)時連接到基極的電阻的方法相同。

2023-05-29 16:40:45 893

893 華為發(fā)布首款5nm 5G SoC,集成153億晶體管? 在當今的數(shù)字時代,5G成為了一種越來越重要的通信技術(shù),它能夠大幅提升傳輸速度和低延時,以實現(xiàn)更高的數(shù)據(jù)傳輸質(zhì)量。而華為公司最近發(fā)布了自家

2023-09-01 16:47:35 9729

9729 上次我的文章解釋了所謂的7nm不是真的7nm,是在實際線寬無法大幅縮小的前提下,通過改變晶體管結(jié)構(gòu)的方式縮小晶體管實際尺寸來達到等效線寬的效果那么新的問題來了:從平面晶體管結(jié)構(gòu)(Planar)到立體

2023-12-19 16:29:01 1396

1396

NMOS晶體管和PMOS晶體管是兩種常見的金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)類型,它們在多個方面存在顯著的差異。以下將從結(jié)構(gòu)、工作原理、性能特點、應(yīng)用場景等方面詳細闡述NMOS晶體管和PMOS晶體管的區(qū)別。

2024-09-13 14:10:00 9544

9544 現(xiàn)有的晶體管都是基于 PN 結(jié)或肖特基勢壘結(jié)而構(gòu)建的。在未來的幾年里,隨著CMOS制造技術(shù)的進步,器件的溝道長度將小于 10nm。在這么短的距離內(nèi),為使器件能夠工作,將采用非常高的摻雜濃度梯度。

2025-06-18 11:43:22 1011

1011

電子發(fā)燒友App

電子發(fā)燒友App

評論