Altium中的信號完整性分析包括檢查信號上升時間,下降時間,提供終端方案和進行串擾分析的能力。您還可以定義模型并設置規則和約束以及信號完整性分析相關的其它設置。一旦確認了串擾問題,就可以根據需要修改相同層或相鄰層的布線路徑。

2020-08-25 15:50:00 10700

10700

歡迎來到 “掌握 PCB 設計中的 EMI 控制” 系列的第六篇文章。本文將探討串擾如何影響信號完整性和 EMI,并討論在設計中解決這一問題的具體措施。

2025-08-25 11:06:45 9572

9572

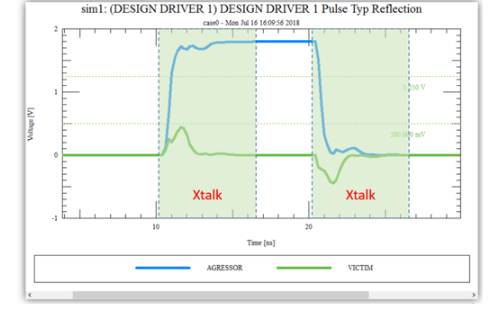

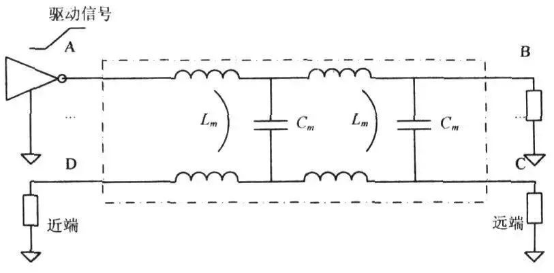

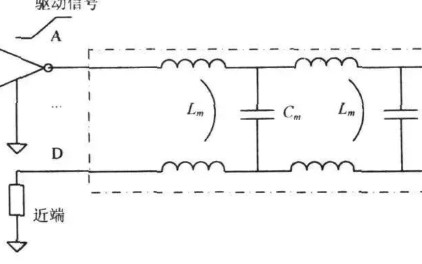

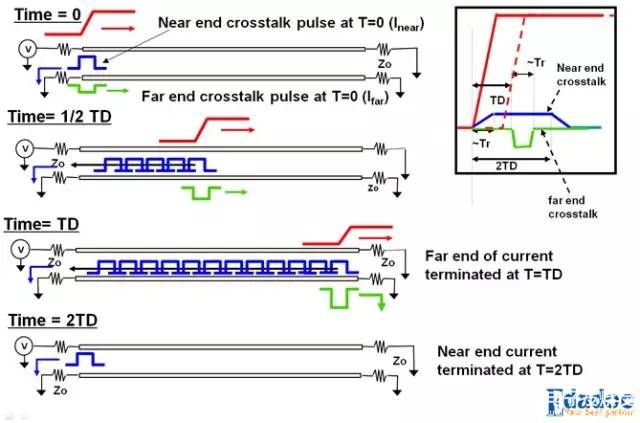

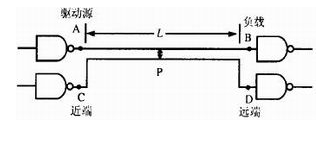

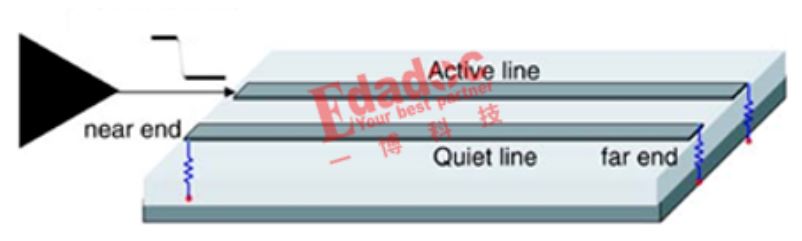

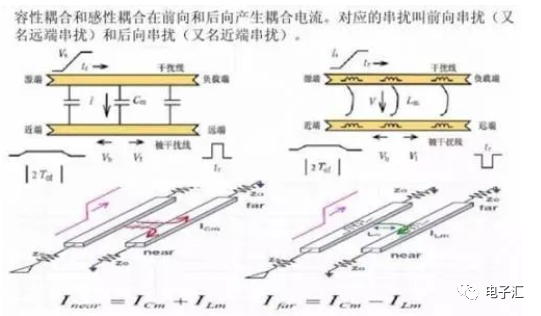

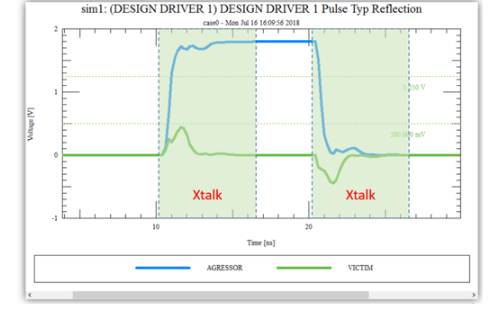

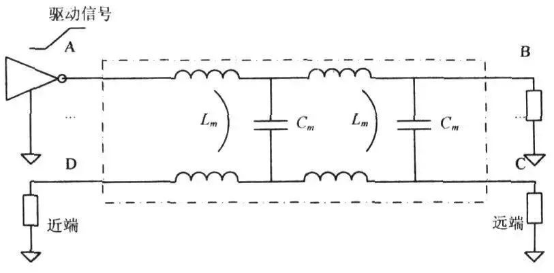

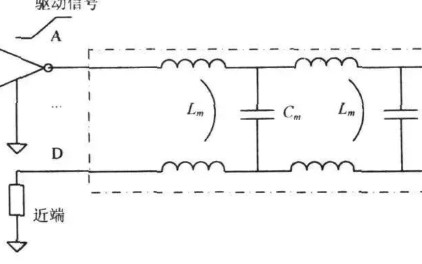

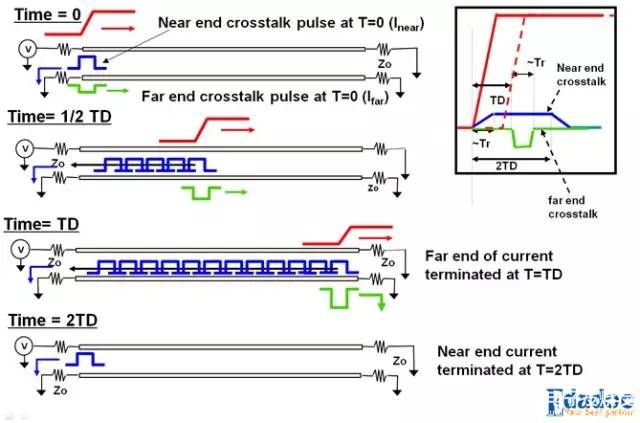

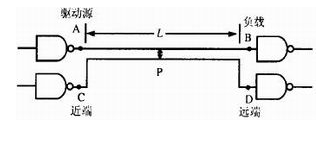

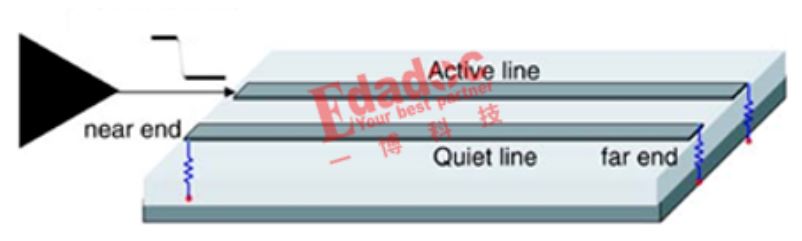

靜態網絡靠近干擾源一端的串擾稱為近端串擾(也稱后向串擾),而遠離干擾源一端的串擾稱為遠端串擾(或稱前向串擾)。

2021-01-24 16:13:00 8677

8677

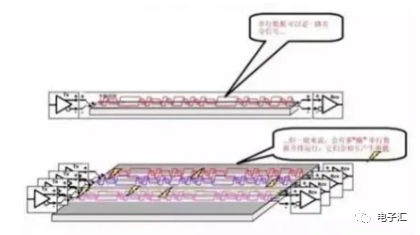

,EE/Layout人員就能于設計中同步進行SI等級的串擾分析,預先消除常見的信號串擾問題,并達到更為精確的結果,使設計效率提升,不良機率減少。

2020-11-12 17:33:24 4101

4101

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。

2022-08-22 10:45:08 4444

4444

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。

2022-08-29 09:38:57 2560

2560

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。 串擾(crosstalk

2022-09-05 18:55:08 3020

3020

因此了解串擾問 題產生的機理并掌握解決串擾的設計方法,對于工程師來說是相當重要的,如果處理不好可能會嚴重影響整個電路的效果。

2022-09-28 09:41:25 2687

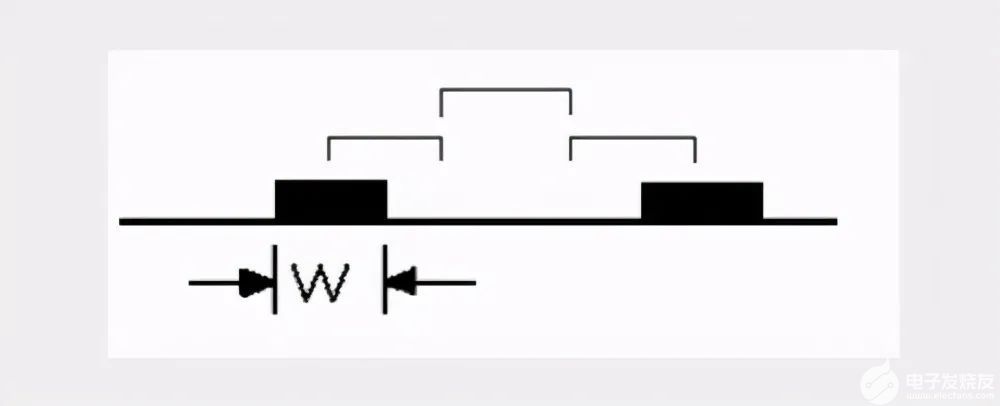

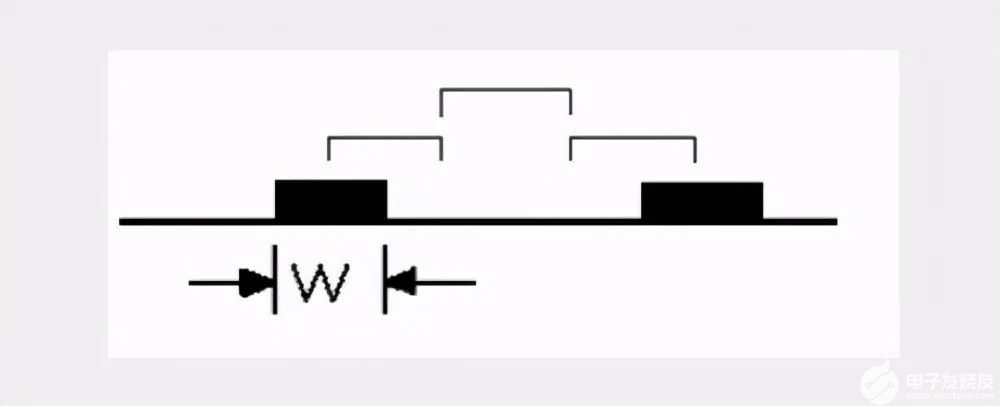

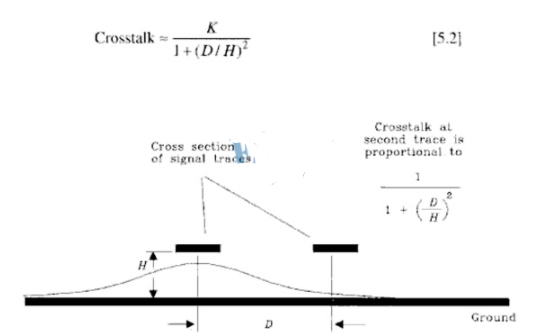

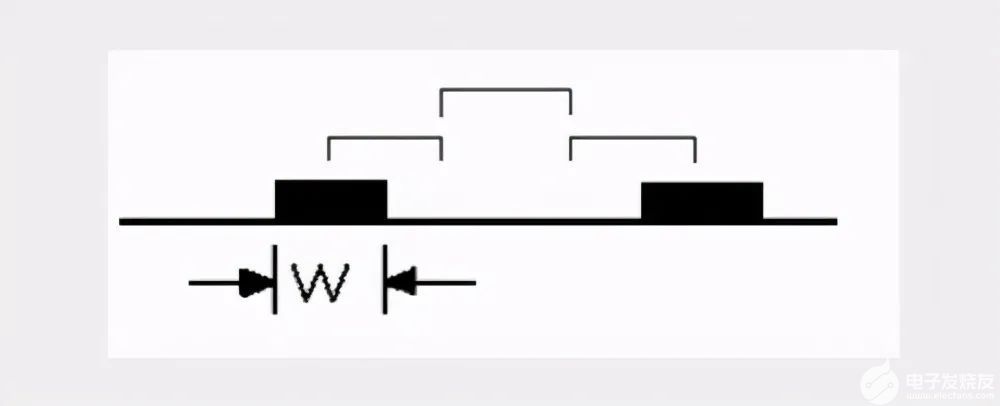

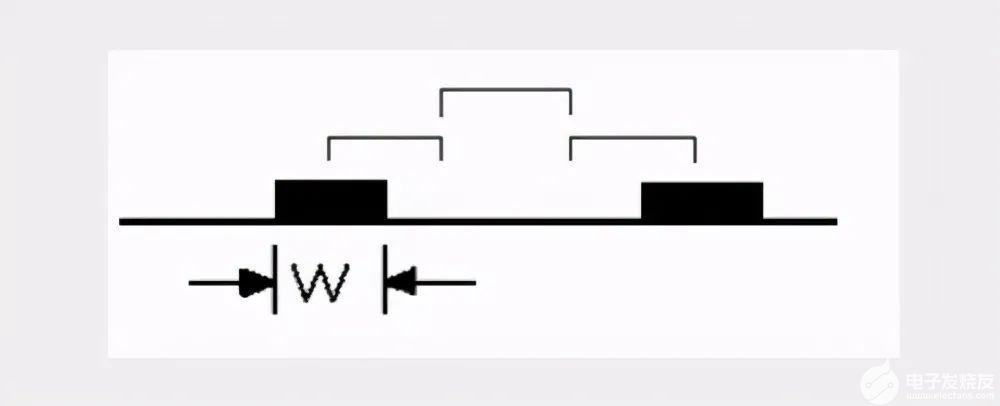

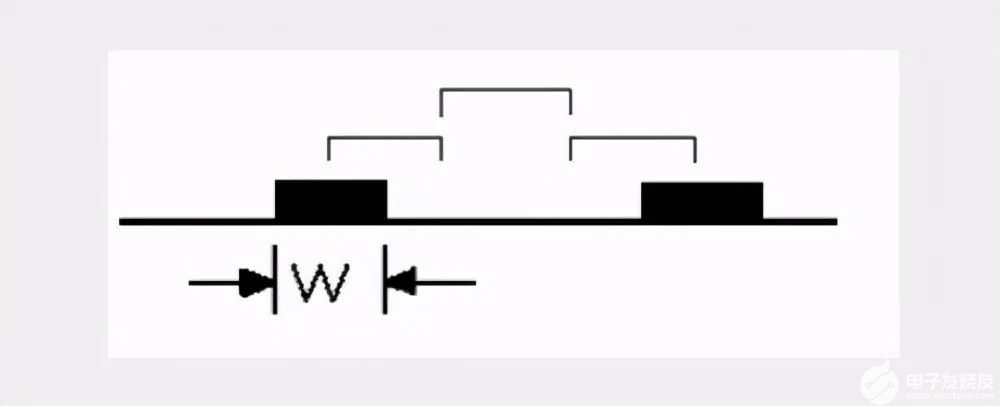

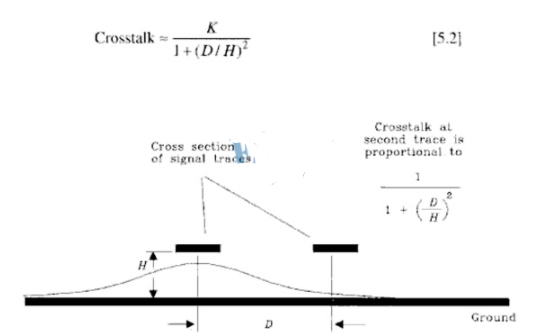

2687 我們經常聽說PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾,這就是3W原則,信號線之間的干擾被稱為串擾,串擾是怎么形成的呢?

2023-04-18 11:06:22 2146

2146

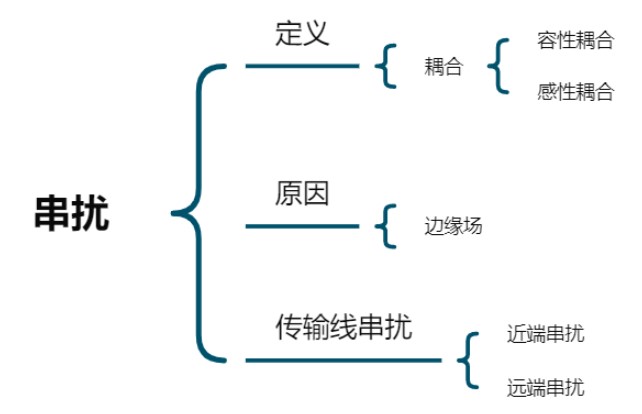

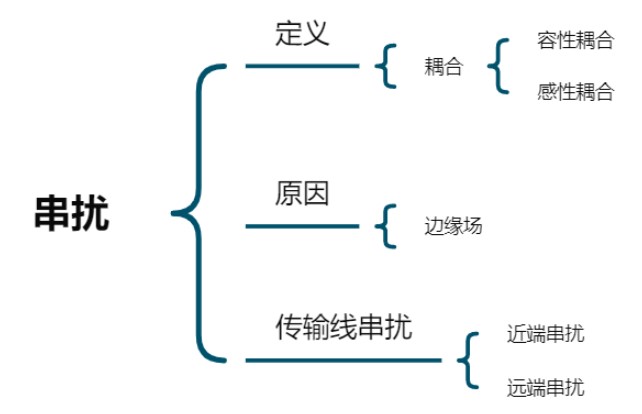

通常以斷斷續續或不易重現的方式發生,對于工程師來說, 盡早解決 PCB 上串擾發生的所有原因非常重要。 串擾會對時鐘信號、周期和控制信號、數據傳輸線和 I/O 產生不良影響。通常來講, 串擾是無法完全消除的,只能盡量減少串擾。 02 . 串擾的機制 ? 1、耦合

2023-05-23 09:25:59 8732

8732

串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法。

2023-06-13 10:41:52 2372

2372

設計工程師不可避免的問題。 ? 串擾是指有害信號從一個網絡轉移到另一個網絡,它是信號完整性問題中一個重要問題,在數字設計中普遍存在,有可能出現在芯片、PCB板、連接器、芯片封裝和連接器電纜等器件上。 如果串擾超過一定的限度就會引

2023-09-15 15:58:33 2579

2579

串擾是四類信號完整性問題之一,指的是有害信號從一個線網傳遞到相鄰線網。任何一對線網之間都存在串擾。

2023-09-25 11:29:07 3292

3292

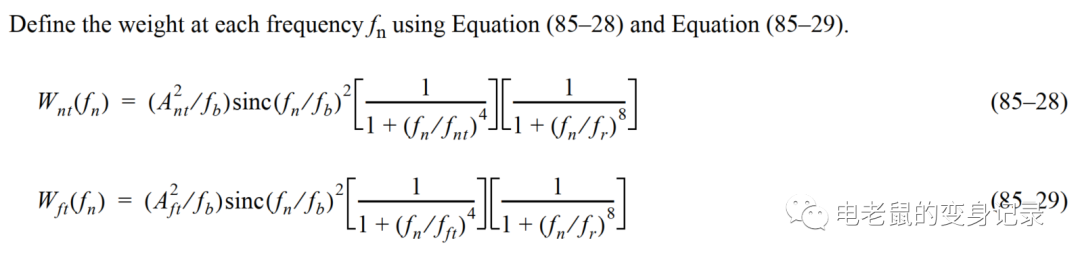

講到串擾,基礎的串擾知識比如串擾是由電場耦合和磁場耦合的共同結果啊,從串擾影響的方向來分有FEXT和NEXT這些小P就都不說了。當小P在學習一篇PCIe 5.0連接器一致性的paper里出現了ICN的字樣。

2023-10-25 14:43:22 7932

7932

信號串擾(Crosstalk)是指在信號傳輸過程中,一條信號線上的信號對相鄰信號線產生的干擾,這種干擾是由于電磁場耦合或直接電容、電感耦合引起的。根據耦合類型和位置的不同,信號串擾主要分為以下幾類

2024-09-12 08:08:34 4569

4569

串擾是信號完整性中最基本的現象之一,在板上走線密度很高時串擾的影響尤其嚴重。我們知道,線性無緣系統滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產生畸變

2019-05-31 06:03:14

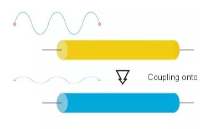

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進行介紹。串擾串擾是由于線路之間的耦合引發的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達

2018-11-29 14:29:12

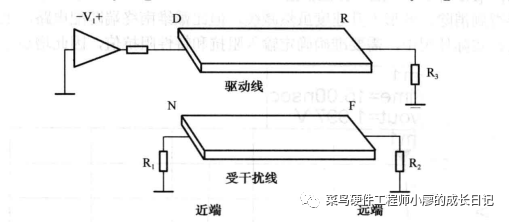

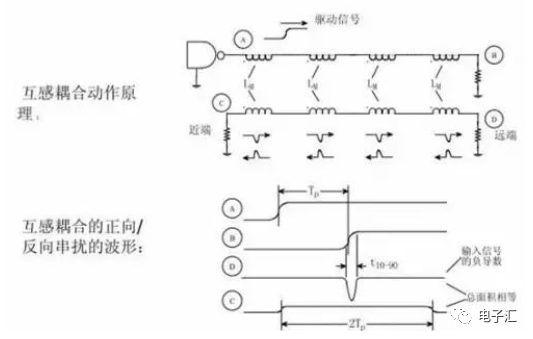

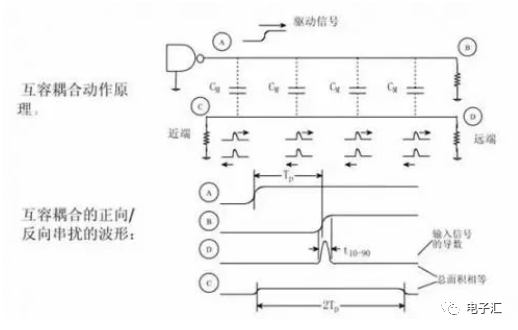

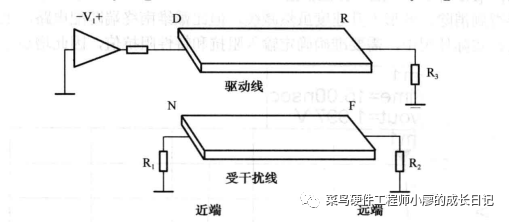

所謂串擾,是指有害信號從一個傳輸線耦合到毗鄰傳輸線的現象,噪聲源(攻擊信號)所在的信號網絡稱為動態線,***擾的信號網絡稱為靜態線。串擾產生的過程,從電路的角度分析,是由相鄰傳輸線之間的電場(容性)耦合和磁場(感性)耦合引起,需要注意的是串擾不僅僅存在于信號路徑,還與返回路徑密切相關。

2019-08-02 08:28:35

串擾信號產生的機理是什么串擾的幾個重要特性分析線間距P與兩線平行長度L對串擾大小的影響如何將串擾控制在可以容忍的范圍

2021-04-27 06:07:54

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數字信號處理之后再畫到顯示屏上顯示實時波形。

調試發現顯示的信號有串擾,表現為某一路信號懸空之后,相鄰的那一路信號

2023-12-18 08:27:39

是ADI的SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數字信號處理之后再畫到顯示屏上顯示實時波形。 調試發現顯示的信號有串擾,表現為某一路信號懸空之后,相鄰的那一路信號上

2018-09-06 14:32:00

,ADC是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數字信號處理之后再畫到顯示屏上顯示實時波形。

調試發現顯示的信號有串擾,表現為某一路信號懸空之后,相鄰的那一路信號上就會出現噪聲。將采樣的時間延長也無法消除串擾。

想請教一下各路專家,造成串擾的原因和如何消除串擾,謝謝。

2025-01-07 06:15:34

作者:一博科技SI工程師陳德恒摘要:隨著電子設計領域的高速發展,產品越來越小,速率越來越高,信號完整性越來越成為一個硬件工程師需要考慮的問題。串擾,阻抗匹配等詞匯也成為了硬件工程師的口頭禪。電路

2014-10-21 09:53:31

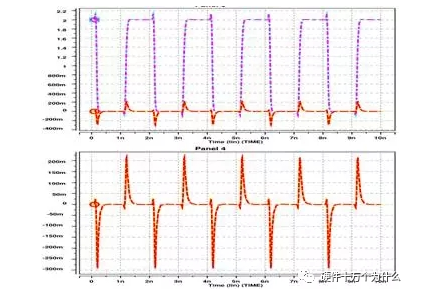

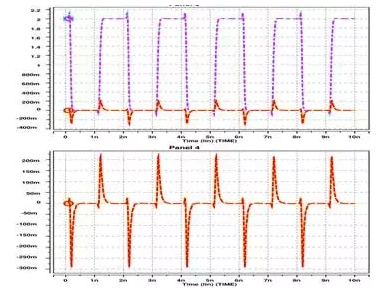

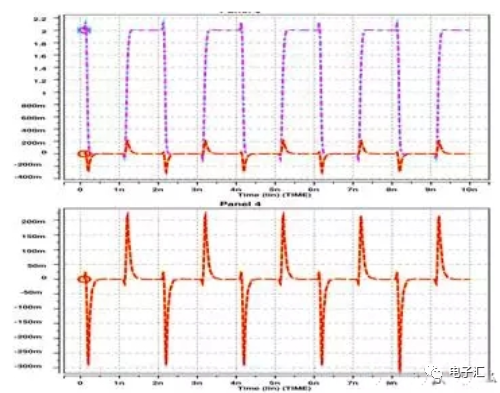

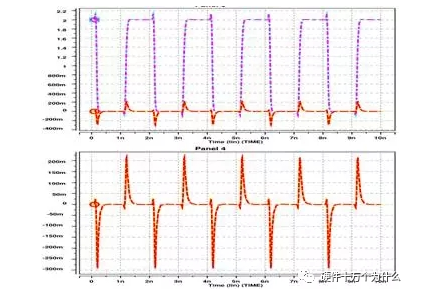

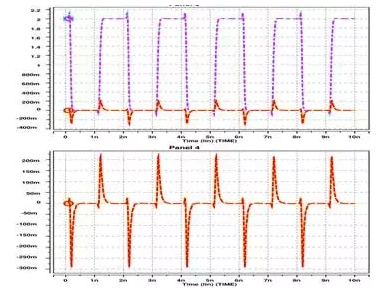

4.2,與兩側間距同為8mil。 圖5 圖6圖6中四個電路分別為微帶線的近端串擾,微帶線的遠端串擾,帶狀線的近端串擾,帶狀線的遠端串擾。紅色為攻擊線上信號,藍色為靜態線串擾。我們將線長定為2000mil

2014-10-21 09:52:58

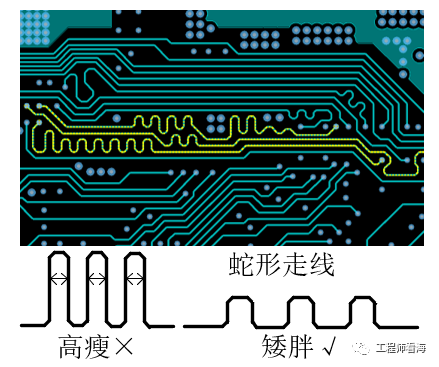

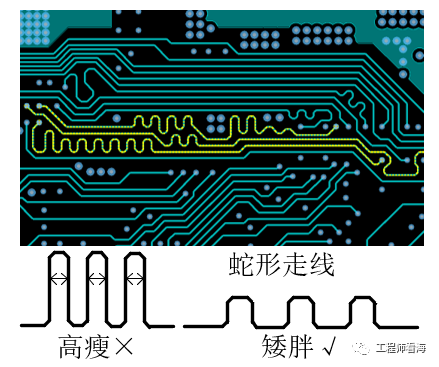

了各自的見解,比如串擾,繞線,過孔,跨分割等等。本期我們就以不同模態下的串擾對信號時延的影響繼續通過理論分析和仿真驗證的方式跟大家一起進行探討。在開始仿真之前我們先簡單的了解一下什么是串擾以及串擾

2023-01-10 14:13:01

繼上一篇“差模(常模)噪聲與共模噪聲”之后,本文將對“串擾”進行介紹。串擾串擾是由于線路之間的耦合引發的信號和噪聲等的傳播,也稱為“串音干擾”。特別是“串音”在模擬通訊時代是字如其意、一目了然的表達

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是有擾射頻?怎么消除有擾射頻?

2021-05-25 06:51:47

相互作用時就會產生。在數字電路系統中,串擾現象相當普遍,串擾可以發生在芯片內核、芯片的封裝、PCB板上、接插件上、以及連接線纜上,只要有臨近的銅互連鏈路,就存在信號間的電磁場相互作用,從而產生串擾現象

2016-10-10 18:00:41

靜態存儲器SRAM是一款不需要刷新電路即能保存它內部存儲數據的存儲器。在SRAM 存儲陣列的設計中,經常會出現串擾問題發生。那么要如何減小如何減小SRAM讀寫操作時的串擾,以及提高SRAM的可靠性呢

2020-05-20 15:24:34

在嵌入式系統硬件設計中,串擾是硬件工程師必須面對的問題。特別是在高速數字電路中,由于信號沿時間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設計者必須了解串擾產生的原理,并且在設計時應用恰當的方法,使串擾產生的負面影響降到最小。

2019-11-05 08:07:57

在PCB電路設計中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設計最常用的軟件等問題,本文我們講一下關于怎么解決PCB設計中消除串擾的問題,快跟隨小編一起趕緊學習下。 串擾是指在一根

2020-11-02 09:19:31

是SAR型 18位單通道全差分輸入的ADC。ADC的后端是MCU,MCU將數字信號處理之后再畫到顯示屏上顯示實時波形。 調試發現顯示的信號有串擾,表現為某一路信號懸空之后,相鄰的那一路信號上就會出現噪聲。將采樣的時間延長也無法消除串擾。想請教一下各路專家,造成串擾的原因和如何消除串擾,謝謝。

2019-05-14 14:17:00

高頻數字信號串擾的產生及變化趨勢串擾導致的影響是什么怎么解決高速高密度電路設計中的串擾問題?

2021-04-27 06:13:27

高速電路信號完整性分析與設計—串擾串擾是由電磁耦合引起的,布線距離過近,導致彼此的電磁場相互影響串擾只發生在電磁場變換的情況下(信號的上升沿與下降沿)[此貼子已經被作者于2009-9-12 10:32:03編輯過]

2009-09-12 10:31:08

高速PCB設計中的信號完整性概念以及破壞信號完整性的原因高速電路設計中反射和串擾的形成原因

2021-04-27 06:57:21

高速數字設計領域里,信號完整性已經成了一個關鍵的問題,給設計工程師帶來越來越嚴峻的考驗。信號完整性問題主要為反射、串擾、延遲、振鈴和同步開關噪聲等。本文基于高速電路設計的信號完整性基本理論,通過近端

2010-05-13 09:10:07

高速電路信號完整性分析與設計—串擾串擾是由電磁耦合引起的,布線距離過近,導致彼此的電磁場相互影響串擾只發生在電磁場變換的情況下(信號的上升沿與下降沿)

2009-10-06 11:10:15 0

0 該文研究了銅互連線中的多余物缺陷對兩根相鄰的互連線間信號的串擾,提出了互連線之間的多余物缺陷和互連線之間的互容、互感模型,用于定量的計算缺陷對串擾的影響。提出

2010-02-09 15:03:50 6

6 什么是路間串擾/幅頻特性/隨機信噪比

路間串擾 路間串擾:多路信號在同一設備中,由于空間的輻射與電源的波動

2010-03-26 11:49:40 1504

1504 串擾是 高速電路板 設計中干擾信號完整性的主要噪聲之一;為有效地抑制串擾噪聲,保證系統設計的功能正確,有必要分析串擾問題。針對實際PCB中互連線拓撲和串擾的特點,構

2011-06-22 15:58:54 0

0 通過端接電路在抑制攻擊線上反射的同時,減小了受害線上信號的串擾,從而使信號在兩條耦合線上的傳輸質量得到改善。最后進行了多組數據的串擾比較研究,分析了串擾減小的原因。

2011-12-12 14:31:21 28

28 串擾是不同傳輸線之間的能量耦合。當不同結構的電磁場相互作用時,就會發生串擾。在數字設計中,串擾現象是非常普遍的。串擾可能出現在芯片、PCB板、連接器、芯片封裝和連接器

2012-05-28 09:09:38 2951

2951 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號沿

2017-11-29 14:13:29 0

0 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號沿

2018-01-26 11:03:13 6105

6105

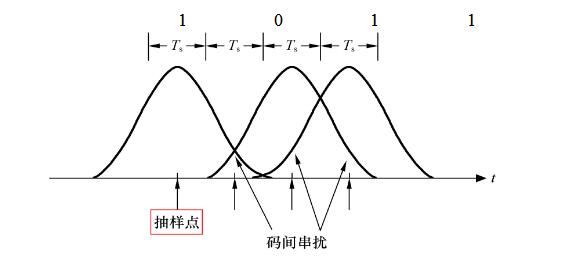

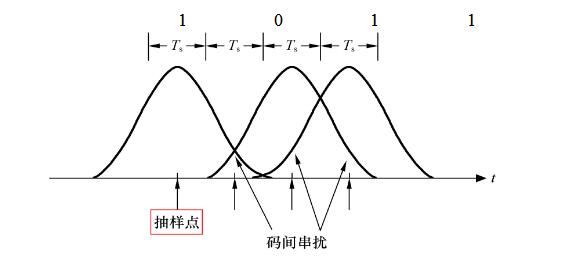

所謂碼間串擾,就是數字基帶信號通過基帶傳輸系統時,由于系統(主要是信道)傳輸特性不理想,或者由于信道中加性噪聲的影響,使收端脈沖展寬,延伸到鄰近碼元中去,從而造成對鄰近碼元的干擾,我們將這種現象稱為碼間串擾。

2018-04-16 14:25:39 47082

47082

們就需要弄清楚近端串擾與遠端串擾了。攻擊信號的幅值影響著串擾的大小;減小串擾的途徑就是減小信號之間的耦合,增加信號與其回流平面之間的耦合。

2018-10-27 09:25:52 16189

16189

信號頻率變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾在高速PCB設計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發,導致系統無法正常工作。設計者必須了解串擾產生的機理,并且在設計中應用恰當的方法,使串擾產生的負面影響最小化。

2019-05-29 14:09:48 1271

1271

串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法:

2019-08-14 11:50:55 20421

20421 串擾是信號完整性中最基本的現象之一,在板上走線密度很高時串擾的影響尤其嚴重。我們知道,線性無緣系統滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產生畸變。

2019-09-18 15:10:37 15882

15882

耦合電感電容產生的前向串擾和反向串擾同時存在,并且大小幾乎相等,這樣,在受害網絡上的前向串擾信號由于極性相反,相互抵消,反向串擾極性相同,疊加增強。串擾分析的模式通常包括默認模式,三態模式和最壞情況模式分析。

2019-09-19 14:39:54 1448

1448 串擾在電路板設計中無可避免,如何減少串擾就變得尤其重要。在前面的一些文章中給大家介紹了很多減少串擾和仿真串擾的方法。

2020-03-07 13:30:00 4390

4390 串擾是信號完整性中最基本的現象之一,在板上走線密度很高時串擾的影響尤其嚴重。我們知道,線性無緣系統滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產生畸變。

2020-11-12 10:39:00 2

2 高速PCB設計中,信號之間由于電磁場的相互耦合而產生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可能引發電路誤動作從而導致系統無法正常工作,解決PCB串擾問題可以從以下幾個方面考慮。

2020-07-19 09:52:05 2820

2820 ,這些技術可以回答如何減少 PCB 布局中的串擾。 印刷電路板上的串擾 電路板上的活動過多會導致信號傳輸困難。考慮一下電路板上并排在一起的兩條走線。如果一條跡線的信號比另一條跡線的信號具有更大的幅度,可能會使另一條跡線過載。

2020-09-19 15:47:46 3330

3330 串擾中的信號耦合分為容性耦合和感性耦合,通常感性串擾占的比例大于容性串擾。

2020-11-20 10:47:23 5894

5894 來源:電源網 力科的信號完整性網絡分析儀SPARQ可快速定位連接器,背板和電纜的串擾,可使用單端或差分端口分配來測量近端串擾(NEXT,next-end crosstalk)或遠端串擾(FEXT

2020-10-12 01:59:22 2613

2613 本文主要介紹串擾的概念,及其FEXT、NEXT等,以及串擾的消除措施。 串擾串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲干擾。這種干擾是由于兩條信號線間的耦合,即

2020-10-19 17:54:49 8359

8359

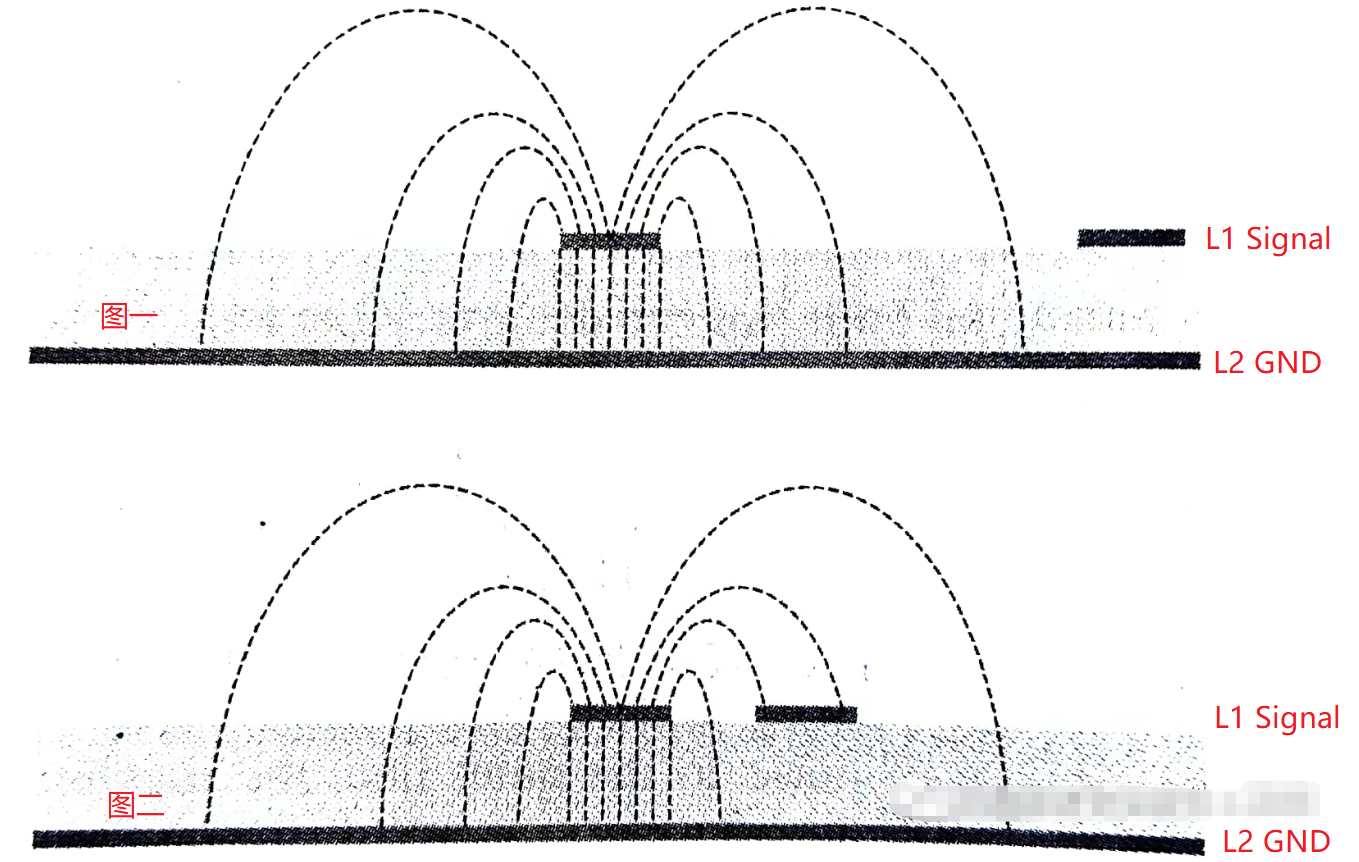

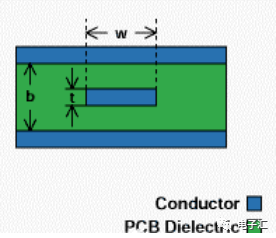

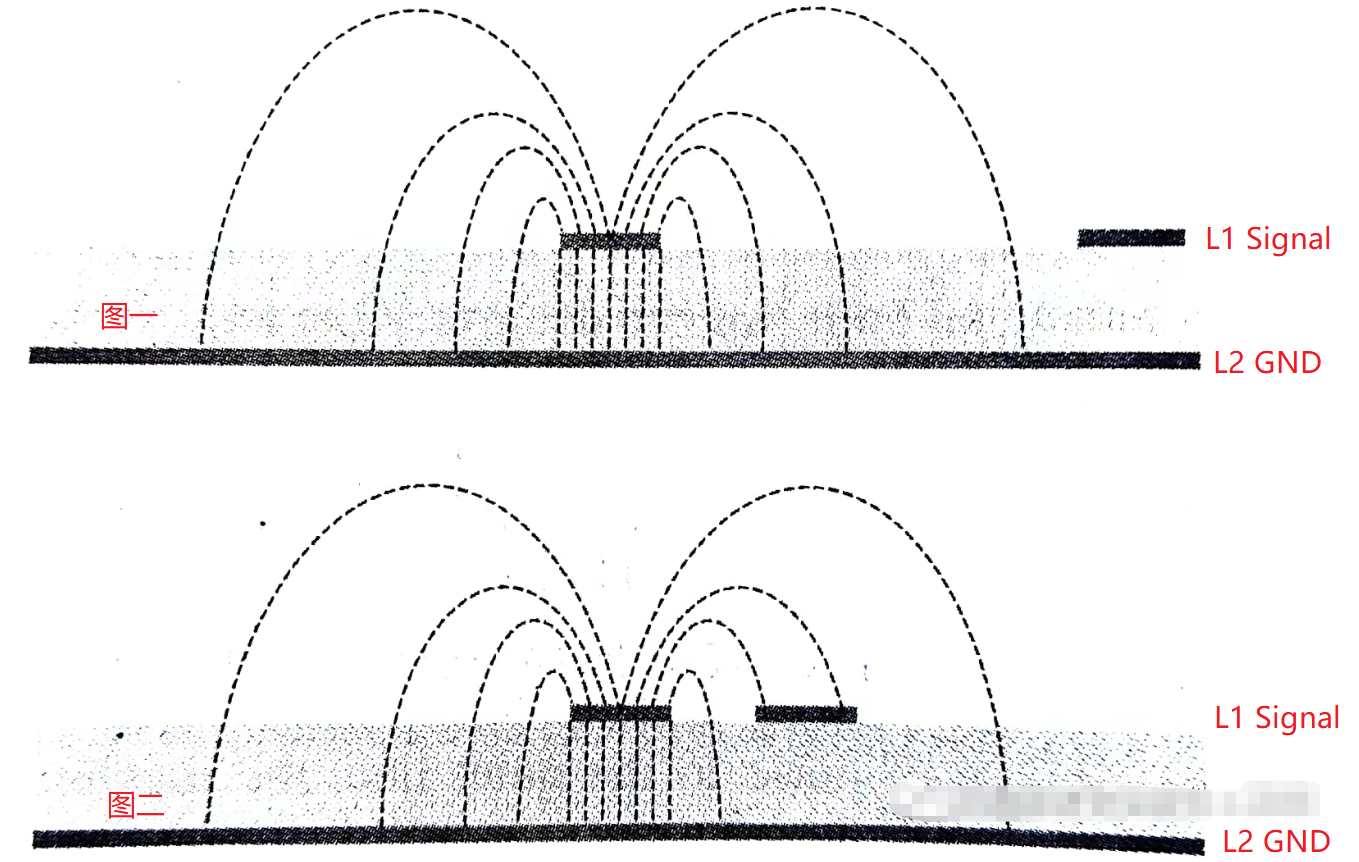

1、 層疊設計與同層串擾 很多時候,串擾超標的根源就來自于層疊設計。也就是我們第一篇文章說的設計上先天不足,后面糾正起來會比較困難。 講到層疊對串擾的影響,這里有另一張圖片,和上文提到的參考平面

2021-04-09 17:21:57 5483

5483

文章——串擾溯源。 提到串擾,防不勝防,令人煩惱。不考慮串擾,仿真波形似乎一切正常,考慮了串擾,信號質量可能就讓人不忍直視了,于是就出現了開頭那驚悚的一幕。下面就來說說串擾是怎么產生的。 所謂串擾,是指有害信號從一

2021-03-29 10:26:08 4155

4155 義: 攻擊者=高振幅+高頻+短上升時間 受害者=低振幅+高阻抗? 某些信號由于其性質或在電路中的功能而對串擾特別敏感,這些信號是潛在的串擾受害者?,如: 模擬信號:與數字信號相比,它們對噪聲更敏感,尤其是在振幅較低的情況下。 高阻

2020-12-25 15:12:29 3169

3169 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2021-01-23 08:19:24 16

16 電磁兼容之射頻電磁場輻射抗擾度試驗

2021-08-11 11:12:31 39

39 電磁兼容之射頻場感應的傳導騷擾抗擾度

2021-08-11 11:34:45 67

67 高速電路信號完整性分析與設計—串擾

2022-02-10 17:23:04 0

0 串擾的危害:

降低板內信號完整性

時鐘或者信號延遲

產生過沖電壓和突變電流

造成芯片邏輯功能紊亂

2022-07-07 10:35:01 1289

1289 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2022-08-15 09:32:06 11704

11704 一個網絡傳遞信號,有些電壓和電流通過網絡之間的耦合(容性耦合和感性耦合),傳遞到相鄰網絡,這就是串擾。

2022-08-16 09:23:52 6466

6466

在高速鏈路設計或者射頻鏈路設計中,串擾是一個非常重要的分析參數。如何測量、如何分析。一般遵循著一些設計經驗或者規則可以減小串擾的影響,但是很多時候卻難以按照規則設計,這就會帶來串擾影響的風險。

2022-08-24 09:32:27 3527

3527 我們知道:電源不穩定、電源的干擾、信號間的串擾、信號傳輸過程中的反射,這些都會讓信號產生畸變,看下面這張圖,你就會知道理想的信號,經過:反射、串擾、抖動,最后變成什么鬼。

2022-08-24 11:22:17 986

986 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。串擾也可以理解為感應噪聲。

2022-09-14 09:49:55 3781

3781

當串擾發生在信號的邊沿時,其作用效果類似于影響了信號的傳播時間,比如下圖所示,有3根信號線,前兩根等時傳播,第三根信號線在邊沿時收到了串擾,看起來信號傳播的時間被改變了

2022-12-12 11:01:21 1912

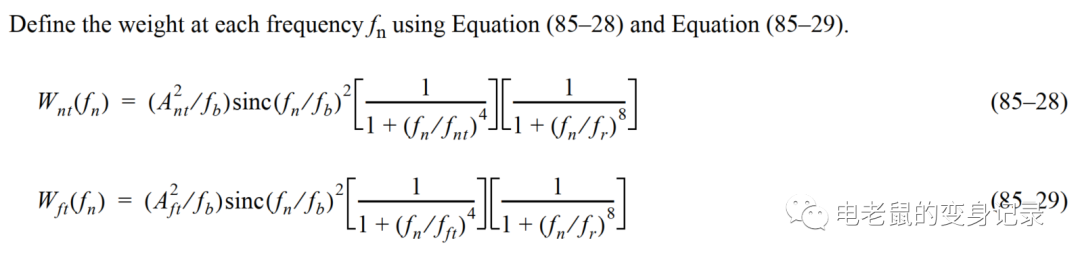

1912 關于兩個公式,我們不需要去記住,我們只需要知道它告訴了我們什么:攻擊信號的幅值影響著串擾的大小;減小串擾的途徑就是減小信號之間的耦合,增加信號與其回流平面之間的耦合。

2023-01-24 16:28:00 5755

5755

本章我們接著介紹信號完整性基礎第三章節串擾剩余知識。

2023-01-16 09:58:36 3159

3159 串擾,是兩條信號線之間的耦合產生的噪聲干擾。因此分析串擾的S參數就需要查看兩條線的特性,即一個四端口網絡,這時我們需要關注S31和S41

2023-05-05 17:29:57 4907

4907

串擾是指有害信號從一個網絡轉移到相鄰網絡。任何一對網絡之間都存在串擾。通常把噪聲源所在網絡稱為動態網絡或攻擊網絡。把受影響的網絡稱為靜態網絡或者受害網絡。

2023-05-06 11:48:08 3293

3293

串擾是 PCB 的走線之間產生的不需要的噪聲 (電磁耦合)。

2023-05-22 09:54:24 5606

5606

其他重要的系統電路有關,如數據線、地址線、控制線、和I/O線都可能受串擾和耦合效應影響。時鐘和周期信號是產生問題的主要原因,并且能導致其他區域的組件出現嚴重的功能性問題,如有客戶遇到板子上的高頻諧波,影響到2.4G通信問題。

2023-06-26 16:10:36 1220

1220

串擾是一種信號干擾現象,表現為一根信號線上有信號通過時,由于兩個相鄰導體之間所形成的互感和互容,導致在印制電路板上與之相鄰線的信號線就會感應相關的信號,稱之為串擾。

2023-07-03 15:45:10 5328

5328

串擾 :即兩條信號線之間的耦合引起的線上噪聲干擾。

2023-07-06 09:15:48 2670

2670

當信號通過電纜發送時,它們面臨兩個主要的通信影響因素:EMI和串擾。EMI和串擾嚴重影響信噪比。通過容易產生EMI 和串擾的電纜發送關鍵數據是有風險的。下面,讓我們來看看這兩個問題。

2023-07-06 10:07:03 3408

3408 串擾是指一個信號在傳輸通道上傳輸時,因電磁耦合而對相鄰的傳輸線產生不期望的影響,在被干擾信號表現為被注入了一定的耦合電壓和耦合電流。過大的串擾可能引起電路的誤觸發,導致系統無法正常工作。

2023-08-01 14:30:52 1591

1591

空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-08-21 14:26:46 700

700 pcb上的高速信號需要仿真串擾嗎? 在數字電子產品中,高速信號被廣泛應用于芯片內部和芯片間的數據傳輸。這些信號通常具有高帶寬,并且需要在特定的時間內準確地傳輸數據。然而,在高速信號傳輸的過程中,會出

2023-09-05 15:42:31 1458

1458 一站式PCBA智造廠家今天為大家講講pcb設計布線解決信號串擾的方法有哪些?PCB設計布線解決信號串擾的方法。信號之間由于電磁場的相互而產生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可

2023-10-19 09:51:44 2514

2514 雙絞線的串擾就是其中一個線對被相鄰的線對的信號串進來所干擾就是串擾。串擾本身是消除不了的,但只要控制在標準所要求以內就不會對網絡傳輸產生大的影響。

2023-11-01 10:10:37 2314

2314

“一秒”讀懂串擾對信號傳輸時延的影響

2023-11-28 17:07:27 1632

1632

串擾和反射影響信號的完整性? 串擾和反射是影響信號傳輸完整性的兩個主要因素。在深入討論之前,首先需要了解信號傳輸的基本原理。 在通信系統中,信號通常被傳輸通過各種類型的傳輸媒介,例如電纜、光纖或

2023-11-30 15:21:55 1146

1146 串擾是芯片后端設計中非常普遍的現象,它會造成邏輯信號的預期之外的變化。消除串擾的影響是后端的一個重要課題。

2023-12-06 15:38:19 2340

2340 空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-12-28 16:14:19 718

718

串擾(Crosstalk)是信號完整性(SignalIntegrity)中的核心問題之一,尤其在當今的高密度電路板設計中,其影響愈發顯著。當電路板上的走線密度增大時,各線路間的電磁耦合增強,串擾

2024-01-06 08:12:22 3925

3925

串擾是PCB(Printed Circuit Board)中走線之間產生的不需要的噪聲(電磁耦合)。串擾會對時鐘信號、周期和控制信號、數據傳輸線以及I/O產生不利影響。串擾無法完全消除,但可以通過

2024-01-17 15:02:12 3261

3261

了解什么是串擾及其常見原因。串擾是指一個信號電路中的電流或電磁場對周圍其他電路產生干擾的現象。常見的原因包括電磁輻射、電磁感應、信號反射、互連線長度不匹配等。 二、正確的布局設計 1.分離敏感信號與噪聲源:盡量分離敏感信號線和噪聲源

2024-02-02 15:40:30 2902

2902 在高頻電路的精密布局中,信號線的近距離平行布線往往成為引發“串擾”現象的潛在因素。串擾,這一術語描述的是未直接相連的信號線間因電磁耦合而產生的不期望噪聲信號,它如同電路中的隱形干擾源,對信號完整性

2024-09-25 16:04:45 1100

1100 改善串擾的設計方法據說有兩種:很多人知道的方法:信號線之間通過“包地”改善串擾……幾乎只有高速先生知道的方法:信號線之間通過“割地”改善串擾……

2024-11-11 17:26:11 822

822

電子發燒友App

電子發燒友App

評論