本文主要介紹串擾的概念,及其FEXT、NEXT等,以及串擾的消除措施。

串擾串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲干擾。這種干擾是由于兩條信號線間的耦合,即信號線之間互感和互容耦合引起的。容性耦合(當干擾源產生的干擾是以電壓形式出現時,干擾源與信號電路之間就存在容性(電場)耦合,這時干擾電壓線電容耦合到信號電路,形成干擾源)引發耦合電流,而感性耦合(當干擾源是以電流形式出現的,此電流所產生的磁場通過互感耦合對鄰近信號形成干擾)則產生耦合電壓。由于自身的邏輯電平發生變化,對其他信號產生影響的信號線稱為“攻擊線”(Aggressor),即干擾線。受到影響而導致自身邏輯電平發生異常的信號連線我們稱為“受害線”(Victim),即被干擾線。串擾噪聲從干擾對象上通過交叉耦合到被干擾對象上,表現為在一根信號線上有信號通過時,在PCB板上與之相鄰的信號線上就會感應出相關的信號。

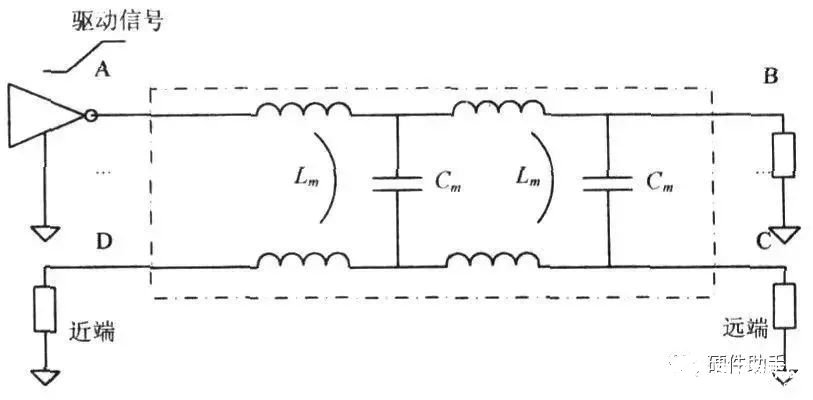

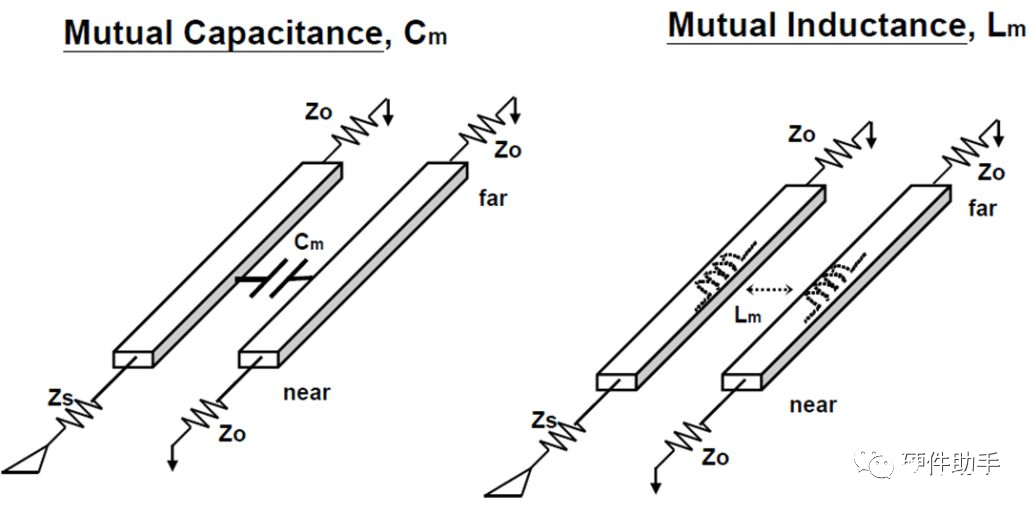

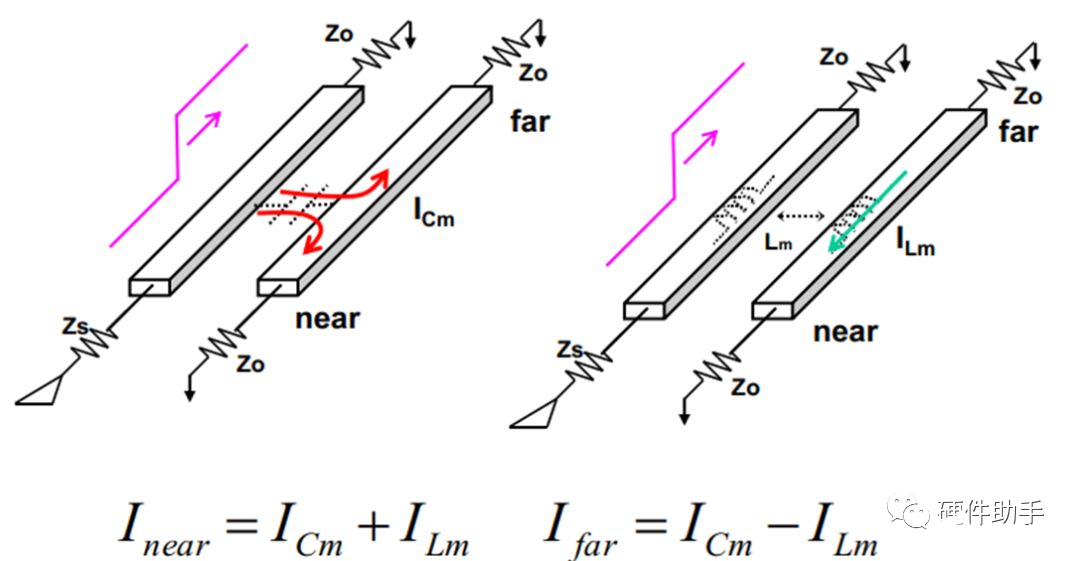

串擾由一條線到另一條線的能量耦合的方式主要分為電場(electric field)和磁場(magnetic field)。由于走線之間存在著互容(Mutual capacitance)和互感(Mutual inductance),一條走線上的AC信號便會從這些分布的互容和互感傳遞到另一根被干擾線(victim net)上。串擾可分為容性耦合串擾和感性耦合串擾兩類。

靜態網絡靠近干擾源一端的串擾稱為近端串擾(也稱后向串擾NEXT),而遠離干擾源一端的串擾稱為遠端串擾(或稱前向串擾FEXT)。

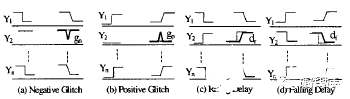

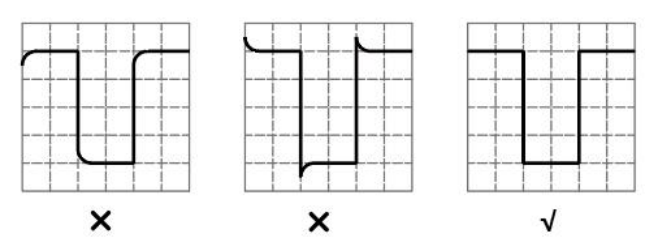

當干擾源狀態變化時,會在被干擾對象上產生一串擾脈沖,在高速系統中,這種現象很普遍。通常,依賴于干擾源和被干擾源上信號的跳變,被干擾線上產生四種類型的影響:正的短時脈沖,負的短時脈沖,上升時延,下降時延,如下圖所示:

串擾的來源當信號沿著傳輸線傳播時,在信號路徑與返回路徑之間存在電場和磁場。這些場的分布不僅僅限于信號和返回路徑之間的空間內,而是在周圍空間延伸。我們把這些延伸出去的場稱為邊緣場。

如果將兩導線的間距加大,可看到邊緣場的強度大大減弱。

第2根線處在邊緣場的附近時,就有過多的耦合和串擾。歸根結底,邊緣場是引起串擾的根本原因。減小串擾最重要的方法就是使網絡間的間距足夠遠,使其邊緣場降低到可以接受的范圍。

在系統中的每兩個網絡之間,總會有邊緣場產生的電感耦合和電容耦合。我們把耦合電感和耦合電容分別叫做互感和互容。

串擾的消除解決容性串擾,主要加大線間距,在PCB上的布線要遵循3W原則,即兩個傳輸線的線中心之間的距離要大于3倍的傳輸線的線寬。對系統中關鍵傳輸線,可以改用差分線傳輸以減少其它傳輸線對它的串擾;也可以對關鍵線的中間加地線保護以減少串擾。

解決感性串擾,主要減小回路面積,減小互感。例如,在芯片的電源的去耦電容,通過電容提供回流通道,可以減少回路面積,減小互感。

盡可能地減少相鄰傳輸線間的平行距離(累積的平行距離),最好在不同層間走線,相鄰兩層的信號層(中間沒有平面層隔離)走線方向應該相互正交,以減少層間的串擾。

在保證傳輸線特征阻抗的同時,使布線層與參考平面(電源平面或地平面)間的介質層盡可能的薄,這樣就加大了傳輸線與參考平面間的耦合度,從而減少相鄰傳輸線間的耦合。

在保證信號時序的情況下,盡可能選擇轉換速度低的元器件,這樣電場與磁場的變化速度慢一點,從而降低串擾。由于信號上升時間是造成SI 問題的主要原因,所以在滿足系統設計指標的情況下,應該盡可能選取信號上升沿較慢的器件。

可能的話,盡量少在表層走線,走帶狀線或嵌入式微帶線,因為表層線的電場耦合比中間層的要強(表層線只有一個參考平面),內層走線可以消除傳播速度的變化。

責任編輯:haq

-

電源

+關注

關注

185文章

18840瀏覽量

263493 -

電容

+關注

關注

100文章

6484瀏覽量

159322 -

電壓

+關注

關注

45文章

5773瀏覽量

121824 -

網絡

+關注

關注

14文章

8264瀏覽量

94702

發布評論請先 登錄

IDT信號完整性產品:解決高速信號傳輸難題

信號完整性(SI)/ 電源完整性(PI)工程師的核心技能樹體系

了解信號完整性的基本原理

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

受控阻抗布線技術確保信號完整性

信號完整性測試基礎知識

信號完整性系列之“串擾”

信號完整性系列之“串擾”

評論