我們經常聽說PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾,這就是3W原則,信號線之間的干擾被稱為串擾,串擾是怎么形成的呢?

當兩條走線很近時,一條信號線上的信號可能會在另一條信號線上產生噪聲,產生干擾的走線叫做攻擊線,收到干擾的走線叫做受害線。

PCB上走線與走線之間、走線與地之間會形成電容,其中一條走線有信號經過時,會產生變化的電場,這個電場通過電容,作用于另一條走線,在受害線上產生噪聲,進而產生串擾,這就是通常所說的電場耦合產生容性耦合電流。

同樣的道理,PCB上走線與走線之間、走線與地之間會形成互感,其中一條走線有信號經過時,會產生變化多的磁場,這個磁場通過互感,作用于另一條走線,在受害線上產生噪聲,進而產生串擾,這就是通常所說的磁場耦合產生感性耦合電流。

等長走線不一定等時!

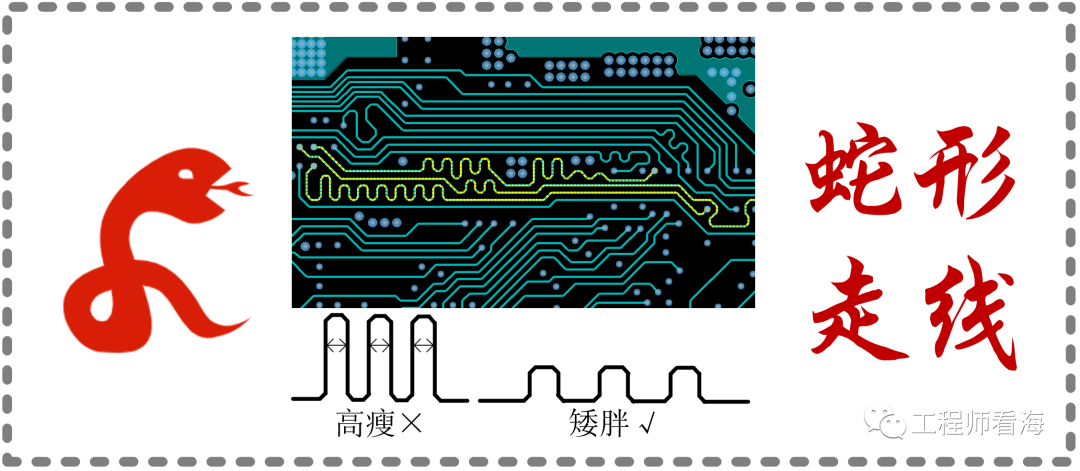

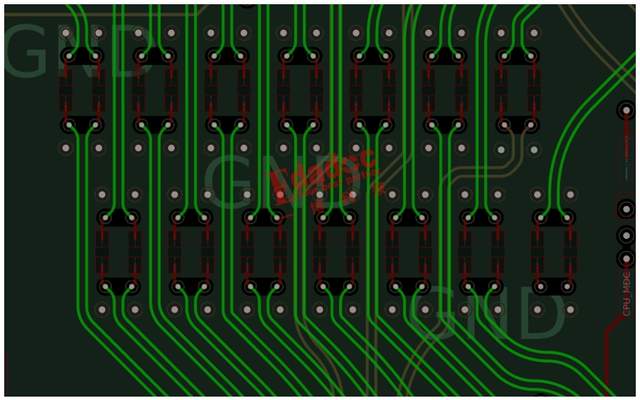

為了控制群組走線等時性的要求,比如手機MIPI信號、USB或DDR信號,通常的做法是對PCB走線進行繞等長處理,在初步調整走線后,選一根最長的走線為目標長度走線,其余走線通過繞線的方式增加走線長度,最終達到所有走線長度一致,俗稱蛇行走線,如上圖所示。

等長走線確保等延遲是依據信號在相同走線環境下的傳播速度是一樣的,走線長度一樣,信號傳播速度一樣,那么信號傳播的時間就一樣了。

實際上及時走線長度一樣,信號傳播的時間也不一定一樣,比如高瘦和矮胖這兩種繞等長的方法,高瘦走線中,有大量相鄰走線,會增加串擾;而矮胖走線,相鄰走線長度小,串擾也小。

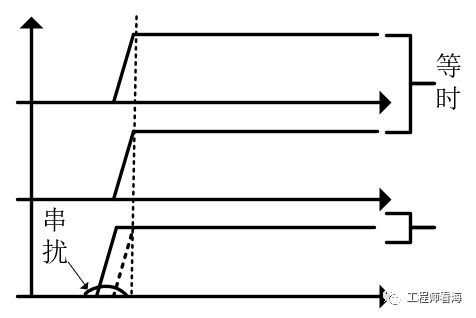

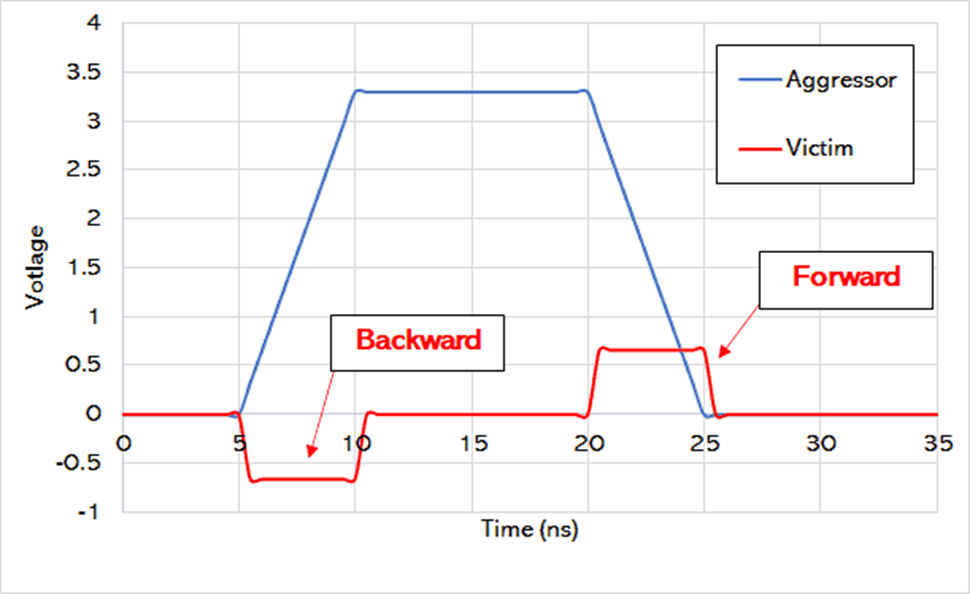

當串擾發生在信號的邊沿時,其作用效果類似于影響了信號的傳播時間,比如下圖所示,有3根信號線,前兩根等時傳播,第三根信號線在邊沿時收到了串擾,看起來信號傳播的時間被改變了

容性耦合電流和感性耦合電流共同構成了串擾,如何抑制串擾呢?

增加走線之間間距,這是非常有效的手段。

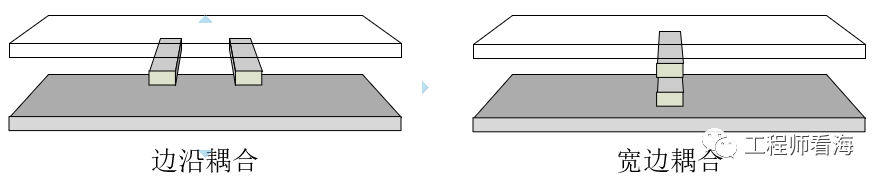

減小平行信號走線的長度,盡量做的垂直走線,避免下圖邊沿耦合和寬邊耦合的走線方式。

做好阻抗控制或做好端接電阻。

避免阻抗不連續使得串擾被反射,而加劇串擾的影響。

使用地線隔離。

在相鄰信號之間添加一條地線進行隔離,并且地線上打地孔,孔的間距小于λ/10(λ是波長,隔離地孔的使用場景比較復雜,這里只提供個經驗參考)。

在滿足datasheet需求條件下,降低信號上升沿時間。

審核編輯 :李倩

-

pcb

+關注

關注

4404文章

23878瀏覽量

424257 -

串擾

+關注

關注

4文章

196瀏覽量

27837

原文標題:你的蛇行走線,對嗎?

文章出處:【微信號:玩轉單片機與嵌入式,微信公眾號:玩轉單片機與嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

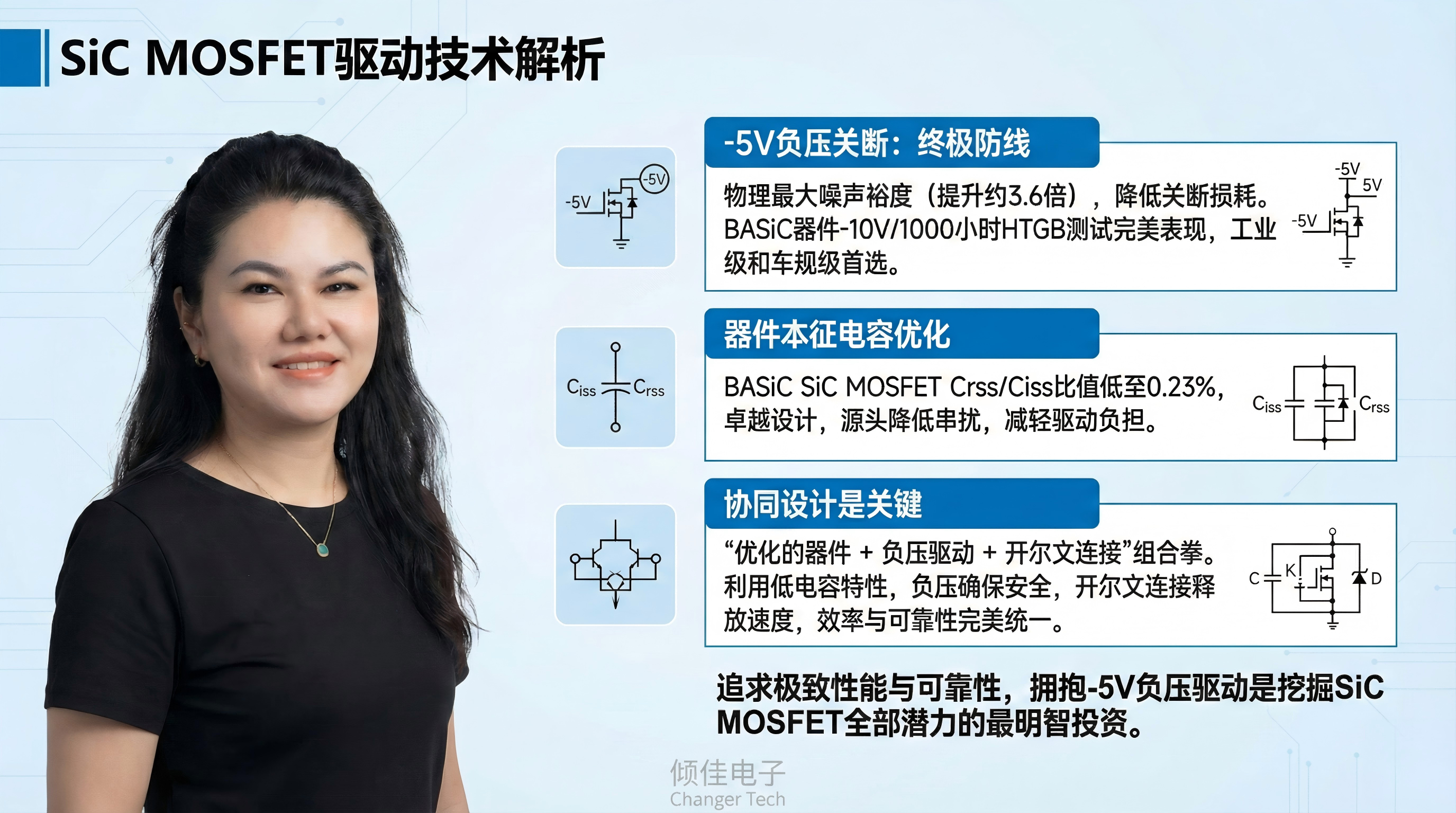

碳化硅MOSFET串擾抑制策略深度解析:負壓關斷與寄生電容分壓的根本性優勢

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

隔離地過孔要放哪里,才能最有效減少高速信號過孔串擾?

昊衡科技全新推出——偏振串擾分析儀OLI-P助力保偏光纖系統性能躍升

SiC MOSFET并聯均流及串擾抑制驅動電路的研究

技術資訊 I 哪些原因會導致近端和遠端串擾?

高速AC耦合電容挨得很近,PCB串擾會不會很大……

高速AC耦合電容挨得很近,PCB串擾會不會很大……

NEXT(Near-End Crosstalk,近端串擾)

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

OLI-P——分布式偏振串擾測量利器

武漢昊衡科技重磅推出全新設備——偏振串擾分析儀OLI-P助力保偏光纖系統性能躍升

串擾是怎么形成的呢?

串擾是怎么形成的呢?

評論