可編程邏輯

提供權威的PLD及可編程邏輯器件設計應用、Altera公司、Xilinx公司資訊和解決方案,包括HDL語言與源代碼、FPGA開發(fā)板、EDA工具、FPGA、FPGA軟件等領域。用FPGA器件實現(xiàn)UART核心功能的一種方法

串行外設都會用到RS232-C異步串行接口,傳統(tǒng)上采用專用的集成電路即UART實現(xiàn),如TI、EXAR、EPIC的550、452等系列,但是我們一般不需要使用完整的UART的功能,而且對于多串...

2009-06-20 標簽:uart 965

用CPLD實現(xiàn)單片機讀寫模塊

摘要:介紹實現(xiàn)單片機與Xilinx公司XC9500系列可編程邏輯器件的讀寫邏輯功能模塊的接口設計,以及Xilinx公司的XC9500系列可編程邏輯器件的開發(fā)流程。 ...

2009-06-20 標簽:cpld 1820

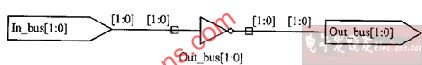

非多路復用與多路復用總線轉換橋的設計與實現(xiàn)

摘要:提出了一種新穎的非多路復用總線與多路復用總線的轉換接口電路。以兩種總線的典型代表芯片TMS320F206與SJA1000為例,分...

基于CPLD的系統(tǒng)中I2C總線的設計

摘要: 在介紹I2C總線協(xié)議的基礎上,討論了基于CPLD的系統(tǒng)中I2C總線的設計技術,并結合工程實例設計了I2C總線IP核,給出了部分源代碼和仿...

2009-06-20 標簽:I2C總線 2866

用Verilog HDL實現(xiàn)I2C總線功能

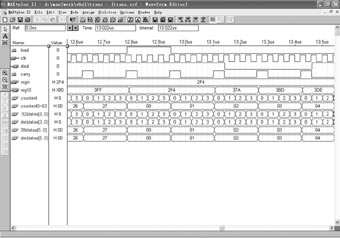

摘要: 簡述了I2C總線的特點;介紹了開發(fā)FPGA時I2C總線模塊的設計思想;給出并解釋了用Verilog HDL實現(xiàn)部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖...

2009-06-20 標簽:I2C總線 7184

基于VHDL的I2C總線控制核設計

摘要: 從狀態(tài)機的角度,介紹一種I2C控制核的VHDL設計方法。將其嵌入到FPGA中,用于實現(xiàn)與TMS320C6000系列DSP的接口,并配合DSP的軟件完成對視頻采集與顯示處理系統(tǒng)...

2009-06-20 標簽:I2C總線 2344

用FPGA/CPLD設計UART

摘 要 :UART是廣泛使用的串行數(shù)據(jù)通訊電路。本設計包含UART發(fā)送器、接收器和波特率發(fā)生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現(xiàn)UART。 ...

2009-06-20 標簽:uart 1310

用CPLD實現(xiàn)DSP與PLX9054之間的連接

摘要: 介紹了利用CPLD實現(xiàn)DSP芯片TMS320C6711b和PCI橋芯片PLX9054之間高速數(shù)據(jù)傳輸?shù)南到y(tǒng)設計方法,并給出了相應的系統(tǒng)設計原理圖,同時對該系統(tǒng)的性能進行了分析。...

2009-06-20 標簽:cpld 1588

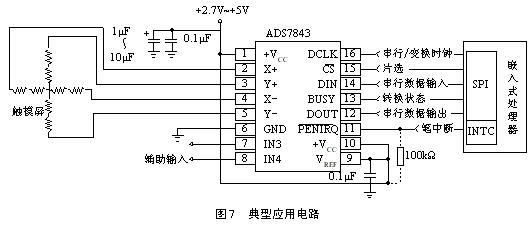

可復用SPI模塊IP核的設計與驗證

摘要: SoC是超大規(guī)模集成電路的發(fā)展趨勢和新世紀集成電路的主流[1]。其復雜性以及快速完成設計、降低成本等要求,決定了系統(tǒng)級芯片的設計必須采用IP(Intellectual...

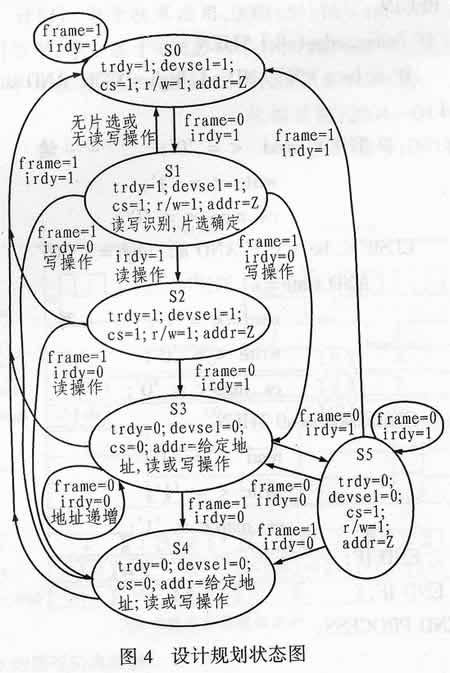

簡易通用型PCI接口的VHDL-CPLD設計

摘要: 從PCI時序分析入手,重點闡述了PCI通用的狀態(tài)機設計,說明了用VHDL語言來實現(xiàn)本PIC通信狀態(tài)機的軟件設計以及進行MaxPlusII驗證的程序和方法。用該方法所設...

2009-06-20 標簽:PCI 1125

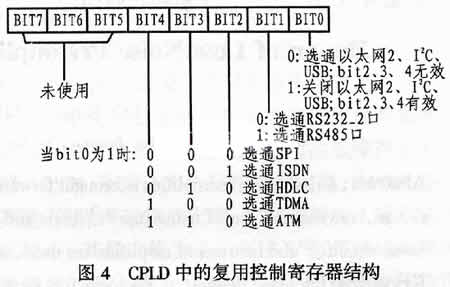

MPC850中復位邏輯和CPM協(xié)議切換的CPLD實現(xiàn)

摘要: 介紹了用CPLD輔助設計在嵌入系統(tǒng)中進行曲MPU復雜邏輯功能設計的總體方案,給出了通過對XC95144中復用控制寄存器進行配置以實現(xiàn)MPU復位邏輯和CPM協(xié)議切換的實現(xiàn)方案...

2009-06-20 標簽:cpld 1189

使用Verilog實現(xiàn)基于FPGA的SDRAM控制器

摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設計方法,使用該方法實現(xiàn)的控制器可非常方便地對SDRAM進行控制。 關鍵...

SDRAM控制器的設備與VHDL實現(xiàn)

摘要: 介紹了SDRAM的存儲體結構、主要控制時序和基本操作命令,并且結合實際系統(tǒng),給出了一種用FPGA實現(xiàn)的通用SDRAM控制器的方案。 關鍵詞: ...

2009-06-20 標簽:SDRAM 1071

一種基于移位寄存器的CAM的Verilog HDL實現(xiàn)

摘要:一種利用Verilog HDL設計CAM的方案,該方案以移位寄存器為核心,所實現(xiàn)的CAN具有可重新配置改變字長、易于擴展、匹配查找速度等特點,并在網(wǎng)絡協(xié)處理器仿真中得到...

錯誤檢測與糾正電路的設計與實現(xiàn)

摘 要:針對一些惡劣的電磁環(huán)境對隨機存儲器(RAM)電路誤碼影響的情況,根據(jù)糾錯編碼的基本原理,提出簡單實用的能檢查兩位錯誤并自動糾正一位錯誤的EDAC...

異步FIFO結構及FPGA設計

摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法;在傳統(tǒng)設計的基礎上提出一種新穎的電路結構并對其進行...

2009-06-20 標簽:fifo 4226

基于CPLD/FPGA的半整數(shù)分頻器的設計

摘要:簡要介紹了CPLD/FPGA器件的特點和應用范圍,并以分頻比為2.5的半整數(shù)分頻器的設計為例,介紹了在MAX+plus II開發(fā)軟件下,利用VHDL硬件描述語言以及原理圖的輸...

用VHDL語言在CPLD上實現(xiàn)串行通信

摘 要: 串行通信是實現(xiàn)遠程測控的重要手段。采用VHDL語言在CPLD上實現(xiàn)了串行通信,完全可以脫離單片機使用。 關鍵詞: ...

2009-06-20 標簽:cpld 993

基于FPGA的多種形式分頻的設計與實現(xiàn)

摘 要: 本文通過在QuartursⅡ開發(fā)平臺下,一種能夠實現(xiàn)等占空比、非等占空比整數(shù)分頻及半整數(shù)分頻的通用分頻器的FPGA設計與實現(xiàn),介紹了利用VHDL硬件描...

2009-06-20 標簽:FPGA 754

基于FPGA的高頻時鐘的分頻和分配設計

摘要:介紹了為PET(正電子發(fā)射斷層掃描儀)的前端電子學模塊提供時間基準而設計的一種新型高頻時鐘扇出電路。該電路利用FPGA芯片來實現(xiàn)對高頻時鐘的分頻...

2009-06-20 標簽:FPGA 1572

使用PLD內(nèi)部鎖相環(huán)解決系統(tǒng)設計難題

摘要: 從整個應用系統(tǒng)的角度,理解和分析PLD內(nèi)部鎖相環(huán);在此基礎上,深入剖析鎖相環(huán)的相移結構,同時用這個技術解決系統(tǒng)設計難題。 關鍵...

2009-06-20 標簽:PLD 1047

智能全數(shù)字鎖相環(huán)的設計

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎上進行改進,設計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進行動態(tài)智...

2009-06-20 標簽:鎖相環(huán) 1801

VHDL設計中電路簡化問題的探討

摘 要:從描述方法、設計規(guī)則、邏輯函數(shù)分析了VHDL設計中容易引起電路復雜化的原因,并提出了相應的解決方法。 關鍵詞:VHDL 電路簡化...

2009-06-20 標簽:vhdl 1217

在PLD開發(fā)中提高VHDL的綜合質量

摘 要:介紹可編程邏輯器件的開發(fā)流程,敘述EDA工具Quartus II和LeonardoSpectrum在Altera公司CPLD器件開發(fā)中的應用,給出提高VHDL綜合質量的幾點經(jīng)驗。 關鍵詞:電...

2009-06-20 標簽:PLD 945

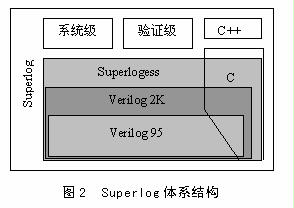

硬件描述語言HDL的現(xiàn)狀與發(fā)展

摘要:從數(shù)字系統(tǒng)設計的性質出發(fā),結合目前迅速發(fā)展的芯片系統(tǒng),比較、研究各種硬件描述語言;詳細闡述各種語言的發(fā)展歷史、體系結構和設計方法;探討未來...

2009-06-20 標簽:HDL 1958

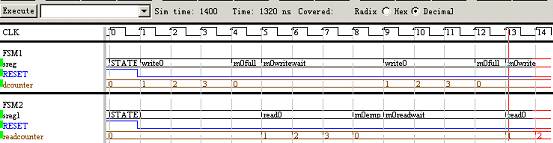

多狀態(tài)機的協(xié)同設計

隨著微電子技術的迅速發(fā)展,人們對數(shù)字系統(tǒng)的需求也在提高[ 1 ]。不僅要有完善的功能,而且對速度也提出了很高的要求。對于大部分數(shù)字系統(tǒng),都可以劃分為控制單元...

用STATECAD快速設計有限狀態(tài)機

數(shù)字系統(tǒng)通常劃分為信息處理單元和控制單元。信息單元主要進行信息的傳輸和運算, 而控制單元的主要任務是控制信息處理單元的微操作的順序。控制單元的...

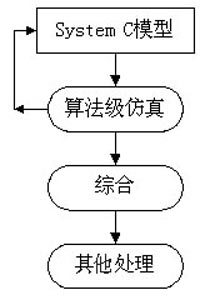

基于SYSTEM C的FPGA設計方法

摘 要: 隨著VLSI的集成度越來越高,設計也越趨復雜。傳統(tǒng)的設計方法如原理圖輸入、HDL語言描述在進行復雜系統(tǒng)設計時,設計效率往往比較低。特別是在...

2009-06-20 標簽:FPGA 601

Verilog HDL語言在FPGA/CPLD開發(fā)中的應用

摘 要:通過設計實例詳細介紹了用Verilog HDL語言開發(fā)FPGA/CPLD的方法,并通過與其他各種輸入方式的比較,顯示出使用Verilog HDL語言的優(yōu)越性。 ...

編輯推薦廠商產(chǎn)品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術 | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |