現(xiàn)在“零功耗”的含義是指在大多數(shù)應(yīng)用中CPLD具有許多 節(jié)省功耗的特點(diǎn),以及可以用于充分減少器件功耗需求的核心邏輯。

2011-11-21 15:48:54 2158

2158 本文描述了復(fù)位的定義,分類及不同復(fù)位設(shè)計(jì)的影響,并討論了針對(duì)FPGA和CPLD的內(nèi)部自復(fù)位方案。

2016-07-11 14:33:49 7289

7289

CPLD邏輯電路

2019-10-29 09:10:54

,現(xiàn)有一個(gè)邏輯關(guān)系不會(huì)處理,請(qǐng)各位幫忙(盡量用圖形輸入法,VHDL看不懂,正在學(xué)習(xí)中),我看過(guò)用觸發(fā)器去做,但需要CLK信號(hào),這個(gè)信號(hào)要從CPLDI/O口引入,但板子已做好,該邏輯關(guān)系是后加的,所以希望

2012-12-24 22:39:54

最近想做一個(gè)液晶屏驅(qū)動(dòng)板,采用CPLD+Sram的方案,性價(jià)比高,芯片也不貴,做好驅(qū)動(dòng)板之后,可以用單片機(jī)控制驅(qū)動(dòng)板來(lái)最終實(shí)現(xiàn)控制液晶屏顯示,CPLD采用EPM240Sram采用

2019-02-25 20:28:54

MPC850 - Communications Controller Hardware Specifications - Motorola, Inc

2022-11-04 17:22:44

我正在為 MPC5744P 編寫引導(dǎo)加載程序。當(dāng)在 APP 中檢測(cè)到下載請(qǐng)求時(shí),看門狗復(fù)位用于從 APP 跳轉(zhuǎn)到引導(dǎo)加載程序。我想將此請(qǐng)求標(biāo)志保存在 RAM 中。當(dāng)項(xiàng)目重置時(shí),標(biāo)志如何保留在 RAM 中?謝謝你!

2023-03-27 09:10:16

ADC 的 cpld 代碼,實(shí)現(xiàn)該串行轉(zhuǎn)并行的功能。

相當(dāng)于:ADC硬核+ADC的cpld邏輯,實(shí)現(xiàn)了一個(gè)完整的“ADC 外設(shè)”。

ADC的用戶cpld代碼,都是在 analog_ip.v中實(shí)現(xiàn)

2025-04-07 09:25:33

一、在AGM 的AG32 CPLD中實(shí)現(xiàn)DMA(直接內(nèi)存訪問(wèn))功能,其核心邏輯如下:

1、系統(tǒng)架構(gòu)?采用主從架構(gòu):MCU作為主設(shè)備,CPLD作為從設(shè)備?交互方式:MCU通過(guò)訪問(wèn)寄存器的方式

2025-10-31 15:42:18

cpld中實(shí)現(xiàn)DMA的邏輯:

Mcu為master,cpld為slave,mcu對(duì)cpld的交互方式為存取寄存器的方式;

mcu中配置好DMA(讀取cpld中準(zhǔn)備好的數(shù)據(jù));

cpld中準(zhǔn)備好數(shù)據(jù)后

2025-08-12 09:22:56

也不會(huì)丟失

立即上電 :上電后立即開始運(yùn)作

可在單芯片上運(yùn)作

內(nèi)建高性能硬宏功能

PLL

存儲(chǔ)器模塊

DSP模塊

用最先進(jìn)的技術(shù)實(shí)現(xiàn)高集成度,高性能

需要外部配置ROM

應(yīng)用范圍偏向于簡(jiǎn)單的控制通道應(yīng)用以及

膠合邏輯偏向于較復(fù)雜且高速的控制通道應(yīng)用以及數(shù)據(jù)處理集成度小~中規(guī)模中~大規(guī)模

2011-09-27 09:49:48

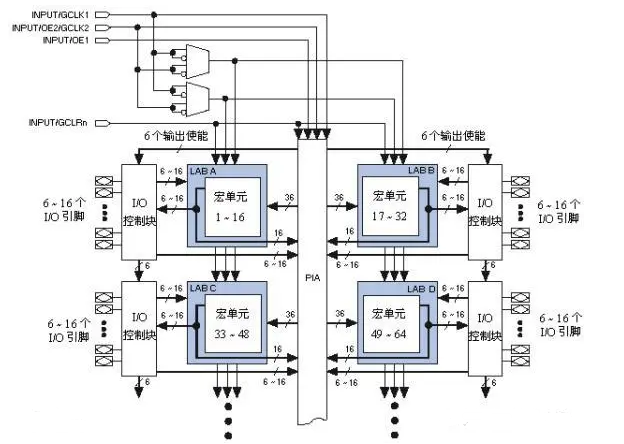

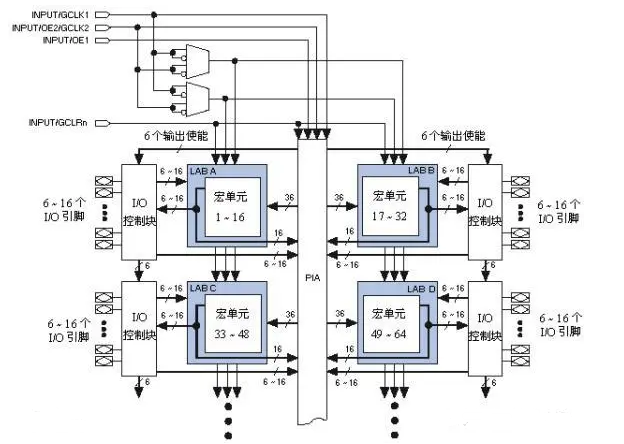

的路徑。這就是為何CPLD被認(rèn)為是“邏輯豐富”型的。宏單元以邏輯模塊的形式排列(LB),每個(gè)邏輯模塊由16個(gè)宏單元組成。宏單元執(zhí)行一個(gè)AND操作,然后一個(gè)OR操作以實(shí)現(xiàn)組合邏輯。每個(gè)邏輯群有8個(gè)邏輯模塊

2012-10-26 08:10:36

FPGA與CPLD(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-12 13:54:42

大家好...一世我正在使用XC95144xl CPLD從事系統(tǒng)內(nèi)編程項(xiàng)目。一世想知道JTAG協(xié)議如何用于編程CPLD。我的意思是四個(gè)信號(hào)tck,tdi,tdo和tms如何實(shí)現(xiàn)“CPLD編程”。除了

2019-01-15 10:08:00

verilog實(shí)現(xiàn)I2C透?jìng)鳎鳛橹鲝臋C(jī)設(shè)備之間的傳輸通道,但是SDA信號(hào)在cpld的端口進(jìn)行輸入、輸出狀態(tài)切換的邏輯始終處理不好,有沒(méi)有大佬能幫忙分析一下!

2022-08-17 11:22:27

,我們可以改變?nèi)我獾刂稢1B1A1CBAS2S1S0的值,即完成任意驅(qū)動(dòng)信號(hào)的實(shí)現(xiàn),解決了CPLD在橫機(jī)機(jī)頭板應(yīng)用中不方便布板的問(wèn)題,增加了客戶布板的靈活性。歡迎登錄進(jìn)行評(píng)論

2017-08-22 10:11:38

Device)生成各種邏輯電平來(lái)控制螺線管和步進(jìn)電機(jī),所以CPLD被橫機(jī)客戶廣泛使用。橫機(jī)機(jī)頭板一般由主板和子板,子板通過(guò)接插件插在主板上完成最終的控制功能(如圖一)。因?yàn)槊總€(gè)子板都有控制信號(hào)來(lái)自母板,所以

2022-11-14 06:52:19

主板上。圖二由此可見通過(guò)上述方法,我們可以改變?nèi)我獾刂稢1B1A1CBAS2S1S0的值,即完成任意驅(qū)動(dòng)信號(hào)的實(shí)現(xiàn),解決了CPLD在橫機(jī)機(jī)頭板應(yīng)用中不方便布板的問(wèn)題,增加了客戶布板的靈活性。歡迎登錄進(jìn)行評(píng)論

2019-03-26 06:45:09

現(xiàn)在大多數(shù)的CPLD(復(fù)雜可編程邏輯器件)都采用可減少功耗的工作模式,但當(dāng)系統(tǒng)未使用時(shí),應(yīng)完全切斷電源以保存電池能量,從而實(shí)現(xiàn)很多設(shè)計(jì)者的終極節(jié)能目標(biāo)。圖1描述了如何在一片CPLD 上增加幾只

2018-09-26 17:29:24

相關(guān)接口)是物理層芯片與物理介質(zhì)的接口;PCS、PMA和PMD則分別表示實(shí)現(xiàn)物理層協(xié)議的各子層。在實(shí)際應(yīng)用系統(tǒng)中,這些子層的操作細(xì)節(jié)將全部由PHY芯片實(shí)現(xiàn),只需對(duì)MII和MDI接口進(jìn)行設(shè)計(jì)與操作即可。吉

2018-11-30 11:27:55

七大模塊組成。FPGA核心調(diào)度模塊是下位機(jī)的核心部分,完成對(duì)下位機(jī)各個(gè)模塊間的協(xié)調(diào)運(yùn)行與邏輯控制,實(shí)現(xiàn)全局時(shí)鐘管理、TCP/IP協(xié)議與串口通信、命令和數(shù)據(jù)的組幀與解析、通道切換與配置、信號(hào)采集與數(shù)據(jù)處理

2021-07-12 08:30:00

本設(shè)計(jì)利用CPLD進(jìn)行數(shù)字邏輯器件設(shè)計(jì),并配合多路精密程控放大,實(shí)現(xiàn)了寬輸入范圍高精度頻率測(cè)量,頻率測(cè)量穩(wěn)定度達(dá)10 -7,而且將輸入信號(hào)的范圍進(jìn)行了有效地拓寬,使這種高精度頻率計(jì)的應(yīng)用領(lǐng)域更加廣泛。同時(shí),解決了傳統(tǒng)分立數(shù)字器件測(cè)頻時(shí)存在的問(wèn)題。

2021-05-14 06:24:24

嗨, 我正在通過(guò)App。關(guān)于如何連接CRII CPLD中的LED的說(shuō)明805。該說(shuō)明提到CPLD可以在LED的情況下吸收電流,即。如果連接的引腳處于邏輯0,那么LED將發(fā)光,反之亦然。如果連接的引腳

2019-08-08 06:20:48

直流電動(dòng)機(jī)的PWM控制原理是什么?如何采用CPLD實(shí)現(xiàn)數(shù)字控制PWM信號(hào)?如何利用CPLD技術(shù)實(shí)現(xiàn)了邏輯和時(shí)序的控制?

2021-05-07 06:03:34

我想通過(guò)按鍵實(shí)現(xiàn)復(fù)位,能不能提示下怎么寫外部復(fù)位邏輯啊?

2015-01-20 21:37:58

數(shù)字系統(tǒng)的設(shè)計(jì)人員擅長(zhǎng)在其印制電路板上用FPGA和CPLD將各種處理器、存儲(chǔ)器和標(biāo)準(zhǔn)的功能元件粘合在一起來(lái)實(shí)現(xiàn)數(shù)字設(shè)計(jì)。除了這些數(shù)字功能之外,F(xiàn)PGA和CPLD還可以使用LVDS輸入、簡(jiǎn)單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實(shí)現(xiàn)共模功能,從而構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。

2019-08-19 06:15:33

我想做一個(gè)純硬件的電路,實(shí)現(xiàn)用自復(fù)位的按鍵,按一下實(shí)現(xiàn)高低電平的切換,簡(jiǎn)單來(lái)說(shuō)就是按一下輸出高電平,再按一下輸出低電平,雖然用CPU可以很簡(jiǎn)單的實(shí)現(xiàn),但是因?yàn)轫?xiàng)目需要硬件來(lái)實(shí)現(xiàn),大家有沒(méi)有什么好的方法,謝謝大家!!!

2019-06-21 14:47:56

依舊是2M,經(jīng)測(cè)試,最多只能例化兩次。CPLD型號(hào)是EPM570T100C5, 時(shí)鐘50MHz,異步復(fù)位,RTL視圖和波形示意圖如下所示:

2016-09-01 10:42:44

。MPC8260支持多種DMA實(shí)現(xiàn)方式,分別適用于不同數(shù)據(jù)傳輸源/目的設(shè)備、不同傳輸數(shù)據(jù)塊大小和存儲(chǔ)模式的需要,因此需要根據(jù)主控板的系統(tǒng)特點(diǎn)設(shè)計(jì)出合適的DMA傳輸接口。1MPC8260的 DMA系統(tǒng)結(jié)構(gòu)圖2CPM

2019-05-22 05:00:53

如何通過(guò)添加一個(gè)簡(jiǎn)單的RC電路至FPGA或CPLD 的LVDS輸入來(lái)實(shí)現(xiàn)模數(shù)轉(zhuǎn)換器?請(qǐng)問(wèn)怎么實(shí)現(xiàn)低頻率(DC至1K Hz)和高頻率(高達(dá)50K Hz)ADC?

2021-04-15 06:29:55

在于:① SDRAM中的數(shù)據(jù)和MPC8260的數(shù)據(jù)同步比較復(fù)雜。② 每次發(fā)出請(qǐng)求信號(hào)后都要進(jìn)行總線仲裁,并且在得到總線使用權(quán)之后一次只能夠傳輸外設(shè)端口大小或者32位的數(shù)據(jù),總線利用率低。③ 握手控制邏輯

2019-04-18 07:00:08

針對(duì)安全協(xié)議一階邏輯模型不能夠給出易于理解的攻擊序列的問(wèn)題,對(duì)安全協(xié)議一階邏輯模型進(jìn)行擴(kuò)展,對(duì)邏輯推理中的規(guī)則及合一化操作進(jìn)行分類,給出操作置換規(guī)則,在此基

2009-03-20 16:01:09 25

25 在電動(dòng)車驅(qū)動(dòng)控制單元的設(shè)計(jì)中,邏輯處理部分的設(shè)計(jì)是關(guān)系到汽車安全可靠行使的關(guān)鍵環(huán)節(jié)。本文中采用CPLD 邏輯處理與微處理器管理相結(jié)合實(shí)現(xiàn)邏輯控制,可以根據(jù)不同運(yùn)行

2009-05-30 08:22:39 8

8 Motorola’s MPC850 broadens the PowerPC™ family portfolio by offering similar integration

2009-06-19 09:32:27 21

21 characteristics, and AC timing speciÞcations for revision A and B of the MPC850.This document contains the following topics:Topic PageS

2009-06-24 11:40:39 34

34 The MPC850 integrated communications microprocessor is a versatile, one-chip integrated

2009-06-24 11:42:15 24

24 MPC806作為一款功能強(qiáng)大的嵌人式通信處理器,缺乏對(duì)USB的支持必然限制其在某些領(lǐng)域的應(yīng)用;所以提出了一種基于FT245BM實(shí)現(xiàn)MPc860USB通信接口的方法;實(shí)現(xiàn)FT245BM和處理器的連接有兩種通

2009-07-16 14:18:51 17

17 在使用Flash 存儲(chǔ)數(shù)據(jù)時(shí),有時(shí)需要對(duì)其設(shè)計(jì)讀寫控制邏輯。本文介紹了用VHDL 語(yǔ)言在CPLD內(nèi)部編程,實(shí)現(xiàn)對(duì)Flash 中數(shù)據(jù)的讀取控制的具體方法,并給出

2009-09-04 09:29:36 35

35 設(shè)計(jì)一種基于MCS-51 單片機(jī)與FPGA/CPLD 的總線接口邏輯,實(shí)現(xiàn)單片機(jī)與可編程邏輯器件數(shù)據(jù)與控制信息的可靠通信,使可編程邏輯器件與單片機(jī)相結(jié)合,優(yōu)勢(shì)互補(bǔ),組成靈活的、軟硬件

2009-09-22 10:16:40 83

83 摘要:介紹了一種采用CPLD實(shí)現(xiàn)嵌入式CPU外圍電路的方法,將數(shù)據(jù)總線、譯碼單元、分頻電路及邏輯電路集成于一片CPLD,大大縮小了印制板的面積并提高了系統(tǒng)可靠性,同時(shí),由于CPLD

2010-05-10 09:23:49 29

29 闡述了MPC860芯片及其SCC接口的基本工作原理,介紹了在SCC通道上實(shí)現(xiàn)HDLC協(xié)議的基本設(shè)計(jì)思想及具體實(shí)現(xiàn),并給出了主要功能函數(shù)的設(shè)計(jì)流程。

2010-07-02 17:01:12 17

17 XCR3256是Xilinx公司推出的CoolRunner系列CPLD器件,在數(shù)字系統(tǒng)設(shè)計(jì)中的應(yīng)用非常廣泛。本文詳細(xì)分析了CoolRunner系列CPLD的特點(diǎn)、結(jié)構(gòu)及功能,使用VHDL語(yǔ)言編程實(shí)現(xiàn)數(shù)字邏輯,實(shí)現(xiàn)了水下沖擊

2010-08-06 16:29:07 15

15 摩托羅拉MPC8260 微處理器芯片因其強(qiáng)大的通信處理能力和多種協(xié)議的支持而被廣泛應(yīng)用于通信和網(wǎng)絡(luò)領(lǐng)域。本文以MPC8260 為例,探討在嵌入式系統(tǒng)中實(shí)現(xiàn)基于VxWorks 操作系統(tǒng)的快

2010-10-08 16:05:54 32

32 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 1194

1194

換體DMA高速數(shù)據(jù)采集電路的CPLD實(shí)現(xiàn)

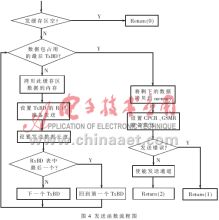

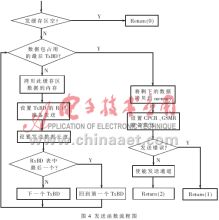

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實(shí)現(xiàn)。用CPLD設(shè)計(jì)雙端口RAM緩存、控制譯碼、時(shí)序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 1008

1008

CPLD在多路高速同步數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)是在傳統(tǒng)的PAL、GAL基礎(chǔ)上發(fā)展而來(lái)的,具有多種工作方式

2009-03-28 16:49:00 1302

1302

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的簡(jiǎn)稱,一種較PLD為復(fù)雜的邏輯元件。CPLD是一種用戶根據(jù)各自

2009-03-30 13:40:43 4116

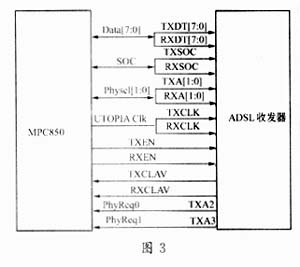

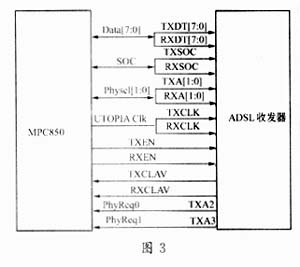

4116 【摘 要】 介紹了基于PowerPC內(nèi)核的嵌入式通信控制器芯片MPC850,及一種開發(fā)MPC850通信功能的硬件平臺(tái)設(shè)計(jì)。 關(guān)鍵詞:嵌

2009-05-11 19:38:12 1778

1778

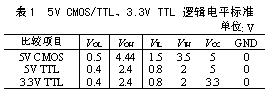

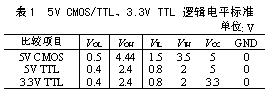

摘要: 較詳細(xì)地闡述不同邏輯電平的接口原理。以低壓CPLD EPM7512A為例,給出在混合電壓系統(tǒng)中的具體設(shè)計(jì)方案。

關(guān)鍵詞: 低壓CPLD 邏輯電平

2009-06-20 10:53:23 1153

1153

?摘 要:介紹了一種利用ALTERA公司的復(fù)雜可編程邏輯器件(CPLD)快速卷積法實(shí)現(xiàn)數(shù)字濾波器的設(shè)計(jì)??? 關(guān)鍵詞:CPLD 數(shù)字濾波器 信號(hào)處理

2009-06-20 14:23:56 1317

1317

摘要:介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實(shí)現(xiàn)。用CPLD設(shè)計(jì)雙端口RAM緩存、控制譯碼、時(shí)序邏輯電路,很好地解決了電路元件所占體積大、電路復(fù)雜、不能實(shí)現(xiàn)在線

2009-06-20 15:12:07 1203

1203

高速數(shù)據(jù)采集系統(tǒng)中精確時(shí)標(biāo)的CPLD實(shí)現(xiàn)方法

本文介紹一種利用復(fù)雜可編程邏輯器件給高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時(shí)間標(biāo)簽的方法,并

2009-07-20 12:42:23 828

828 CPLD邏輯電路 圖6是CPLD內(nèi)部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設(shè)計(jì)采用原理圖輸入法,主要功能是對(duì)MUX的通道進(jìn)行選擇、對(duì)A/D轉(zhuǎn)換器進(jìn)

2009-11-13 12:04:13 2982

2982

基于MPC860的HDLC通道驅(qū)動(dòng)程序的設(shè)計(jì)與實(shí)現(xiàn)

摘 要: 闡述了MPC860芯片及其SCC接口的基本工作原理,介紹了在SCC通道上實(shí)現(xiàn)HDLC協(xié)議的基本設(shè)計(jì)思想及具體實(shí)現(xiàn),并給出了

2010-01-14 10:41:56 1246

1246

CPLD,CPLD是什么意思

CPLD是指結(jié)構(gòu)比較復(fù)雜的可編程邏輯器件,它包括下述輸出宏單元結(jié)構(gòu):

(1)可編程I/O 允

2010-03-26 17:08:50 3555

3555 基于FPGA和CPLD數(shù)字邏輯實(shí)現(xiàn)ADC技術(shù)

數(shù)字系統(tǒng)的設(shè)計(jì)人員擅長(zhǎng)在其印制電路板上用FPGA和CPLD將各種處理器、存儲(chǔ)器和標(biāo)準(zhǔn)的功能元件粘合在一起來(lái)實(shí)現(xiàn)

2010-05-25 09:39:10 1844

1844

MPC8260有兩個(gè)CPU:嵌入的PowerPC內(nèi)核和通信處理模塊(CPM)。由于CPM分擔(dān)了嵌入式PowerPC核的外圍工作任務(wù),這種雙處理器體系結(jié)構(gòu)功耗要低于傳統(tǒng)的體系結(jié)構(gòu)的處理器。

2011-03-17 11:22:45 4011

4011 提出了以 MPC850 微處理器和FPGA 芯片為核心的非對(duì)稱數(shù)字用戶線路技術(shù)(AD2SL) 的實(shí)現(xiàn)方案,解決了系統(tǒng)的局端和用戶端的接入問(wèn)題. 微處理器MPC850 完成 ADSL 系統(tǒng)的控制和管理,大規(guī)模FPGA 芯片

2011-06-08 18:00:49 35

35 編碼輸入,帶同步功能可接手輪,多個(gè)模塊組網(wǎng)工作可達(dá)120軸,任意兩軸直線插補(bǔ),任意兩軸圓弧插補(bǔ),自帶基本邏輯判斷能力,指令自動(dòng)緩存式連續(xù)執(zhí)行,簡(jiǎn)單的18條指令配合可實(shí)現(xiàn)強(qiáng)大的運(yùn)動(dòng)控制功能。

2016-03-15 09:58:49 24

24 復(fù)雜可編程邏輯器件_CPLD_在DSP交流電機(jī)控制系統(tǒng)中的應(yīng)用

2016-04-15 18:06:15 9

9 PC與歐姆龍CPM1A系列PLC的通信協(xié)議,感興趣的小伙伴們可以瞧一瞧。

2016-10-26 15:55:29 28

28 可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

2016-12-11 23:38:39 0

0 在CPLD中用UART邏輯實(shí)現(xiàn)高速異步串行通信

2017-01-24 16:54:24 12

12 基于CPLD的SGPIO總線實(shí)現(xiàn)及應(yīng)用

2017-01-24 16:00:51 78

78 數(shù)字系統(tǒng)的設(shè)計(jì)人員擅長(zhǎng)在其印制電路板上用FPGA和CPLD將各種處理器、存儲(chǔ)器和標(biāo)準(zhǔn)的功能元件粘合在一起來(lái)實(shí)現(xiàn)數(shù)字設(shè)計(jì)。除了這些數(shù)字功能之外,F(xiàn)PGA和CPLD還可以使用LVDS輸入、簡(jiǎn)單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實(shí)現(xiàn)共模功能,從而構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。

2018-04-26 11:53:00 1765

1765

FPGA LAB和CPLD的LAB設(shè)計(jì)不同。CPLD LAB由宏單元構(gòu)成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構(gòu)成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來(lái)可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來(lái)提高性能,減少邏輯資源的浪費(fèi)。

2018-04-17 17:02:00 2494

2494

CPLD通常用于實(shí)現(xiàn)前面提到的簡(jiǎn)單組合邏輯功能,并負(fù)責(zé)“引導(dǎo)”FPGA以及控制整個(gè)電路板的復(fù)位和引導(dǎo)順序。

2018-09-27 11:56:01 7180

7180 本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Verilog-HDL做CPLD設(shè)計(jì)的時(shí)序邏輯電路的實(shí)現(xiàn)。

2018-12-12 16:25:46 11

11 介紹了一種用CPLD(復(fù)雜可編程邏輯器件)作為核心控制電路的測(cè)試系統(tǒng)接口,通過(guò)時(shí)cPLD和竹L電路的比較及cPLD在系統(tǒng)中實(shí)現(xiàn)的強(qiáng)大功能,論述了CPLD在測(cè)試系統(tǒng)接口中應(yīng)用的可行性和優(yōu)越性,簡(jiǎn)單介紹

2019-01-01 16:18:00 2544

2544

對(duì)于CPLD/FPGA初學(xué)者而言,如何實(shí)現(xiàn)雙向信號(hào)往往是個(gè)難題。duoduo 當(dāng)年初接觸CPLD/FPGA的時(shí)候也為這個(gè)問(wèn)題頭疼過(guò)。讓我們透過(guò)下面這個(gè)簡(jiǎn)單的例子看看CPLD/FPGA設(shè)計(jì)中如何實(shí)現(xiàn)雙向信號(hào)。

2019-06-11 16:13:51 15

15 CPLD實(shí)現(xiàn)Watchdog 功能,通過(guò)對(duì)寄存器的操作,實(shí)現(xiàn)Watchdog各項(xiàng)功能。CPLD 內(nèi)部Watchdog 模塊邏輯框圖如下所示。

2019-06-12 15:59:33 14

14 實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定可靠,但往往具體應(yīng)用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費(fèi)專用芯片的資源,而且也

2020-03-20 09:54:04 2020

2020

本文主要介紹CPLD和FPGA的基本結(jié)構(gòu)。 CPLD是復(fù)雜可編程邏輯器件(Complex Programable Logic Device)的簡(jiǎn)稱,F(xiàn)PGA是現(xiàn)場(chǎng)可編程門陣列(Field

2020-09-25 14:56:33 14416

14416

可編程邏輯器件rPGA(現(xiàn)場(chǎng)可編程門陣列)和CPLD(復(fù)雜可編程邏輯器件)越來(lái)越多的應(yīng)用于數(shù)字信號(hào)處理領(lǐng)域,與傳統(tǒng)的ASIC(專用集成電路和DSP數(shù)字信號(hào)處理器)相比,基于FPGA和CPLD實(shí)現(xiàn)

2021-02-01 10:33:06 19

19 可編程邏輯陣列fpga和cpld說(shuō)明。

2021-03-30 09:30:05 25

25 CPM功能塊使用入門免費(fèi)下載。

2021-05-09 09:58:42 27

27 FPGA CPLD中的Verilog設(shè)計(jì)小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計(jì)小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 37

37 電子發(fā)燒友網(wǎng)站提供《Compact系列CPLD可配置邏輯模塊(CLM)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 10:06:25 4

4 一種使用分立邏輯芯片代替CPLD的解決方案

2022-11-01 08:27:25 1

1 with DMA and CCIX Rev. 1.0)的 QDMA IP 中選中,CPM 內(nèi)嵌在CIPS (Control Interfaces and Processing System) 中。不同系

2023-05-10 09:47:13 3229

3229

可編程邏輯包括 PAL、GAL、PLD 等。通過(guò)不斷發(fā)展,它已經(jīng)發(fā)展成為現(xiàn)在的CPLD/FPGA。CPLD(復(fù)雜可編程邏輯器件)和FPGA(現(xiàn)場(chǎng)可編程門陣列)的功能基本相同,只是實(shí)現(xiàn)原理略有不同。當(dāng)

2023-07-03 14:33:38 10709

10709

RC復(fù)位電路中R如何影響芯片復(fù)位? RC復(fù)位電路是常見的一種復(fù)位電路,它通過(guò)串聯(lián)一個(gè)電阻和一個(gè)電容元件來(lái)實(shí)現(xiàn)對(duì)芯片的復(fù)位功能。在RC電路中,電容元件起到存儲(chǔ)電荷、延遲釋放電荷的作用,而電阻元件起到

2023-10-25 11:07:51 2247

2247 其實(shí)這個(gè)分頻時(shí)鐘切換很簡(jiǎn)單,根本不需要額外的切換電路。一個(gè)共用的計(jì)數(shù)器,加一點(diǎn)控制邏輯,就可以了,而且可以實(shí)現(xiàn)2到16任意整數(shù)分頻率之間的無(wú)縫切換。

2023-12-14 15:28:56 1448

1448

HT7044A 是一種復(fù)位電路芯片,常用于電子設(shè)備中實(shí)現(xiàn)對(duì)系統(tǒng)的復(fù)位功能。復(fù)位是一項(xiàng)重要的功能,用于將整個(gè)系統(tǒng)恢復(fù)到初始狀態(tài),以確保系統(tǒng)在啟動(dòng)和運(yùn)行時(shí)的可靠性和穩(wěn)定性。在本文中,我們將詳細(xì)介紹

2024-01-04 11:24:41 3069

3069 CPLD和FPGA都是由邏輯陣列模塊構(gòu)成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數(shù)量的增加,呈指數(shù)

2024-01-23 09:17:04 2281

2281 數(shù)字電路中寄存器和 RAM 在上電之后默認(rèn)的狀態(tài)和數(shù)據(jù)是不確定的,如果有復(fù)位,我們可以把寄存器復(fù)位到初始狀態(tài),RAM 的數(shù)據(jù)可以通過(guò)復(fù)位來(lái)觸發(fā) RAM 初始化程序邏輯如果進(jìn)入了錯(cuò)誤的狀態(tài)。

2024-03-13 12:16:38 3194

3194

在CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)中,邏輯塊是實(shí)現(xiàn)邏輯功能的核心模塊。它主要由可編程乘積項(xiàng)陣列(即與陣列)、乘積項(xiàng)分配、宏單元三部分組成。

2024-04-07 17:37:54 4080

4080

電子發(fā)燒友網(wǎng)站提供《使用離散邏輯的可配置定時(shí)復(fù)位.pdf》資料免費(fèi)下載

2024-09-03 10:16:26 1

1 隨著電子技術(shù)的快速發(fā)展,可編程邏輯器件在各個(gè)領(lǐng)域中的應(yīng)用越來(lái)越廣泛。CPLD作為一種靈活、成本效益高的解決方案,被廣泛應(yīng)用于多種電子系統(tǒng)設(shè)計(jì)中。 CPLD概述 CPLD是一種可編程邏輯器件,它通過(guò)

2025-01-23 09:48:12 2314

2314 在現(xiàn)代電子設(shè)計(jì)領(lǐng)域,復(fù)雜可編程邏輯器件(CPLD)因其靈活性、成本效益和快速開發(fā)周期而在嵌入式系統(tǒng)中扮演著重要角色。 1. CPLD簡(jiǎn)介 CPLD是一種集成電路,其內(nèi)部包含可編程邏輯塊和可編程互連

2025-01-23 09:50:33 1932

1932 器件。它具有中等規(guī)模的邏輯資源和較高的集成度,適用于中小型邏輯設(shè)計(jì)。 CPLD的優(yōu)勢(shì) 1. 集成度高 CPLD具有較高的集成度,可以在一個(gè)芯片上實(shí)現(xiàn)復(fù)雜的邏輯功能,減少了外部元件的使用,從而降低了系統(tǒng)成本和復(fù)雜性。 2. 編程靈活性 CPLD可以通過(guò)編程來(lái)實(shí)現(xiàn)不同的邏輯功能,這使得它們可以被用于多種不同

2025-01-23 09:54:36 2222

2222 的應(yīng)用。 CPLD的優(yōu)勢(shì) 靈活性 :CPLD可以根據(jù)汽車制造商的具體需求進(jìn)行定制,實(shí)現(xiàn)不同的邏輯功能。 低功耗 :CPLD在設(shè)計(jì)時(shí)就考慮到了功耗問(wèn)題,適合用于對(duì)功耗有嚴(yán)格要求的汽車電子系統(tǒng)。 快速響應(yīng) :CPLD的邏輯門延遲小,能夠快速響應(yīng)外部信號(hào)變化

2025-01-23 10:05:30 1319

1319

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論