摘 要: 隨著VLSI的集成度越來越高,設(shè)計(jì)也越趨復(fù)雜。傳統(tǒng)的設(shè)計(jì)方法如原理圖輸入、HDL語言描述在進(jìn)行復(fù)雜系統(tǒng)設(shè)計(jì)時(shí),設(shè)計(jì)效率往往比較低。特別是在算法由軟件轉(zhuǎn)化為硬件的環(huán)節(jié)上,傳統(tǒng)的設(shè)計(jì)方法的效率不是很高,設(shè)計(jì)者往往要耗費(fèi)大量的時(shí)間和精力手工進(jìn)行算法的轉(zhuǎn)化。為解決這些問題,一種新的系統(tǒng)級(jí)的設(shè)計(jì)方法SYSTEM C 被提出。SYSTEM C是一種方法,也是一個(gè)C++庫,用SYSTEM C可以很方便地實(shí)現(xiàn)一個(gè)軟件算法的硬件實(shí)現(xiàn),以及完成一個(gè)系統(tǒng)級(jí)的設(shè)計(jì)。

關(guān)鍵詞: System C;硬件描述語言;FPGA

一、概述

隨著VLSI的集成度越來越高,設(shè)計(jì)也越趨復(fù)雜。一個(gè)系統(tǒng)的設(shè)計(jì)往往不僅需要硬件設(shè)計(jì)人員的參與,也需要有軟件設(shè)計(jì)人員的參與。軟件設(shè)計(jì)人員與硬件設(shè)計(jì)人員之間的相互協(xié)調(diào)就變的格外重要,它直接關(guān)系到工作的效率以及整個(gè)系統(tǒng)設(shè)計(jì)的成敗。傳統(tǒng)的設(shè)計(jì)方法沒有使軟件設(shè)計(jì)工作與硬件設(shè)計(jì)工作協(xié)調(diào)一致,而是將兩者的工作割裂開來。軟件算法的設(shè)計(jì)人員在系統(tǒng)設(shè)計(jì)后期不能為硬件設(shè)計(jì)人員的設(shè)計(jì)提供任何的幫助。同時(shí)現(xiàn)在有些大規(guī)模集成電路設(shè)計(jì)中往往帶有DSP Core或其它CPU Core。這些都使得單純地用原理圖或硬件描述語言來設(shè)計(jì)、仿真這么復(fù)雜的系統(tǒng)變得十分困難。System C就是在這些矛盾的背景下提出的。它的出現(xiàn)為復(fù)雜的系統(tǒng)設(shè)計(jì)提供了一條有效的解決途徑。

System C 是由 Synospy Inc. 提出的,目前最新的版本為V2.0。它提出的目的就是以一種系統(tǒng)設(shè)計(jì)的思想進(jìn)行系統(tǒng)設(shè)計(jì)。它將軟件算法與硬件實(shí)現(xiàn)很好的結(jié)合在一起,提高了整個(gè)系統(tǒng)設(shè)計(jì)的效率和正確性。

System C 是一個(gè)C++ 庫,也是一種使設(shè)計(jì)者可以有效地設(shè)計(jì)出一個(gè)軟件算法的準(zhǔn)確循環(huán)模型,硬件結(jié)構(gòu)以及系統(tǒng)級(jí)設(shè)計(jì)的方法。設(shè)計(jì)者可以用System C開發(fā)工具或在標(biāo)準(zhǔn)C++開發(fā)工具中加如System C庫制作系統(tǒng)級(jí)模型,快速地仿真和優(yōu)化設(shè)計(jì),以及研究不同的算法,并且為硬件和軟件設(shè)計(jì)人員提供一個(gè)設(shè)計(jì)系統(tǒng)的可執(zhí)行規(guī)范。可執(zhí)行規(guī)范本質(zhì)上是一個(gè)C++程序,它顯示了和設(shè)計(jì)系統(tǒng)同樣的性能,為軟件設(shè)計(jì)人員和硬件設(shè)計(jì)人員提供了一個(gè)設(shè)計(jì)的標(biāo)準(zhǔn)。

System C 庫提供了創(chuàng)造系統(tǒng)結(jié)構(gòu)模型的必須結(jié)構(gòu),包括那些在C++沒有的功能如硬件時(shí)序,并行和觸發(fā)功能。C++這種面對(duì)象語言提供了通過增加類來擴(kuò)展語言的能力,而這種能力是C語言所不具備的。因此,System C使用大家熟悉的C++語言和開發(fā)工具。

?

二、SYSTEM C的特點(diǎn)

System C 支持對(duì)硬件和軟件的聯(lián)合設(shè)計(jì),支持描述一個(gè)既包含硬件部分也包含軟件部分的復(fù)雜系統(tǒng)結(jié)構(gòu)。它也支持對(duì)接口的描述,有以下幾個(gè)顯著的特點(diǎn):

1.System C可以為軟件設(shè)計(jì)人員和硬件設(shè)計(jì)人員提供一個(gè)系統(tǒng)的可執(zhí)行規(guī)范。設(shè)計(jì)人員使用該可執(zhí)行規(guī)范可以避免設(shè)計(jì)中矛盾和錯(cuò)誤的產(chǎn)生,并確保設(shè)計(jì)的完備性。這是應(yīng)為在設(shè)計(jì)可執(zhí)行規(guī)范時(shí),系統(tǒng)設(shè)計(jì)者必須設(shè)計(jì)出也一個(gè)和系統(tǒng)具有同樣工作狀態(tài)的程序,通過這個(gè)程序可以發(fā)掘出潛在的矛盾和錯(cuò)誤,并將這些矛盾和錯(cuò)誤消除在整個(gè)設(shè)計(jì)的開始階段,而不是在整個(gè)系統(tǒng)進(jìn)行調(diào)試階段才發(fā)現(xiàn)和解決這些矛盾和錯(cuò)誤。這個(gè)程序還可以幫助設(shè)計(jì)者確保整個(gè)系統(tǒng)設(shè)計(jì)的完備性。

2.設(shè)計(jì)人員利用這個(gè)可執(zhí)行的系統(tǒng)規(guī)范,還可以發(fā)現(xiàn)設(shè)計(jì)中概念模糊的地方。無論什么時(shí)候,設(shè)計(jì)人員對(duì)設(shè)計(jì)產(chǎn)生疑惑,就可以運(yùn)行這個(gè)可執(zhí)行程序以明確在這個(gè)問題上系統(tǒng)設(shè)計(jì)人員是如何處理的,從而確保系統(tǒng)設(shè)計(jì)的正確性。而現(xiàn)在的設(shè)計(jì)方法不能使設(shè)計(jì)人員方便迅速的解決這些疑惑。甚至這些疑惑是系統(tǒng)設(shè)計(jì)人員也不曾考慮過,這可能導(dǎo)致系統(tǒng)要重新進(jìn)行設(shè)計(jì)。

3.在系統(tǒng)設(shè)計(jì)被實(shí)現(xiàn)以前,設(shè)計(jì)人員還可以通過用System C設(shè)計(jì)的系統(tǒng)可執(zhí)行規(guī)范來驗(yàn)證整個(gè)系統(tǒng)設(shè)計(jì)。這樣可以避免由于在系統(tǒng)設(shè)計(jì)上的失誤,而使系統(tǒng)實(shí)現(xiàn)不能達(dá)到要求。現(xiàn)在的設(shè)計(jì)方法不能提供這樣的手段在設(shè)計(jì)完成前進(jìn)行系統(tǒng)的驗(yàn)證,對(duì)系統(tǒng)的驗(yàn)證必須是在系統(tǒng)設(shè)計(jì)完后。即使在完成前進(jìn)行驗(yàn)證,由于不能完全模擬實(shí)際系統(tǒng)的工作,其結(jié)果也只能作為一種參考。

4.System C設(shè)計(jì)的可執(zhí)行規(guī)范所使用的TESTBENCH文件可以通過小范圍的修改或直接用在實(shí)現(xiàn)后的系統(tǒng)仿真。這就為設(shè)計(jì)實(shí)現(xiàn)人員帶來很大的好處,他們不必花很多的時(shí)間去編寫用來驗(yàn)證實(shí)現(xiàn)后系統(tǒng)正確性的TESTBENCH文件。而現(xiàn)在采用的設(shè)計(jì)方法所使用的TESTBENCH文件卻沒有提供這樣的便利條件。這是應(yīng)為軟件設(shè)計(jì)人員和硬件設(shè)計(jì)人員兩者的設(shè)計(jì)思想和設(shè)計(jì)手段都是不同的,一個(gè)軟件設(shè)計(jì)人員所使用的TESTBENCH文件并不能被硬件設(shè)計(jì)人員使用,甚至不能給硬件設(shè)計(jì)人員任何幫助。

三、SYSTEM C設(shè)計(jì)與傳統(tǒng)設(shè)計(jì)比較

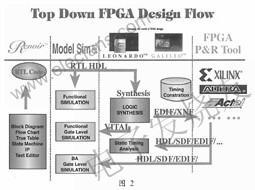

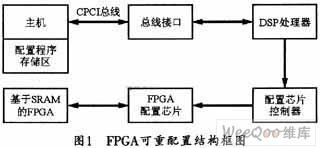

現(xiàn)在的系統(tǒng)設(shè)計(jì)一般是由系統(tǒng)工程師用C語言或C++語言設(shè)計(jì)出一個(gè)系統(tǒng)模型,并在系統(tǒng)級(jí)層次上檢驗(yàn)概念和算法。當(dāng)這些概念和算法被檢驗(yàn)為正確無誤時(shí),C/C++模塊被分解為功能相對(duì)獨(dú)立的子模塊。這些相對(duì)對(duì)立的子模塊由硬件設(shè)計(jì)人員手工地轉(zhuǎn)化為VHDL或Verilog語言用以硬件實(shí)現(xiàn)。這一個(gè)設(shè)計(jì)流程被顯示在圖1中。

圖1

從圖1所示的設(shè)計(jì)流程中我們可以發(fā)現(xiàn)以下幾個(gè)問題:

1.人工將C\C++程序轉(zhuǎn)換為HDL程序容易產(chǎn)生錯(cuò)誤。在現(xiàn)在的這種設(shè)計(jì)方法中,系統(tǒng)工程師先按期望的設(shè)計(jì)要求設(shè)計(jì)出一個(gè)C模塊,并驗(yàn)證這個(gè)模塊使其達(dá)到期望的設(shè)計(jì)要求。然后系統(tǒng)工程師所設(shè)計(jì)的C模塊被硬件設(shè)計(jì)人員手工轉(zhuǎn)換為HDL模塊。這個(gè)轉(zhuǎn)換過程不僅容易產(chǎn)生錯(cuò)誤,而且還很浪費(fèi)時(shí)間。這是因?yàn)镃\C++語言和HDL語言有著顯著的區(qū)別。首先,HDL的處理方式比C\C++的復(fù)雜。C\C++程序采用順序執(zhí)行的處理方式,而HDL程序中既有順序執(zhí)行也有并行執(zhí)行的處理方式。要將C\C++程序轉(zhuǎn)化為HDL程序必然要引入一些控制信號(hào),由這些信號(hào)控制HDL程序的運(yùn)行,但這樣也容易產(chǎn)生錯(cuò)誤。其次,C\C++語言不涉及到時(shí)序關(guān)系。由于C\C++語言不支持對(duì)時(shí)序的描述,系統(tǒng)工程師設(shè)計(jì)的系統(tǒng)模型只是驗(yàn)證了概念和算法,而只能對(duì)時(shí)間耗費(fèi)上有一個(gè)大概的估計(jì)。這就使得硬件實(shí)現(xiàn)時(shí),為滿足系統(tǒng)在時(shí)間上的要求,硬件設(shè)計(jì)人員必須對(duì)軟件算法進(jìn)行一定的改造或優(yōu)化。而這些改造或優(yōu)化也有可能引入各種錯(cuò)誤。

2.系統(tǒng)模塊和HDL模塊間缺乏聯(lián)系。當(dāng)系統(tǒng)模塊被轉(zhuǎn)換為HDL模塊后,HDL模塊成為整個(gè)系統(tǒng)設(shè)計(jì)的焦點(diǎn)。為適應(yīng)硬件實(shí)現(xiàn)的特點(diǎn),硬件設(shè)計(jì)人員會(huì)更改系統(tǒng)設(shè)計(jì)人員的設(shè)計(jì),但這種更改只是在HDL模塊中進(jìn)行,而系統(tǒng)設(shè)計(jì)人員設(shè)計(jì)的C模塊并沒有因此更改。這就使得系統(tǒng)工程師設(shè)計(jì)的C模塊和當(dāng)前硬件設(shè)計(jì)人員設(shè)計(jì)的HDL模塊缺乏必要的聯(lián)系。當(dāng)硬件設(shè)計(jì)人員遇到概念模糊或理解錯(cuò)誤的地方時(shí),往往不能馬上從C模塊中得到明確的解答。此時(shí),C模塊的設(shè)計(jì)人員也不一定能為HDL設(shè)計(jì)人員提供有效的幫助。

3.多系統(tǒng)測(cè)試。不但C模塊要轉(zhuǎn)換為HDL模塊,對(duì)C模塊的測(cè)試也要人工轉(zhuǎn)換為在HDL環(huán)境下的測(cè)試。這種轉(zhuǎn)換也很復(fù)雜,而且浪費(fèi)時(shí)間。HDL設(shè)計(jì)人員是根據(jù)他所設(shè)計(jì)的HDL模塊和系統(tǒng)要求來設(shè)計(jì)TESTBENCH,這使得硬件設(shè)計(jì)人員不可能利用軟件設(shè)計(jì)人員所使用的測(cè)試文件。同時(shí),HDL人員要設(shè)計(jì)出一個(gè)好的TESTBENCH也需要比較長(zhǎng)的時(shí)間。

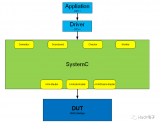

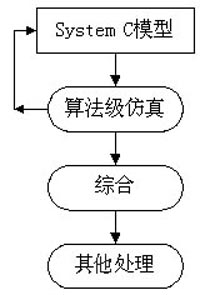

為解決在現(xiàn)在設(shè)計(jì)流程中所帶來的種種弊端,一種全新的設(shè)計(jì)流程被提出,這就是System C設(shè)計(jì)流程。它能很好的解決上面所提到的各種設(shè)計(jì)弊端,大大提高設(shè)計(jì)效率。圖2是System C的硬件設(shè)計(jì)流程。

圖2

這種設(shè)計(jì)方法與現(xiàn)在常用的設(shè)計(jì)方法相比有很多優(yōu)點(diǎn):

1.精煉的設(shè)計(jì)方法。使用System C設(shè)計(jì)系統(tǒng),系統(tǒng)設(shè)計(jì)人員不必花費(fèi)很大的精力將整個(gè)系統(tǒng)設(shè)計(jì)由C語言描述轉(zhuǎn)換為HDL描述。系統(tǒng)設(shè)計(jì)人員可以通過在C模塊中很小的區(qū)域范圍內(nèi)加入必要的硬件和時(shí)序結(jié)構(gòu)描述,從而將C模塊方便準(zhǔn)確地轉(zhuǎn)化為一個(gè)有效的硬件設(shè)計(jì),而避免將另行設(shè)計(jì)一個(gè)硬件模塊。利用System C設(shè)計(jì)方法,設(shè)計(jì)人員可以很輕松地實(shí)現(xiàn)一個(gè)設(shè)計(jì)的更改,或在優(yōu)化算法時(shí)檢測(cè)出一些設(shè)計(jì)錯(cuò)誤并及時(shí)修改。

2.單一語言書寫。使用System C設(shè)計(jì)系統(tǒng),整個(gè)設(shè)計(jì)都用一種語言設(shè)計(jì)系統(tǒng),降低了對(duì)設(shè)計(jì)人員的要求,減少了語言轉(zhuǎn)換時(shí)所造成的錯(cuò)誤。這一優(yōu)點(diǎn)也使得設(shè)計(jì)人員可以在一個(gè)比較高的層次上進(jìn)行系統(tǒng)模塊設(shè)計(jì)。在較高層次的設(shè)計(jì)會(huì)導(dǎo)致產(chǎn)生小的設(shè)計(jì)代碼,使設(shè)計(jì)和仿真的速度比傳統(tǒng)的設(shè)計(jì)方法要快很多。這一點(diǎn)是很顯著的。

?

四、SYSTEM C基本概念

1.模塊

模塊是System C設(shè)計(jì)中的基本設(shè)計(jì)單元。模塊可以使得設(shè)計(jì)者將一個(gè)復(fù)雜的系統(tǒng)分割為一些更小但易于管理的部分。System C模塊的功能和作用與HDL語言中的模塊是相類似的,這使得一位習(xí)慣于用HDL進(jìn)行設(shè)計(jì)的設(shè)計(jì)人員可以很容易的轉(zhuǎn)向用System C進(jìn)行設(shè)計(jì)。

模塊在System C中的關(guān)鍵字為SC_MODULE。緊跟著關(guān)鍵字后的是模塊的名稱,如SC_MODULE(fifo),這就定義了一個(gè)叫fifo的模塊。定義的模塊也可以像HDL語言一樣包含端口、信號(hào)、其它模塊、處理過程和結(jié)構(gòu)體,這些單元實(shí)現(xiàn)用以實(shí)現(xiàn)模塊的功能。通過端口可以將幾個(gè)模塊連接起來。

模塊被保存為.h文件。如果在一個(gè)模塊中調(diào)用其它模塊,只需像C++中引入庫一樣將要調(diào)用的模塊作為一個(gè)庫引入即可。

2.過程

模塊中的處理過程(process)類似于C語言中的子程序,與C語言中的子程序不同的的是它具有HDL語言中的觸發(fā)功能。處理過程(process)的具體工作部分被保存為.cpp文件。處理過程的調(diào)用類似于在C語言中子程序的調(diào)用。根據(jù)不同的要求,SystemC中有三種處理過程。

● Methods : SC_METHOD()

● Threads : SC_THREAD()

● Clock Threads : SC_CTHREAD()

SC_METHOD是用來描述組合邏輯,它由輸入信號(hào)的變化觸發(fā),但不能在兩次調(diào)用中保存控制狀態(tài)。并且在SC_METHOD中不能包含無限循環(huán)。由于組合邏輯有可能導(dǎo)致毛刺的產(chǎn)生,從而影響系統(tǒng)性能,所以SC_METHOD不易太復(fù)雜。 下面是一個(gè)簡(jiǎn)單的SC_METHOD例子:

SC_MODULE(example) {

sc_in

sc_out

void inverter();//處理過程聲明

SC_CTOR(example) {

SC_METHOD(inverter);

sensitive(din);//處理過程由輸入變化觸發(fā)

}

};

處理過程inverter如下:

void example::inverter() {

bool internal;

internal = din;//輸入數(shù)據(jù)取反后由輸出端口輸出

dout = ~internal;

}

SC_THREAD是最常用的處理過程,基本上可以用在任何地方。它是由輸入信號(hào)的變化觸發(fā),但與SC_METHOD不同的是它可以在兩次調(diào)用這保存控制狀態(tài)。它的功能類似于積存器的功能。SC_THREAD中可以包含有wait()函數(shù),這使得處理過程可以被掛起。

SC_CTHREAD是SC_THREAD的一種特殊情況。SC_CTHREAD能產(chǎn)生更好的綜合效果。SC_CTHREAD中可以使用wait()函數(shù)。在不同的狀態(tài)間加入wait()函數(shù),設(shè)計(jì)人員可以用SC_CTHREAD來實(shí)現(xiàn)狀態(tài)機(jī)。這種設(shè)計(jì)風(fēng)格是簡(jiǎn)便的而且容易理解。SC_CTHREAD只能由時(shí)鐘信號(hào)沿觸發(fā),而SC_THREAD可以由其它非時(shí)鐘信號(hào)觸發(fā)。如果在時(shí)鐘上跳邊觸發(fā),可以使用pos()函數(shù),反之用neg()。

為進(jìn)一步說明SC_CTHREAD,下面給出了一個(gè)SC_CTHREAD的例子。

SC_MODULE(example) {

sc_in_clk clock;//輸入時(shí)鐘

sc_in

sc_out

void invert();

SC_CTOR(example) {

SC_CTHREAD(toggler, clock.pos());//時(shí)鐘上升沿觸發(fā)

}

}

void example::invert() {

bool last = false;

for (;;) {

wait_until(trigger.delayed() == true);//等到下個(gè)時(shí)鐘上升沿 //且trigger=1再執(zhí)行

last = din; dout = last; wait();

last =~din; dout = last;wait();//下個(gè)上升沿才更改數(shù)據(jù)

}

}

3.端口與信號(hào)

與HDL語言相似,使用System C庫就可以在C程序中加入端口和信號(hào)。這些原先C語言中沒有的功能,使設(shè)計(jì)更復(fù)合硬件設(shè)計(jì)的要求。

模塊與模塊之間是通過端口信號(hào)加一聯(lián)系。只要兩個(gè)端口被連接在一起,信號(hào)就可以在它們之間進(jìn)行傳遞。對(duì)于這一點(diǎn)習(xí)慣用HDL進(jìn)行設(shè)計(jì)的設(shè)計(jì)人員是很容易理解和接受的,因?yàn)檫@和HDL中端口的功能是一樣的。 信號(hào)只是在一個(gè)模塊的內(nèi)部使用,這也是和HDL中信號(hào)的用法是一致的。 下面給出端口和信號(hào)聲明的例子。

sc_in<“類型”> din// 輸入端口din

sc_out<“類型”> dout// 輸出端口dout

sc_inout<“類型”> q// 輸入輸出端口q

sc_signal

4.?dāng)?shù)據(jù)類型

考慮到硬件設(shè)計(jì)的要求,System C中也加入了一些硬件設(shè)計(jì)中常用的數(shù)據(jù)類型。具體如下:

sc_int 有符號(hào)整數(shù)類型,最大有64個(gè)比特位。

sc_uint 無符號(hào)整數(shù)類型,最大有64個(gè)比特位。

sc_bigint 有符號(hào)整數(shù)類型,任意比特位,其最大比特位定義在

sc_constants.h中。

sc_biguint 無符號(hào)整數(shù)類型,任意比特位,其最大比特位定義在

sc_constants.h中。

sc_bit 二值數(shù)據(jù),單比特位。

sc_logic 四值數(shù)據(jù),單比特位。

sc_bv 二值數(shù)據(jù),任意比特位。

sc_lv 四值數(shù)據(jù),任意比特位。

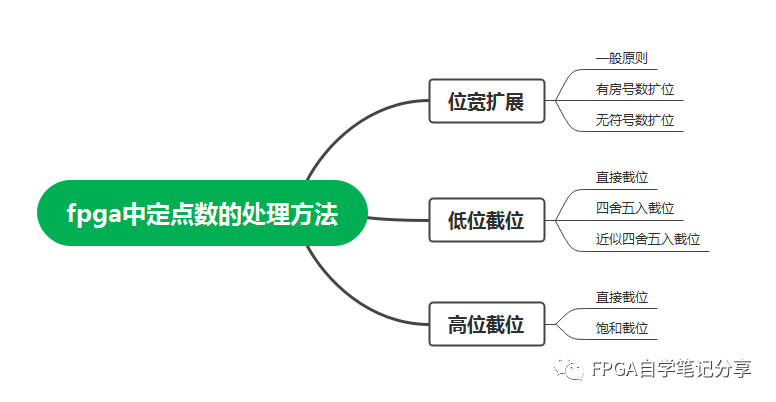

sc_fixed 參數(shù)固定的有符號(hào)定點(diǎn)數(shù)。

sc_ufixed 參數(shù)固定的無符號(hào)定點(diǎn)數(shù)。

sc_fix 參數(shù)不固定的有符號(hào)定點(diǎn)數(shù)。

sc_ufix 參數(shù)不固定的無符號(hào)定點(diǎn)數(shù)。

User defined structs 用戶自定義結(jié)構(gòu)

以上是一些System C的基本概念。

五、結(jié)論

System C是一種很有效的設(shè)計(jì)方法,它不僅可以幫助設(shè)計(jì)人員完成一個(gè)復(fù)雜的系統(tǒng)設(shè)計(jì),還可以避免傳統(tǒng)設(shè)計(jì)中的各種弊端,并提高設(shè)計(jì)人員的工作效率。它的這些優(yōu)點(diǎn)使System C在復(fù)雜的系統(tǒng)設(shè)計(jì)中大有作為。并且習(xí)慣用HDL的設(shè)計(jì)人員,可以很容易地轉(zhuǎn)到用System C設(shè)計(jì)。

?

參考文獻(xiàn)

1 SystemC v1.0 User Guide (http:\\www.systemc.org)

2 SystemC v2.0 User Guide (http:\\www.systemc.org

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論