??? 關(guān)鍵詞:VHDL 電路簡(jiǎn)化

??? 近年來(lái),隨著集成電路技術(shù)的發(fā)展,用傳統(tǒng)的方法進(jìn)行芯片或系統(tǒng)設(shè)計(jì)已不能滿足要求,迫切需要提高設(shè)計(jì)效率。在這樣的技術(shù)背景下,能大大降低設(shè)計(jì)難度的VHDL設(shè)計(jì)方法正越來(lái)越廣泛地被采用。但是VHDL設(shè)計(jì)是行為級(jí)的設(shè)計(jì)?所帶來(lái)的問(wèn)題是設(shè)計(jì)者的設(shè)計(jì)思考與電路結(jié)構(gòu)相脫節(jié)。設(shè)計(jì)者主要是根據(jù)VHDL的語(yǔ)法規(guī)則?對(duì)系統(tǒng)目標(biāo)的邏輯行為進(jìn)行描述?然后通過(guò)綜合工具進(jìn)行電路結(jié)構(gòu)的綜合、編譯、優(yōu)化,通過(guò)仿真工具進(jìn)行邏輯功能仿真和系統(tǒng)時(shí)延的仿真。實(shí)際設(shè)計(jì)過(guò)程中,由于每個(gè)工程師對(duì)語(yǔ)言規(guī)則、對(duì)電路行為的理解程度不同,每個(gè)人的編程風(fēng)格不同,往往同樣的系統(tǒng)功能,描述的方式是不一樣的,綜合出來(lái)的電路結(jié)構(gòu)更是大相徑庭。因此,即使最后綜合出的電路都能實(shí)現(xiàn)相同的邏輯功能,其電路的復(fù)雜程度和時(shí)延特性都會(huì)有很大的差別,甚至某些臃腫的電路還會(huì)產(chǎn)生難以預(yù)料的問(wèn)題。從這個(gè)問(wèn)題出發(fā),我們就很有必要深入討論在VHDL設(shè)計(jì)中如何簡(jiǎn)化電路結(jié)構(gòu),優(yōu)化電路設(shè)計(jì)的問(wèn)題。

??? 1 描述方法對(duì)電路結(jié)構(gòu)的影響

??? 用VHDL進(jìn)行設(shè)計(jì),其最終綜合出的電路的復(fù)雜程度除取決于設(shè)計(jì)要求實(shí)現(xiàn)的功能的難度外,還受設(shè)計(jì)工程師對(duì)電路的描述方法和對(duì)設(shè)計(jì)的規(guī)劃水平的影響。最常見(jiàn)的使電路復(fù)雜化的原因之一是設(shè)計(jì)中存在許多本不必要的類似LATCH的結(jié)構(gòu)。而且由于這些結(jié)構(gòu)通常都由大量的觸發(fā)器組成,不僅使電路更復(fù)雜,工作速度降低,而且由于時(shí)序配合的原因而導(dǎo)致不可預(yù)料的結(jié)果。例如對(duì)于同一譯碼電路有不同VHDL描述:

1: IF INDEX=″00000″ THEN

???? STEPSIZE<=″0000111″;?

???? WLSIF INDEX=″00001″ THEN

???? STEPSIZE<=″0001000″;?

???? LSIF INDEX=″00010″ THEN

???? STEPSIZE<=″0001001″;?

???? ……

???? ELSE

??????? STEPSIZE<=″0000000″;?

???? END IF;

2:STEPSIZE<=″0000111″ WHEN INDEX=″00000″ ELSE

??????????? ″0001000″ WHEN INDEX=″00001″ELSE

??????????? ″0001001″WHEN INDEX=″00010″ ELSE

???? ……

?????????? ″0000000″;?

??? 以上兩段程序描述了同一個(gè)譯碼電路。第二段程序由于WHEN......ELSE的語(yǔ)句不能生成鎖存器的結(jié)構(gòu)且ELSE后一定要有結(jié)果,所以不會(huì)有問(wèn)題,而第一個(gè)程序如果不加ELSE STEPSIZE〈=“0000000”這句,則會(huì)生成一個(gè)含有7位寄存器的結(jié)構(gòu),雖然都能實(shí)現(xiàn)相同的譯碼功能。但是電路復(fù)雜度會(huì)大增。而由于每個(gè)工程師的寫作習(xí)慣不同,有的喜歡用IF....ELSE的語(yǔ)句,有的喜歡用WHEN....ELSE的方式,而用IF....ELSE時(shí),如稍不注意,在描述不需要寄存器的電路時(shí)沒(méi)加ELSE,則會(huì)引起電路不必要的開銷。所以在VHDL設(shè)計(jì)中要慎用IF....ELSE這類能描述自身值代入的語(yǔ)句。

??? 2 設(shè)計(jì)規(guī)劃的優(yōu)劣直接影響電路結(jié)構(gòu)

??? 另一主要引起電路復(fù)雜化的原因是對(duì)設(shè)計(jì)規(guī)劃的不合理。雖然VHDL語(yǔ)言能從行為描述生成電路,但一個(gè)完整的設(shè)計(jì)一般來(lái)說(shuō)都不可能由直接描述設(shè)計(jì)的目標(biāo)功能來(lái)實(shí)現(xiàn)的。總要把設(shè)計(jì)分成若干部分,每一部分再分別描述其行為。這就涉及到如何劃分功能模塊的問(wèn)題,要求對(duì)設(shè)計(jì)了解的較深入,才能使劃分更有效,才能降低電路的復(fù)雜程度。例如我們?cè)O(shè)計(jì)一個(gè)時(shí)鐘源為1kHz,每32秒發(fā)出一組信號(hào)(共八組)的簡(jiǎn)單的控制器來(lái)說(shuō)。下面有兩種實(shí)現(xiàn)方法:

(1)用15位的記數(shù)器實(shí)現(xiàn)把輸入1kHz的時(shí)鐘分頻為1/32Hz,然后用這個(gè)作為時(shí)鐘驅(qū)動(dòng)一個(gè)3位的記數(shù)器,這個(gè)記數(shù)器的八個(gè)狀態(tài)分別通過(guò)一個(gè)3-8譯碼器發(fā)出所要求的信號(hào)。

?2?直接用18位的記數(shù)器把輸入的1kHz時(shí)鐘進(jìn)行分頻,再利用記數(shù)器的八個(gè)相距32秒的狀態(tài)來(lái)推動(dòng)一個(gè)12-8譯碼器來(lái)實(shí)現(xiàn)。

??? 對(duì)于如此的設(shè)計(jì)要求,VHDL程序分別如下所示:

1. 第一種設(shè)計(jì)方法的VHDL源程序

process(clk,cclk,count2)?

begin

if?(clk='1' and clk'event)then

??? count2<=count2 + 1;?

??? if(count2=″000000000000000″)then

????? cclk<='1';?

??? else

????? cclk<='0';?

??? end if;?

end if;?

end process;?

process(cclk,count3,ctemp)?

begin

if(cclk='1' and cclk'event)then

?? count3<=count3 +1;?

?? if(count3=″000″)then

????? ctemp<=″00000001″;?

?? elsif(count3=″001″)then

????? ctemp<=″00000010″;?

?? elsif(count3=″010″)then

????? ctemp<=″00000100″;?

?? elsif(count3=″011″)then

????? ctemp<=″00001000″;?

?? elsif(count3=″100″)then

????? ctemp<=″00010000″;?

?? elsif(count3=″101″)then

????? ctemp<=″00100000″;?

?? elsif(count3=″110″)then

????? ctemp<=″01000000″;?

?? elsif(count3=″111″)then

???? ctemp<=″10000000″;?

?? else

???? ctemp<=″00000000″;?

?? end if;?

end if;?

end process;?

2. 第二種設(shè)計(jì)方法的VHDL源程序

process(clk,ctemp,count)

begin

if(clk='1' and clk'event)then

?? count<=count + 1;?

?? if(count=″00000000000000000″)then

????? ctemp<=″00000001″;?

?? elsif(count=″001000000000000000″)then

????? ctemp<=″00000010″;?

?? elsif(count=″010000000000000000″)then

????? ctemp<=″00000100″;?

?? elsif(count=″011000000000000000″)then

????? ctemp<=″00001000″;?

?? elsif(count=″100000000000000000″)then

????? ctemp<=″00010000″;?

?? elsif(count=″101000000000000000″)then

????? ctemp<=″00100000″;?

?? elsif(count=″110000000000000000″)then

????? ctemp<=″01000000″;?

?? elsif(count=″111000000000000000″)then

????? ctemp<=″10000000″;?

?? end if;?

end if;?

end if;?

end peocess;?

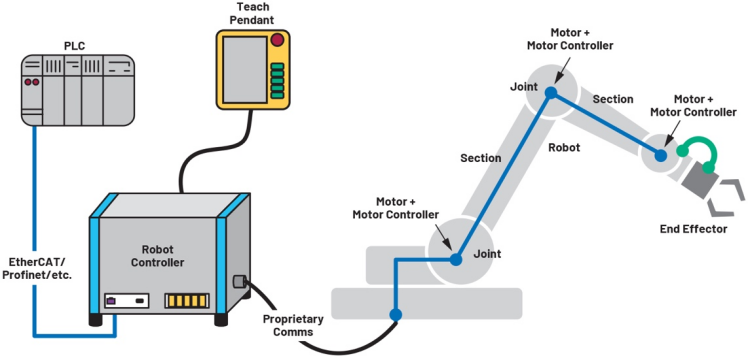

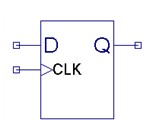

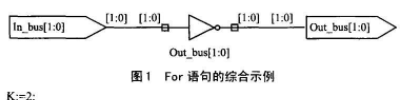

??? 對(duì)于第一種的程序可以綜合出的電路如圖1所示。

??? 該電路用一個(gè)15位的加法器和寄存器組成一個(gè)15位的記數(shù)器。在記數(shù)器記完一周回到“000000000000000”時(shí),通過(guò)后面的15輸入的與非門和一位的觸發(fā)器就可以實(shí)現(xiàn)同步的進(jìn)行215次分頻,同步輸出32Hz的時(shí)鐘CCLK。CCLK再驅(qū)動(dòng)一8位的移位寄存器,便可實(shí)現(xiàn)每32秒輸出一信號(hào)。

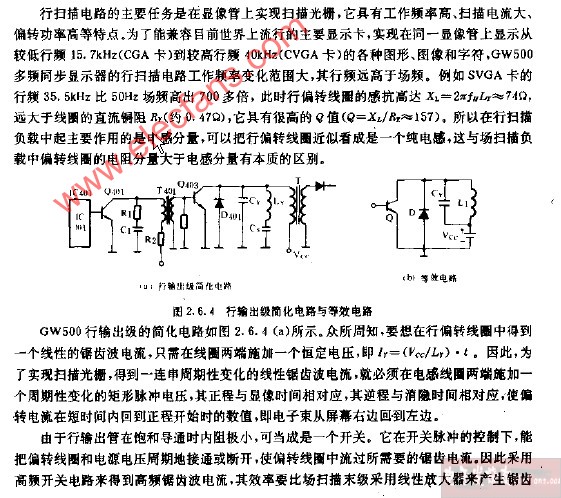

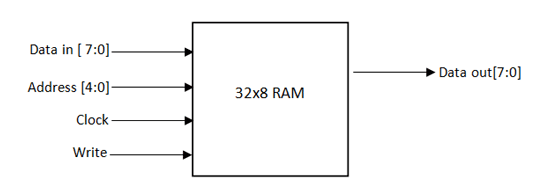

??? 而用第二種的程序設(shè)計(jì)綜合出的電路如圖2所示。

而用第二種的程序設(shè)計(jì)綜合出的電路如圖2所示。

??? 圖2所示的電路用一個(gè)18位的加法器和寄存器組成一個(gè)18位的記數(shù)器。后接了8個(gè)18輸入的邏輯門和8輸入的或門。輸入的1kHz時(shí)鐘經(jīng)過(guò)記數(shù)器被分頻,其中有八個(gè)相隔32Hz的記數(shù)狀態(tài),邏輯門就負(fù)責(zé)把這八狀態(tài)譯碼成所需的八組信號(hào)。譯碼后的數(shù)據(jù)通過(guò)選擇器輸出到8位的觸發(fā)器,以實(shí)現(xiàn)同步輸出。還有個(gè)鎖存器,是用來(lái)保持輸出信號(hào)不變,在八個(gè)狀態(tài)中的從一個(gè)狀態(tài)變到下一個(gè)之前,保持前一個(gè)的數(shù)值。選擇器當(dāng)邏輯門輸出新的數(shù)據(jù)時(shí)讓其輸出數(shù)據(jù)通過(guò),在新數(shù)據(jù)到來(lái)之前輸出鎖存器的數(shù)據(jù)。

??? 以上兩種方法都能實(shí)現(xiàn)相同的邏輯功能,但圖2所示的方法由于運(yùn)用了較少位數(shù)的記數(shù)器,所用的邏輯門也較簡(jiǎn)單,而且還少用了多路選擇器和鎖存器資源,所以綜合出來(lái)的電路較簡(jiǎn)單,以XILINX

?? Spartan S05 -3 芯片為例。第一種方法占用芯片CLB的12%,其中FMAPS為9%,最高工作速度為82Hz。而第二種方法占用了15%的CLB,F(xiàn)MAPS占用15%,最高工作速度只有69.9MHz。在這一個(gè)簡(jiǎn)單的設(shè)計(jì)之中就能省20%的電路,提高12.1MHz的工作速度,由此可見(jiàn)科學(xué)的劃分設(shè)計(jì)對(duì)降低電路復(fù)雜程度的重要意義。

Spartan S05 -3 芯片為例。第一種方法占用芯片CLB的12%,其中FMAPS為9%,最高工作速度為82Hz。而第二種方法占用了15%的CLB,F(xiàn)MAPS占用15%,最高工作速度只有69.9MHz。在這一個(gè)簡(jiǎn)單的設(shè)計(jì)之中就能省20%的電路,提高12.1MHz的工作速度,由此可見(jiàn)科學(xué)的劃分設(shè)計(jì)對(duì)降低電路復(fù)雜程度的重要意義。

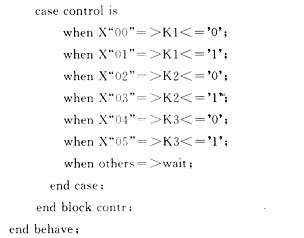

??? 3 邏輯設(shè)計(jì)對(duì)電路結(jié)構(gòu)的影響

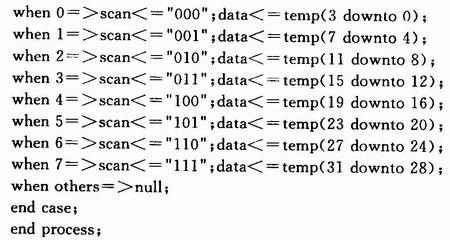

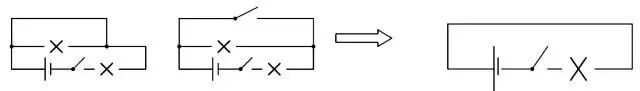

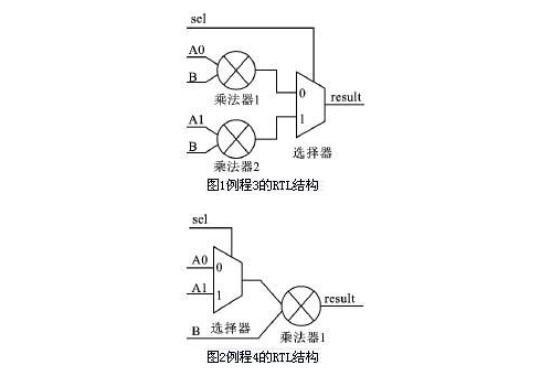

??? 還有一個(gè)使電路復(fù)雜化的原因是邏輯電路的輸入項(xiàng)太多以致需占用過(guò)多的面積。我們從圖3和圖4兩個(gè)相同功能的邏輯電路和他們對(duì)應(yīng)的VHDL描述來(lái)分析。

??? 比較兩圖可知,圖3是二級(jí)邏輯門,每個(gè)輸入信號(hào)與不只一個(gè)邏輯門相連,圖4是三級(jí)的邏輯門,每個(gè)輸入信號(hào)只與一邏輯門相連。由于級(jí)數(shù)少,延時(shí)也較少,因此圖3的速度要比圖4快。然而,由于圖3的輸入項(xiàng)要比圖4大的多(10:5),因此,占用的面積必然也比圖3大。圖4是圖3通過(guò)提取公因數(shù)(例中是B和C)得來(lái)的,這是把附加的中間項(xiàng)加到結(jié)構(gòu)描述中去的一種過(guò)程,它使輸入到輸出中的邏輯級(jí)數(shù)增加,犧牲速度換來(lái)電路占用面積的減少。對(duì)于對(duì)延時(shí)要求不高的情況下采用這種方法分解邏輯電路以達(dá)到減少電路復(fù)雜度的目的。

??? 通過(guò)以上簡(jiǎn)單、初步的探討,我們可以知道,用VHDL進(jìn)行集成電路的設(shè)計(jì),牽涉到對(duì)VHDL語(yǔ)言的使用方法和對(duì)設(shè)計(jì)的理解程度。本文討論了以下幾個(gè)簡(jiǎn)化和優(yōu)化電路設(shè)計(jì)的3個(gè)值得注意的方面:

(1)在用VHDL進(jìn)行設(shè)計(jì)中要注意避免不必要的寄存器描述。

(2)在編寫程序前要先對(duì)整個(gè)設(shè)計(jì)進(jìn)行較深入的了解?科學(xué)的劃分設(shè)計(jì),多設(shè)想幾種方案?再進(jìn)行比較?用多個(gè)較少位數(shù)的單元取代較多位數(shù)的單元。

(3)在延時(shí)要求不高的情況下,可提取邏輯電路公因子?把它分解成含有中間變量的多級(jí)電路。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論