可編程邏輯

提供權(quán)威的PLD及可編程邏輯器件設(shè)計(jì)應(yīng)用、Altera公司、Xilinx公司資訊和解決方案,包括HDL語(yǔ)言與源代碼、FPGA開(kāi)發(fā)板、EDA工具、FPGA、FPGA軟件等領(lǐng)域。基于分布式算法和FPGA實(shí)現(xiàn)基帶信號(hào)成形的研究

摘要: 提出了一種采用現(xiàn)場(chǎng)可編程門陣列(FPGA)實(shí)現(xiàn)基帶信號(hào)成形的FIR數(shù)字濾波器硬件電路的方案。該方案基于分布式算法的思想,利用FPGA豐富的查找表資源,從...

2009-06-20 標(biāo)簽:基帶信號(hào) 1488

基于FPGA流水線分布式算法的FIR濾波器的實(shí)現(xiàn)

摘要: 提出了一種采用現(xiàn)場(chǎng)可編碼門陣列器件(FPGA)并利用窗函數(shù)法實(shí)現(xiàn)線性FIR數(shù)字濾波器的設(shè)計(jì)方案,并以一個(gè)十六階低通FIR數(shù)字濾波器電路的實(shí)現(xiàn)...

2009-06-20 標(biāo)簽:FIR 1725

FIR數(shù)字濾波器分布式算法的原理及FPGA實(shí)現(xiàn)

摘要: 在利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理方面,分布式算法發(fā)揮著關(guān)鍵作用,與傳統(tǒng)的乘積-積結(jié)構(gòu)相比,具有并行處理的高效性特點(diǎn)。詳細(xì)研究了基于FPGA、采用分布式...

2009-06-20 標(biāo)簽:FIR 6428

數(shù)字頻率合成器的FPGA實(shí)現(xiàn)

摘要: 介紹了DDFS的原理和Altera公司的FPGA器件ACEX 1K的主要特點(diǎn),給出了用ACEX 1K系列器件EP1K10TC144-1實(shí)現(xiàn)數(shù)字頻率合成器的工作原理、設(shè)計(jì)思路、電路結(jié)構(gòu)和仿真結(jié)...

2009-06-20 標(biāo)簽:FPGA 1201

采用可編程邏輯器件器件設(shè)計(jì)可變格式和可變速率的通信數(shù)字信號(hào)源

摘要:采用Lattice公司的在系統(tǒng)可編程器件pLSI/ispLSI1016,設(shè)計(jì)出一個(gè)具有可變格式、可變長(zhǎng)度和可變速率的通信數(shù)字信號(hào)源,從而可以產(chǎn)生出符...

2009-06-20 標(biāo)簽:可編程 785

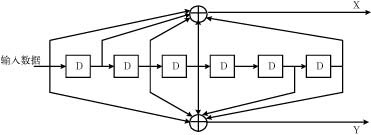

利用FPGA技術(shù)實(shí)現(xiàn)數(shù)字通信中的交織器和解交織器

摘要:介紹用FPGA實(shí)現(xiàn)數(shù)字通信中的交、解交織器的一種比較通用的方案,詳細(xì)說(shuō)明了設(shè)計(jì)中的一些問(wèn)題及解決辦法。還介紹了一種實(shí)現(xiàn)FPGA中信號(hào)延時(shí)的方法。 ...

2009-06-20 標(biāo)簽:FPGA 1648

用FPGA設(shè)計(jì)軟件無(wú)線電和調(diào)制解調(diào)器

本文以16-QAM RF發(fā)射數(shù)據(jù)泵的設(shè)計(jì)為例,介紹利用FPGA設(shè)計(jì)數(shù)字濾波器的技巧和器件選擇方法,說(shuō)明執(zhí)行分布式計(jì)算時(shí)FPGA比DSP的優(yōu)越之處。 所有數(shù)字邏輯的基本結(jié)構(gòu) ...

2009-06-20 標(biāo)簽:FPGA 948

FPGA在多進(jìn)制正交擴(kuò)頻通信系統(tǒng)中的應(yīng)用

摘 要: 討論了高速無(wú)線分組網(wǎng)絡(luò)中多進(jìn)制正交擴(kuò)頻通信系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),其中在系統(tǒng)核心部分的擴(kuò)頻編碼調(diào)制和解調(diào)等很多功能都由FPGA來(lái)完成,并對(duì)此進(jìn)行了詳細(xì)的介紹。 ...

2009-06-20 標(biāo)簽:FPGA 1398

同步數(shù)字體制(SDH)數(shù)字交叉連接(SDXC)矩陣的設(shè)計(jì)原理

要:介紹了一種基于現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)的同步數(shù)字體制(SDH)數(shù)字交叉連接(SDXC)矩陣的設(shè)計(jì)原理,該矩陣可以實(shí)現(xiàn)2條STM-1輸入信號(hào)中126個(gè)TU-12支路之間任意的無(wú)阻塞交叉...

基于FPGA的直接數(shù)字頻率合成器的設(shè)計(jì)和實(shí)現(xiàn)

摘要:介紹了利用Altera的FPGA器件(ACEX EP1K50)實(shí)現(xiàn)直接數(shù)字頻率合成器的工作原理、設(shè)計(jì)思想、電路結(jié)構(gòu)和改進(jìn)優(yōu)化方法。 關(guān)鍵詞:直接數(shù)字...

2009-06-20 標(biāo)簽:FPGA 838

采用PCM編碼原理及FPGA編程技術(shù)實(shí)現(xiàn)PCM數(shù)字基群接口傳

一、概述 ----高速傳輸系統(tǒng)中低速設(shè)備的接入有廣泛的應(yīng)用范圍。在環(huán)境監(jiān)控等監(jiān)控網(wǎng)絡(luò)中,被監(jiān)控設(shè)備往往提供RS-232/RS-485/V.10/V.35的通信接口,為...

2009-06-20 標(biāo)簽:PCM 1803

用FPGA在數(shù)字電視系統(tǒng)中進(jìn)行級(jí)聯(lián)編碼

摘 要:本文介紹了串型級(jí)聯(lián)編碼的原理,以及它在數(shù)字電視地面?zhèn)鬏斚到y(tǒng)中的應(yīng)用,通過(guò)FPGA設(shè)計(jì)電路實(shí)現(xiàn)編碼過(guò)程,最后說(shuō)明串型級(jí)聯(lián)編碼的應(yīng)用優(yōu)越性。 ...

2009-06-20 標(biāo)簽:數(shù)字電視 1025

基于FPGA的總線型LVDS通信系統(tǒng)設(shè)計(jì)

摘要:總線型低壓差分信號(hào)(BLVDS)是一種性能優(yōu)良的物理層接口標(biāo)準(zhǔn)。本文介紹一種基于總線型LVDS的通信系統(tǒng)方案,以及利用FPGA芯片實(shí)現(xiàn)系統(tǒng)核心模塊的設(shè)計(jì)方...

2009-06-20 標(biāo)簽:lvds 7139

HDLC的FPGA實(shí)現(xiàn)方法

摘要: HDLC(高級(jí)數(shù)據(jù)鏈路控制)的一般實(shí)現(xiàn)方法為采用ASIC器件和軟件編程等。應(yīng)用ASIC器件時(shí)設(shè)計(jì)簡(jiǎn)單,但靈活性較差;軟件編程方法靈活,但占用處理器資源多...

2009-06-20 標(biāo)簽:hdlc 4193

基于模糊控制的遲早門同步器及其FPGA實(shí)現(xiàn)

摘要:介紹了遲早門同步器的基本工作原理,提出了在遲早門同步器中引入模糊邏輯控制獲得較小相位抖動(dòng)的方法,給出了遲早門同步器在FPGA上的...

2009-06-20 標(biāo)簽:FPGA 1036

用XC9572實(shí)現(xiàn)HDB3編解碼設(shè)計(jì)

摘要:介紹了HDB3編解碼的原理和方法,給出了用CPLD(Complex Programmable Logic Device)實(shí)現(xiàn)E1信號(hào)HDB3編解碼的方法,同時(shí)給出了它的實(shí)現(xiàn)原理圖,最后給出了XI...

用FPGA實(shí)現(xiàn)1553B總線接口中的曼碼編解碼器

摘要: 介紹用FPGA設(shè)計(jì)實(shí)現(xiàn)MIL-STD1553B部接口中的曼徹斯特碼編解碼器。該設(shè)計(jì)采用VHDL硬件描述語(yǔ)言編程,并且專門的綜合工具Synplify對(duì)設(shè)計(jì)進(jìn)行綜合、優(yōu)化,在MA...

一種用VHDL設(shè)計(jì)嵌入式Web Server的方案

摘要: 近幾年嵌入式Internet開(kāi)始迅猛發(fā)展,但絕大多數(shù)嵌入式Internet都使用微控制器和相應(yīng)的軟件來(lái)實(shí)現(xiàn)。本文介紹一種基于硬件來(lái)實(shí)現(xiàn)嵌入式Web Server的方案。該方...

自適應(yīng)算術(shù)編碼的FPGA實(shí)現(xiàn)

摘要: 在簡(jiǎn)單介紹算術(shù)編碼和自適應(yīng)算術(shù)編碼的基礎(chǔ)上,介紹了利用FPGA器件并通過(guò)VHDL語(yǔ)言描述實(shí)現(xiàn)自適應(yīng)算術(shù)編碼的過(guò)程。整個(gè)編碼系統(tǒng)在LTERA公司的MAX+plus Ⅱ軟...

2009-06-20 標(biāo)簽:FPGA 1430

FPGA在軟件無(wú)線電中的應(yīng)用

摘 要 :本文結(jié)合各種實(shí)際測(cè)試介紹了羅德與施瓦茨公司的手持式頻譜儀R&S FSH在發(fā)射機(jī)與天饋線測(cè)試、無(wú)線電干擾查處以及電磁兼容診斷測(cè)試中的應(yīng)用。 ...

2009-06-20 標(biāo)簽:FPGA 833

利用FPGA實(shí)現(xiàn)多路話音/數(shù)據(jù)復(fù)接設(shè)備

摘 要: 本文利用FPGA完成了8路同步話音及16路異步數(shù)據(jù)的復(fù)接與分接過(guò)程,并且實(shí)現(xiàn)了復(fù)接前的幀同步捕獲和利用DDS對(duì)時(shí)鐘源進(jìn)行分頻得到所需時(shí)鐘的過(guò)程。該設(shè)計(jì)...

2009-06-20 標(biāo)簽:FPGA 832

PSD813器件在單片機(jī)系統(tǒng)中應(yīng)用

摘要:可編程外圍器件PSD813應(yīng)用于單片機(jī)系統(tǒng)后,可大幅度地簡(jiǎn)化CPU外圍電路的設(shè)計(jì),減小系統(tǒng)體積,降低功耗,增強(qiáng)系統(tǒng)可靠性。介紹了PSD813系列產(chǎn)品...

2009-06-20 標(biāo)簽: 1006

用CPLD實(shí)現(xiàn)單片機(jī)與ISA總線并行通信

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。 關(guān)鍵詞:CPLD...

2009-06-20 標(biāo)簽:cpld 1382

基于EPLD的PCI總線仲裁器的設(shè)計(jì)與實(shí)現(xiàn)

摘 要: 以自行研制開(kāi)發(fā)的PCI高速總線背板為背景,系統(tǒng)地論述了PCI總線的仲裁機(jī)制、總線的缺省占用、仲裁信號(hào)協(xié)定及優(yōu)先級(jí)仲裁算法,給出了采用EPLD實(shí)現(xiàn)仲裁器功能的編程設(shè)計(jì)...

2009-06-20 標(biāo)簽:pci總線 1453

基于CPLD的單片機(jī)PCI接口設(shè)計(jì)

摘要:詳細(xì)闡述一種利用CPLD實(shí)現(xiàn)的8位單片機(jī)與PCI設(shè)備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實(shí)踐中檢驗(yàn)通過(guò)。 關(guān)鍵詞:?jiǎn)纹瑱C(jī) CPLD PCI 8位單片...

2009-06-20 標(biāo)簽:PCI 1208

在CPLD管理下實(shí)現(xiàn)高效多串口中斷源

摘要:針對(duì)嵌入式系統(tǒng)的精簡(jiǎn)特性,提出一種通過(guò)1個(gè)中斷源高效管理多個(gè)串行口的有效方法,不但節(jié)省系統(tǒng)資源,而且實(shí)現(xiàn)了多個(gè)串行口中斷的無(wú)漏檢測(cè)與服務(wù)。 ...

2009-06-20 標(biāo)簽:cpld 1249

基于FPGA的LCD&VGA控制器設(shè)計(jì)

摘要:介紹了基于FPGA的圖形式LCD&VGA控制器的設(shè)計(jì),詳細(xì)討論了用VHDL設(shè)計(jì)行場(chǎng)掃描時(shí)序的方法,這種設(shè)計(jì)方法稍作改動(dòng)便可產(chǎn)生任意行場(chǎng)掃描時(shí)序,具有很好的可重用性。...

基于FPGA的USB2.0控制器設(shè)計(jì)

摘要:介紹了一種用VHDL設(shè)計(jì)USB2.0功能控制器的方法,詳術(shù)了其原理和設(shè)計(jì)思想,并在FPGA上予以實(shí)現(xiàn)。 關(guān)鍵詞:USB VHDL FPGA 在視...

2009-06-20 標(biāo)簽:USB2.0 1969

專用鍵盤接口芯片的一種CPLD實(shí)現(xiàn)方案

摘要:對(duì)用于單片機(jī)的鍵盤子系統(tǒng)的專用鍵盤接口芯片進(jìn)行功能分析,就芯片中核心部件的時(shí)序設(shè)計(jì)進(jìn)行狀態(tài)描述,并利用可編程邏輯技術(shù)和原理輸入方式對(duì)鍵盤接...

2009-06-20 標(biāo)簽:鍵盤 1476

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |