前言 SDRAM控制器里面包含5個(gè)主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執(zhí)行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

設(shè)計(jì)的基礎(chǔ)上給出了SDRAM控制器的實(shí)現(xiàn)原理以及詳細(xì)的子模塊劃分。整個(gè)控制器的設(shè)計(jì)已用Verilog HDL語言實(shí)現(xiàn)并通過了Modelsim仿真和FPGA驗(yàn)證。仿真結(jié)果表明所設(shè)計(jì)的控制器符合SDRAM內(nèi)部

2014-01-02 13:59:42 5140

5140

在高速實(shí)時(shí)或者非實(shí)時(shí)信號(hào)處理系統(tǒng)當(dāng)中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié),也是系統(tǒng)實(shí)現(xiàn)中的重點(diǎn)和難點(diǎn)之一。SDRAM(同步動(dòng)態(tài)隨機(jī)訪問存儲(chǔ)器)具有價(jià)格低廉、密度高、數(shù)據(jù)讀寫速度快的優(yōu)點(diǎn)

2018-01-18 07:21:00 8866

8866

本文主要詳解基于FPGA的模糊PID控制器的設(shè)計(jì)實(shí)現(xiàn),首先介紹了FPGA工作原理、基本特點(diǎn)以及FPGA的優(yōu)勢,其次闡述了使用Altera的FPGA設(shè)計(jì)實(shí)現(xiàn)的數(shù)字模糊PID控制器,具體的跟隨小編一起來了解一下。

2018-06-01 09:26:51 18186

18186 FPGA實(shí)現(xiàn)的SATA控制器FPGA實(shí)現(xiàn)的SATA控制器

2012-08-11 18:08:52

FPGA之SDRAM控制器設(shè)計(jì)(二):刷新這次要來解決上次留下來的刷新問題,在100us后首先要經(jīng)過兩次刷新才進(jìn)行模式寄存器設(shè)置。這顆SDRAM芯片需要每隔64ms對8192行(列地址10-位,行

2021-07-30 07:48:42

FPGA怎么實(shí)現(xiàn)控制CF從SDRAM中讀取數(shù)據(jù)以及實(shí)現(xiàn)CF卡向SDRAM中上傳數(shù)據(jù)????本人初學(xué)者,希望大家?guī)蛶兔Γ。。。≈x謝!!

2013-02-25 21:58:59

基于SDRAM控制器實(shí)現(xiàn)FPGA模塊化和通用性的解決方案設(shè)計(jì)

2020-12-22 07:58:55

SDRAM文件結(jié)構(gòu)存儲(chǔ)控制的FPGA實(shí)現(xiàn)面對不同的應(yīng)用場景,原始采樣數(shù)據(jù)可能包含多種不同樣式的信號(hào),這給傳統(tǒng)基于連續(xù)存儲(chǔ)方式的數(shù)據(jù)緩存系統(tǒng)帶來了挑戰(zhàn)。除此之外,由于對不同信號(hào)的處理往往需要不同的數(shù)據(jù)

2012-08-13 10:40:40

SDRAM的基本工作原理是什么SDRAM的基本讀寫操作步驟是什么一種簡單的通用SDRAM控制器的實(shí)現(xiàn)

2021-05-10 06:26:44

本次發(fā)布三例 SDRAM 控制器參考設(shè)計(jì)及 IP Core Generator 支持調(diào)用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

第六講已介紹完SDRAM的寫模塊,而在這一講中,我們會(huì)接著介紹SDRAM控制器的讀模塊。在搞定讀模塊之后,就相當(dāng)于SDRAM控制器部分已經(jīng)搭建好了,想一想還是很期待的哦,哈哈,大家先別急。在這一講中

2017-05-08 22:28:13

第1節(jié) SDRAM讀寫控制器--作者:小黑同學(xué)本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請注明出處!1.1 總體設(shè)計(jì)1.1.1 概述同步動(dòng)態(tài)隨機(jī)存取內(nèi)存(synchronousdynamic

2020-10-15 15:16:02

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

2012-08-20 19:35:27

本文介紹一種通用SDRAM控制器的FPGA模塊化解決方案。

2021-05-07 06:42:49

求大佬介紹一種通用SDRAM控制器的FPGA模塊化解決方案

2021-04-08 06:40:34

。DDR的時(shí)序與SDRAM是相似的,學(xué)好SDRAM后,理解DDR2和DDR3就非常容易了。2、至簡設(shè)計(jì)代碼實(shí)現(xiàn)(附錄部分代碼)下面是使用至簡設(shè)計(jì)法實(shí)現(xiàn)的SDRAM控制器,該控制器使用了四段式狀態(tài)機(jī),其他信號(hào)

2017-08-02 17:43:35

基于FPGA的SDRAM控制器設(shè)計(jì)(原創(chuàng)分享)—自動(dòng)刷新設(shè)計(jì)作者:小周本文為明德?lián)P原創(chuàng)及錄用文章,轉(zhuǎn)載請注明出處!SDRAM控制器設(shè)計(jì)的主要功能是能對SDRAM進(jìn)行讀寫操作,本工程實(shí)現(xiàn)了SDRAM

2020-04-15 14:43:50

集成電路組成,通過為液晶顯示系統(tǒng)提供時(shí)序信號(hào)和顯示數(shù)據(jù)來實(shí)現(xiàn)液晶顯示。本設(shè)計(jì)是一種基于FPGA(現(xiàn)場可編程門陣列)的液晶顯示控制器。與集成電路控制器相比,FPGA更加靈活,可以針對小同的液晶顯示模塊更改

2019-10-22 08:07:28

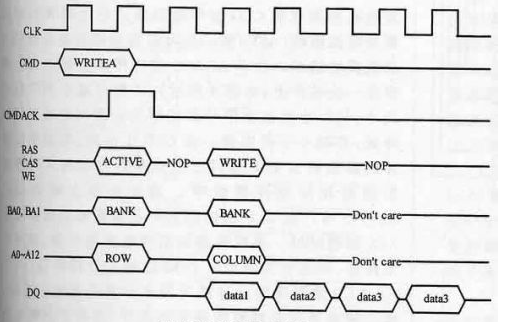

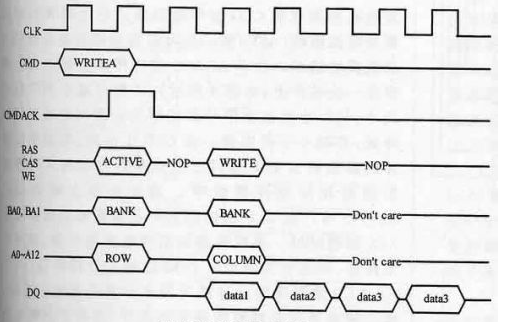

本文提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,并用Verilog給于實(shí)現(xiàn),仿真結(jié)果表明通過該方法設(shè)計(jì)實(shí)現(xiàn)的控制器可以在FPGA芯片內(nèi)組成如圖1所示的SDRAM接口,從而使得系統(tǒng)用戶對SDRAM的操作非常方便。

2021-04-15 06:46:56

基于FPGA的SDRAM控制器包括哪些部分呢?如何去實(shí)現(xiàn)一種基于FPGA的SDRAM控制器設(shè)計(jì)呢?

2021-11-04 06:47:44

SDRAM控制器基本操作原理是什么?如何去設(shè)計(jì)并實(shí)現(xiàn)一種SDRAM控制器?

2021-06-07 06:01:39

的工作時(shí)鐘頻率。然而,設(shè)計(jì)至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實(shí)現(xiàn)高速、高效率的DDR3控制器是一項(xiàng)艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲(chǔ)器可靠接口的塊

2019-08-09 07:42:01

如何解決SDRAM控制器設(shè)計(jì)刷新的問題?

2021-11-04 07:20:02

大家好,我想設(shè)計(jì)自己的DDR控制器并在FPGA上驗(yàn)證它。我將在verilog中實(shí)現(xiàn)我剛開始閱讀JESDC79C DDR規(guī)格..但我很困惑如何編寫那些初始化序列?請建議如何處理這個(gè)設(shè)計(jì)DDR控制器

2019-04-29 11:59:22

本文采用Verilog FPGA設(shè)計(jì)懸掛運(yùn)動(dòng)控制系統(tǒng)的控制器,通過輸入模塊傳送控制參數(shù),采用HDL語言編程實(shí)現(xiàn)的控制算法,驅(qū)動(dòng)步進(jìn)電機(jī),對懸掛運(yùn)動(dòng)物體進(jìn)行精確的控制。

2021-05-06 07:11:03

基于FPGA的MCU設(shè)計(jì)有兩種基本實(shí)現(xiàn)方式如何實(shí)現(xiàn)微控制器與FPGA的接口設(shè)計(jì)

2021-05-06 10:05:17

的內(nèi)存控制器的設(shè)計(jì)與應(yīng)用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存儲(chǔ)器接口設(shè)計(jì).pdf一種采用FPGA設(shè)計(jì)的SDRAM控制器.pdf用Xilinx+FPGA實(shí)現(xiàn)DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

CAN總線控制器Verilog代碼

2008-05-20 10:32:12 170

170 針對SDRAM 控制器讀寫數(shù)據(jù)塊訪問延時(shí)長、速度慢的問題,提出時(shí)間隱藏技術(shù),將其應(yīng)用于SDRAM 控制器的設(shè)計(jì),采用FPGA實(shí)現(xiàn)。實(shí)驗(yàn)結(jié)果表明,時(shí)間隱藏技術(shù)有效縮短了數(shù)據(jù)塊讀寫訪問

2009-03-25 09:00:34 15

15 介紹基于現(xiàn)場可編程門陣列(FPGA),利用VHDL 語言設(shè)計(jì)實(shí)現(xiàn)MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結(jié)構(gòu)、SDRAM 存儲(chǔ)接口結(jié)構(gòu)和SDRAM 控制狀態(tài)機(jī)的設(shè)計(jì)。

2009-05-15 14:47:29 24

24 ref-sdr-sdram-verilog代碼

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:50:44 33

33 采用 Verilog HDL 語言在Altera 公司的FPGA 芯片上實(shí)現(xiàn)了RISC_CPU 的關(guān)鍵部件狀態(tài)控制器的設(shè)計(jì),以及在與其它各種數(shù)字邏輯設(shè)計(jì)方法的比較下,顯示出使用Verilog HDL語言的優(yōu)越性.關(guān)鍵詞

2009-08-21 10:50:05 69

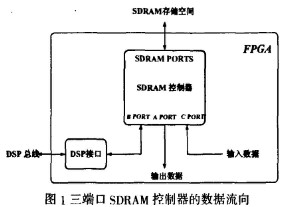

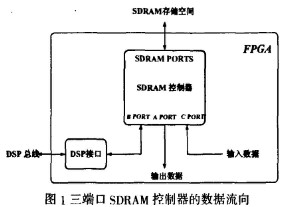

69 設(shè)計(jì)實(shí)現(xiàn)了一種基于FPGA 的,可用于多數(shù)據(jù)緩存的、能夠高效利用帶寬的多端口SDRAM 控制器。本文使用狀態(tài)機(jī)的設(shè)計(jì)思想,采用Verilog 硬件描述語言設(shè)計(jì)了時(shí)序控制程序。得到的SDR

2009-08-27 09:43:33 23

23 簡要介紹了SDRAM工作原理并認(rèn)真研究了Altera提供的SDRAM控制器,根據(jù)實(shí)際系統(tǒng)使用需要加以修改簡化,設(shè)計(jì)了對修改后控制器進(jìn)行操作的狀態(tài)機(jī)。采用全頁突發(fā)讀寫模式,每次讀/寫

2009-12-26 17:02:56 70

70 NandFlash控制器的FPGA實(shí)現(xiàn)方法技巧與程序案例分享。

2017-09-21 09:40:00 78

78 DDR2 SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計(jì)方法!詳述了其基本結(jié)構(gòu)和設(shè)計(jì)思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實(shí)現(xiàn)了一個(gè)三端口非透明型SDRAM 控制器,該控制器面向用戶具有多個(gè)端口,通過輪換優(yōu)先級(jí)的設(shè)計(jì)保證了多個(gè)端口平均分配SDRAM的帶寬且不會(huì)降

2010-03-03 14:37:14 11

11 SMBus是一種高效的同步串行總線。通過分析SMBus總線協(xié)議,提出了一種運(yùn)行于基于PCI-Express技術(shù)的橋接芯片上的SMBus控制器的設(shè)計(jì)方案,并且用Verilog語言描述,最后在Altera公司的FPGA上

2010-07-16 15:08:12 16

16 簡要介紹了SDRAM工作原理并認(rèn)真研究了Altera提供的SDRAM控制器,根據(jù)實(shí)際系統(tǒng)使用需要加以修改簡化,設(shè)計(jì)了對修改后控制器進(jìn)行操作的狀態(tài)機(jī)。采用全頁突發(fā)讀寫模式,每次讀/寫后自動(dòng)

2010-07-21 17:31:37 38

38 摘要: 介紹了SDRAM的存儲(chǔ)體結(jié)構(gòu)、主要控制時(shí)序和基本操作命令,并且結(jié)合實(shí)際系統(tǒng),給出了一種用FPGA實(shí)現(xiàn)的通用SDRAM控制器的方案。

關(guān)鍵詞:

2009-06-20 12:51:58 1027

1027

基于FPGA的高速SDRAM控制器的視頻應(yīng)用

0 引言 SDRAM(同步動(dòng)態(tài)存儲(chǔ)器)是一種應(yīng)用廣泛的存儲(chǔ)器,具有容量大、數(shù)據(jù)讀寫速度快、價(jià)格低廉等優(yōu)點(diǎn),特別適

2009-11-04 09:56:20 1065

1065 文章對適用DDR2 SDRAM控制器的結(jié)構(gòu)、接口和時(shí)序進(jìn)行了深入研究與分析,總結(jié)出一些控制器的關(guān)鍵技術(shù)特性,然后采用了自頂向下(TOP-IX)WN)的設(shè)計(jì)方法,用Verilog硬件描述語言實(shí)現(xiàn)控制器,

2011-09-01 16:36:29 174

174 SDRAM存儲(chǔ)芯片擁有快速讀寫的性能,可以應(yīng)用以回波模擬系統(tǒng)作為數(shù)據(jù)高速緩存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有嚴(yán)格的控制時(shí)序和工作狀態(tài),可以使用有限狀態(tài)機(jī)理論

2011-10-24 15:08:05 0

0 介紹了基于FPGA的以太網(wǎng)MAC控制器的設(shè)計(jì),主要實(shí)現(xiàn)了半雙工模式下CSMA/CD協(xié)議、全雙工模式下Pause幀的收發(fā),以及對物理層芯片中寄存器的讀寫訪問。設(shè)計(jì)采用Verilog硬件描述語,按照自

2011-11-15 11:38:17 284

284 通過設(shè)計(jì)基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等單片機(jī)和DSP等微處理器的外部連接SDRAM,增加系統(tǒng)的存儲(chǔ)空間。

2012-02-16 17:06:47 45

45 使用功能強(qiáng)大的FPGA來實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 239

239 介紹了一種基于FPGA的多軸控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外圍電路組成,用于同時(shí)控制多路電機(jī)的運(yùn)動(dòng)。利用Verilog HDL 硬件描述語言在FPGA中實(shí)現(xiàn)了電機(jī)控制邏

2013-04-27 16:23:11 82

82 為實(shí)現(xiàn)目標(biāo)識(shí)別與跟蹤的應(yīng)用目的 ,在基于 TMS320DM642 的 FIFO 基礎(chǔ)上擴(kuò)展存儲(chǔ)空間 ,提出一種基于

FPGA實(shí)現(xiàn) SDRAM 控制器的方法。分析所用 SDRAM 的特點(diǎn)和工作原理

2015-10-29 14:05:57 2

2 快速浮_定點(diǎn)PID控制器FPGA的研究與實(shí)現(xiàn)

2016-05-11 11:30:19 20

20 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 40

40 Xilinx FPGA工程例子源碼:FPGA實(shí)現(xiàn)CAN總線控制器源碼

2016-06-07 14:13:43 97

97 用 Verilog實(shí)現(xiàn)基于FPGA 的通用分頻器的設(shè)計(jì)時(shí)鐘分頻包括奇數(shù)和偶數(shù)分頻

2016-07-14 11:32:47 46

46 高速圖像存儲(chǔ)系統(tǒng)中SDRAM控制器的實(shí)現(xiàn)

2016-08-29 15:02:03 10

10 基于FPGA的VGA圖像控制器的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 13

13 華清遠(yuǎn)見FPGA代碼-SDRAM讀寫控制的實(shí)現(xiàn)與Modelsim仿真

2016-10-27 18:07:54 26

26 DDR2SDRAM控制器IP功能測試與FPGA驗(yàn)證_陳平

2017-01-07 21:45:57 3

3 基于VHDL的SDRAM控制器的實(shí)現(xiàn)

2017-01-22 13:43:27 12

12 EPM1240的SDRAM控制器的設(shè)計(jì)

2017-10-31 08:24:31 21

21 為了滿足高速圖像數(shù)據(jù)采集系統(tǒng)中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設(shè)計(jì)方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 4071

4071

控制器,在介紹控制器的邏輯結(jié)構(gòu)的基礎(chǔ)上,對FPGA與SDRAM間數(shù)據(jù)通信進(jìn)行了時(shí)序分析,實(shí)現(xiàn)SDRAM 帶有自動(dòng)預(yù)充電突發(fā)讀寫和非自動(dòng)預(yù)充電整頁讀寫。

2017-11-18 12:42:03 2520

2520

邏輯復(fù)雜,接口方式與普通的存儲(chǔ)器差異很大。為了解決這個(gè)矛盾,需要設(shè)計(jì)專用的SDRAM控制器,使用戶像使用SRAM -樣方便的使用SDRAM。考慮到控制器的通用性,本文中提出了一種通用的SDRAM控制器的FPGA設(shè)計(jì),FPGA內(nèi)部采用狀態(tài)機(jī)的方式。該設(shè)計(jì)采用了AD公

2017-11-28 19:51:26 5

5 隨著大規(guī)模集成電路和高速、低功耗、高密度存儲(chǔ)技術(shù)的發(fā)展,SDRAM動(dòng)態(tài)存儲(chǔ)器因容量大、速度快、價(jià)格低廉等優(yōu)點(diǎn),現(xiàn)已成為PC內(nèi)存的主流。然而SDRAM存儲(chǔ)器內(nèi)部控制邏輯十分復(fù)雜,時(shí)序要求也非常嚴(yán)格,因此需要設(shè)計(jì)專門的SDRAM控制器來實(shí)現(xiàn)系統(tǒng)對SDRAM的訪問。

2018-04-30 10:58:00 5913

5913

SDRAM 具有存儲(chǔ)容量大、速度快、成本低的特點(diǎn),因此廣泛應(yīng)用于雷達(dá)信號(hào)處理等需 要海量高速存儲(chǔ)的場合,但是SDRAM 的操作相對復(fù)雜,需要有專門的控制器配合處理器 工作完成數(shù)據(jù)的存取操作。隨著FPGA 技術(shù)的快速發(fā)展及其應(yīng)用的普及,用FPGA 實(shí)現(xiàn) SDRAM 控制器是目前最流行的技術(shù)手段。

2019-04-26 08:06:00 3208

3208

實(shí)現(xiàn)數(shù)據(jù)的高速大容量存儲(chǔ)是數(shù)據(jù)采集系統(tǒng)中的一項(xiàng)關(guān)鍵技術(shù)。本設(shè)計(jì)采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態(tài)機(jī)來描述對DDR SDRAM 的各種時(shí)序

2019-08-14 08:00:00 4427

4427

,SDRAM的原理和時(shí)序,SDRAM控制器,動(dòng)態(tài)隨即存儲(chǔ)器SDRAM模塊功能簡介,基于FPGA的SDRAM控制器的設(shè)計(jì)和實(shí)現(xiàn),一種簡易SDRAM控制器的設(shè)計(jì)方法

2018-12-25 08:00:00 58

58 在學(xué)習(xí)FPGA的過程中,注意是在學(xué)習(xí)過程中,聯(lián)系FPGA的使用技巧,強(qiáng)烈建議嘗試設(shè)計(jì)一個(gè)SDRAM控制器,不要使用IP核。

2019-02-15 15:04:01 1077

1077 VGA(視頻圖形陣列)作為一種標(biāo)準(zhǔn)的顯示接口得到廣泛的應(yīng)用。依據(jù)VGA顯示原理,介紹了利用FPGA實(shí)現(xiàn)對VGA圖形控制器的Verilog設(shè)計(jì)方法。詳細(xì)描述了各硬件模塊的工作原理及實(shí)現(xiàn)途徑,并給出了軟件設(shè)計(jì)思路。

2019-06-29 10:05:30 5776

5776

為了實(shí)現(xiàn)軍航管制系統(tǒng)中雷達(dá)數(shù)據(jù)的可靠傳輸,根據(jù)HDLC協(xié)議的幀結(jié)構(gòu)和循環(huán)冗余校驗(yàn)(CRC)原理,提出了一種新型的基于并行機(jī)制的HDLC協(xié)議控制器,討論采用FPGA新技術(shù)實(shí)現(xiàn)HDLC協(xié)議幀的構(gòu)成

2020-11-04 18:04:10 15

15 針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲(chǔ)器和全頁突發(fā)式操作進(jìn)行研究的基礎(chǔ)上,提出一種簡易SDRAM 控制器的設(shè)計(jì)方法。該設(shè)計(jì)方法充分利用全頁式高效率存取的優(yōu)點(diǎn),對SDRAM 進(jìn)行配置、全頁突發(fā)式讀寫時(shí),操作方便。在實(shí)現(xiàn)sDRAM 的快速批量存儲(chǔ)方面,具有良好的應(yīng)用價(jià)值。

2020-12-18 16:13:18 6

6 以FPGA為平臺(tái),設(shè)計(jì)了采用SPI接口的SD卡控制器。整體設(shè)計(jì)用Verilog HDL硬件描述語言實(shí)現(xiàn),同時(shí)采用數(shù)據(jù)緩存(First In First Out,F(xiàn)IFO)技術(shù)解決實(shí)際應(yīng)用中的時(shí)序

2020-12-22 17:07:18 2

2 的設(shè)計(jì)方法。結(jié)合實(shí)際系統(tǒng),設(shè)計(jì)給出了使用FPGA實(shí)現(xiàn) SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過增加流水級(jí)數(shù)和將輸出觸發(fā)器布置在IO單元中,該控制器可達(dá)到185MHz的頻率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越來越廣泛。

2.SDRAM具有存儲(chǔ)容量大,速率快的特點(diǎn)。

3.SDRAM對時(shí)序要求嚴(yán)格,需要不斷刷新保持?jǐn)?shù)據(jù)。

.FPGA在電子設(shè)計(jì)中的廣泛應(yīng)用,使用十分靈活利用FPGA來設(shè)計(jì)自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 本應(yīng)用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實(shí)現(xiàn)的 DDR SDRAM 控制器。該實(shí)現(xiàn)運(yùn)用了直接時(shí)鐘控制技術(shù)來實(shí)現(xiàn)數(shù)據(jù)采集,并采用自動(dòng)校準(zhǔn)電路來調(diào)整數(shù)據(jù)線上的延遲。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相應(yīng)的解決方案詳細(xì)介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設(shè)計(jì)方案。該控制器采用Verilog HDL硬件描述語言實(shí)現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 23

23 在FPGA視頻圖像處理系統(tǒng)中,經(jīng)常需要使用到SDRAM作為視頻圖像緩存。SDRAM控制器可以分為上電初始化,自動(dòng)刷新,讀操作和寫操作這四個(gè)部分,他們之間的轉(zhuǎn)換可以通過狀態(tài)機(jī)來控制。下面分別實(shí)現(xiàn)這幾個(gè)部分。

2021-04-19 09:46:24 5358

5358

,SDRAM的控制邏輯復(fù)雜,使用很不方便。 為了解決這個(gè)矛盾,需要設(shè)計(jì)專用的SDRAM控制器,使系統(tǒng)用戶象使用SRAM一樣方便的使用SDRAM是十分必要的。考慮到控制器的通用性,本文提出了一種通用的SDRAM控制器的 Verilog設(shè)計(jì),并給出了實(shí)現(xiàn)結(jié)果。 1 SDRAM的工作原理

2021-06-30 09:16:47 3420

3420

FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)圖文稿(ltspice 放置電源)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)圖文稿資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 12:17:02 10

10 FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)(單片機(jī)電源維修)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)修訂稿(空調(diào)電源芯片)-該文檔為FPGA設(shè)計(jì)中DAC控制的Verilog實(shí)現(xiàn)修訂稿資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-26 13:13:56 10

10 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡介(arm嵌入式開發(fā)平臺(tái)PB)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 實(shí)現(xiàn)基于FPGA的SPIFlash控制器設(shè)計(jì)(嵌入式開發(fā)工作怎么樣)-該文檔為實(shí)現(xiàn)基于FPGA的SPIFlash控制器設(shè)計(jì)簡介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:10:17 5

5 基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡介(嵌入式開發(fā)工程師和基層公務(wù)員)-該文檔為基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡介文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 13:07:09 37

37 基于FPGA的SDRAM串口實(shí)驗(yàn)(嵌入式開發(fā)板實(shí)驗(yàn)報(bào)告)-基于FPGA的SDRAM串口實(shí)驗(yàn),verilog語言編寫

2021-08-04 09:43:17 37

37 電子發(fā)燒友網(wǎng)站提供《如何實(shí)現(xiàn)SDRAM存儲(chǔ)器并通過接口連接到高性能微控制器.zip》資料免費(fèi)下載

2022-09-07 09:31:55 1

1 電子發(fā)燒友網(wǎng)站提供《步進(jìn)電機(jī)控制器的FPGA的實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-07 16:29:17 1

1 電子發(fā)燒友網(wǎng)站提供《基于FPGA的一種SDRAM控制器簡易化設(shè)計(jì)方法.pdf》資料免費(fèi)下載

2023-10-26 09:08:37 0

0 實(shí)時(shí)視頻SDRAM控制器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2022-12-30 09:21:26 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論