介紹了一款可配置的USB IP核設計,重點描述USB IP核的結構劃分,詳細闡述了各模塊的設計思想。為了提高USB lP的可重用性,本USB IP核設計了總線適配器,經

2010-07-17 10:39:51 3124

3124

采用基于IP復用技術進行設計是減小這一差距惟一有效的途徑,IP復用技術包括兩個方面的內容:IP核生成和IP核復用。文中采用IP核復用方法和SOC技術基于AVR 8位微處理器AT90S1200IP Core設計專

2012-01-12 14:22:47 2515

2515

本文介紹了LCD的通用驅動電路IP核設計,采用自頂向下的設計方法將其劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進行描述,用FPGA實現并通過了仿真驗證。該IP核具有良好的移植性,可驅動不同規模的LCD電路。

2014-05-13 10:09:35 3236

3236 IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

公司現需12bit sar adc的IP核,國內有哪些公司提供相關方面的服務了?

2015-11-06 08:37:44

控制機制對當前變長分組骨干網的流量控制還是具有重要的參考價值,所以有必要對ATM的流量控制及其實現方式進行深入的研究。 IP核是一段具有特定電路功能的硬件描述語言代碼,該程序與集成電路工藝無關,因而

2011-09-27 11:54:25

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

Altera_IP核,僅供參考

2016-08-24 16:57:15

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

FPGA的IP軟核使用技巧主要包括以下幾個方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實現細節。它通常只經過功能

2024-05-27 16:13:24

如何根據成本、功耗和性能來選擇微處理器?FPGA結構中硬核和軟核的特點是什么?處理器IP有什么重要性?

2021-04-08 06:16:37

本帖最后由 gk320830 于 2015-3-8 09:29 編輯

LCD的通用驅動電路IP核設計 摘 要:本文介紹了一種新型的LCD驅動電路IP核的總體設計,采用自頂向下的設計方法將其

2012-08-12 12:28:42

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

求用sopc builder定制IP核的步驟,是9.0的軟件,假設硬件代碼已有

2013-09-14 18:35:40

請問哪位高手有ise軟件中的各個ip核的功能介紹

2013-10-08 16:41:25

有哪位大神用過pci ip核,為什么輸入lm_req32請求,pci側沒有reqn請求輸出呢?

2016-06-27 17:56:59

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 編輯

Quartus IP核破解在完成quartus軟件安裝之后,一般都要進行一個軟件破解。對于一般的需求來說

2016-05-19 14:13:09

,可以打開參數設置對話框。點擊左上方的Documentation可以查看IP核的手冊。這里將輸入的A、B均設置為4為無符號型,其他為默認值,點擊OK確認。三、繪制電路1. 右擊Diagram窗口空白處

2018-05-15 12:05:13

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP(Intellectual Property)核。

2019-11-04 07:40:53

剛剛接觸IP核做FFT,現在用的是FFTV9.0,已經建立了一個IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應該怎樣呢,謝謝指點。

2011-04-21 10:22:31

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口標準

2019-06-11 05:00:07

Viterbi譯碼的基本過程,接著根據Viterbi譯碼器IP核的特點,分別詳細介紹了并行結構、混合結構和基于混合結構的增信刪余3種Viterbi譯碼器IP核的主要性能和使用方法,并通過應用實例給出了譯碼器IP

2010-04-26 16:08:39

我畢業設計要做一個基于FPGA的IP核的DDS信號發生器,但是我不會用DDS的IP核,有沒有好人能發我一份資料如何用IP核的呀。我的瀏覽器下載不了網站上的資料,所以只能發帖求幫忙了。

2015-03-10 11:46:40

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

什么是三相全控橋整流電路?怎樣去設計IP軟核?怎樣對IP軟核進行仿真及驗證?

2021-04-23 07:12:38

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一個問題。比如說:某個IP,用于計算sin函數,使用了流水線機制,所有從輸入到輸出需要20個時鐘周期的延時。另外,還有一個IP,從輸入到輸出需要1

2021-06-19 11:06:07

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

這是我們一個小比賽的題面:設計一個簡易的電子計算器電路,包括輸入數據處理電路,算數運算電路(包含加法、減法、乘法、除法等算數運算),運算結果處理電路,所有運算電路的設計均不可使用IP核及查找表進行

2018-04-06 20:46:11

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

章禮宏 范全潤1 引言隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

提出一種可進化IP 核的設計和實現方法。這種IP 核采用進化硬件的設計思想, 將遺傳算法運用于硬件電路的設計中,使電路能根據當前的環境自動進行內部電路的進化,從而生成最

2009-05-16 14:33:28 14

14 IP核生成器生成ip后有兩個文件對我們比較有用,假設生成了一個asyn_fifo的核,則asyn_fifo.veo給出了例化該核方式(或者在Edit->Language Template->COREGEN中找到verilog/VHDL的例化方式)

2009-07-21 16:42:12 0

0 IC設計技術中的IP核互連:隨著IC 設計復雜度的不斷提高,在SoC 中集成的IP 核越來越多,基于片上總線的SOC 設計技術解決了大規模集成電路的設計難點,但是片上總線的應用帶來了

2009-10-14 12:50:23 8

8 隨著集成電路設計復雜度的提高和產品上市時間壓力的增大,基于IP 核復用的SoC 設計已成為一種重要的設計方法。在SoC 中集成的IP 核越來越多時,IP 核的互連策略和方法就成

2009-11-28 14:40:46 8

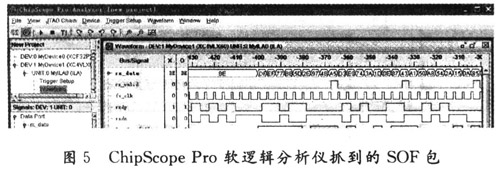

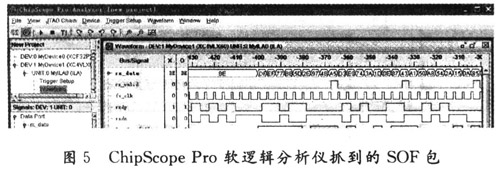

8 USB設備接口IP核的設計:討論了用Verilog硬件描述語言來實現USB設備接口IP核的方法,并進行了FPGA的驗證。簡要介紹USB系統的體系結構,重點描述USB設備接口IP核的結構劃分和各模塊的

2010-01-08 18:15:38 22

22 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 基于Avalon總線的可配置LCD 控制器IP核的設計

本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能

2010-02-09 09:34:44 27

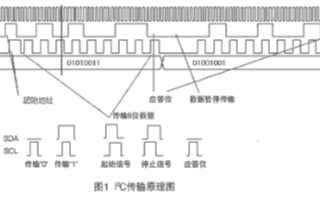

27 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設計,給出了該IP核的系統結構以及各個子模塊的詳細設計方法,并對該IP核進行了功能仿真、FPGA原型驗證,可測性設計以

2010-07-17 16:20:22 21

21 基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 1195

1195

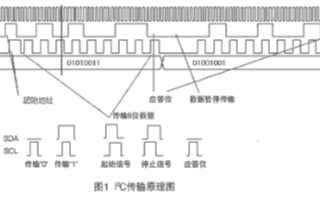

I2C器件接口IP核的CPLD設計

根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立

2009-03-28 16:21:35 1351

1351

摘 要: 根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立過程,并下載到

2009-06-20 13:36:12 1065

1065

基于PCI IP核的碼流接收卡的設計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

介紹了FreeARM7 IP核的基本概況及其接口特點,以LPC2101為原型對該IP核進行了擴展。結合USB 1.1設備控制器IP核和自定制硬件邏輯,構建了一種微控制器功能驗證回路。

2011-04-06 11:41:13 2369

2369

本文介紹的基于Wishbone總線的UART IP核的設計方法,通過驗證表明了各項功能達到預期要求,為IP核接口的標準化設計提供了依據。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 4199

4199

文章采用TOP-DOWN 的方法設計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結構模塊均實現了RTL級建模

2011-07-25 18:10:52 93

93 介紹了SoPC(System on a Programmable Chip)系統的概念和特點,給出了基于PLB總線的異步串行通信(UART)IP核的硬件設計和實現。通過將設計好的UART IP核集成到SoPC系統中加以驗證,證明了所

2012-03-05 17:53:49 63

63 我國集成電路設計業的高速發展帶動IP核市場穩步擴大,國內企業對IP核的數量、質量和服務的需求都在不斷增加。

2012-12-23 12:28:42 1459

1459 定制簡單LED的IP核的設計源代碼

2012-12-23 16:43:53 75

75 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 基于8051內核IP核的應用,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 18:18:32 1

1 一種小規模LCD驅動電路IP核的設計

2017-01-14 12:35:39 11

11 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

電子設計工程 基于FPGA的Flexray IP核通信的研究與實現

2017-08-30 16:08:32 13

13 本文介紹了LCD的通用驅動電路IP核設計,采用自頂向下的設計方法將其劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進行描述,用FPGA實現并通過了仿真驗證。該IP核具有良好的移植性

2017-10-26 17:21:59 15

15 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10744

10744 本文檔內容介紹了建立用戶自己的IP核的操作步驟,供參考

2018-04-03 11:26:51 4

4 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 AD的IP核哪里有?

2018-10-06 15:37:29 469

469 利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP核的市場活動還不規范,但是仍有許多集成電路設計公司從事IP核的設計、開發和營銷工作。

2019-12-19 07:06:00 2168

2168

利用IP核設計電子系統,引用方便,修改基本元件的功能容易。具有復雜功能和商業價值的IP核一般具有知識產權,盡管IP核的市場活動還不規范,但是仍有許多集成電路設計公司從事IP核的設計、開發和營銷工作。

2019-10-08 07:07:00 1949

1949 由于CPLD數字設計結構化的趨勢,將出現針對CPLD不同層次的IP(Intellectual Property)核。各個IP核可重復利用,可大大提高設計能力和效率。國外各大公司都推出了專門的IP核,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。

2020-04-07 09:54:10 4073

4073

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 提出一種可進化IP核的設計和實現方法。這種IP核采用進化硬件的設計思想,將遺傳算法運用于硬件電路的設計中,使電路能根據當前的環境自動進行內部電路的時化,從而生成最有效的電路,并能在普通的FPGA器件

2021-06-22 14:37:40 3382

3382

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

整體而言,作為集成電路產業上游的IP核領域,市場呈現出前所未有的壟斷與集中態勢。2013 年,全球半導體 IP 市場規模達到 24.5億美元,較2012年增長了 11.5%。ARM 以 43.2%的市場占有率遙遙領先,穩居龍頭地位。

2023-10-18 17:02:44 1904

1904 電子發燒友網站提供《HDLC協議IP核的設計與實現.pdf》資料免費下載

2023-11-08 15:45:33 5

5 電子發燒友網站提供《LCD的通用驅動電路IP核設計.doc》資料免費下載

2023-11-15 11:15:37 2

2 Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

在創新加速的浪潮中,為更好地響應客戶群需求, 芯驛電子 ALINX 推出全新 IP 核產品線 ,致力于為高性能數據傳輸和復雜計算需求提供 高帶寬、低延遲 的解決方案。發布的第一批 IP 核包括

2024-10-30 17:39:43 1459

1459

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

電子發燒友App

電子發燒友App

評論