晶心科技今天宣布推出AndesCore? 27系列處理器核心,成為RISC-V指令集架構中領先支持向量擴展架構(RISC-V V-extension)的處理器。

2020-01-03 14:56:38 3521

3521 ARM微處理器的指令集是加載/存儲型的,也即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。

2022-09-02 17:25:48 5709

5709

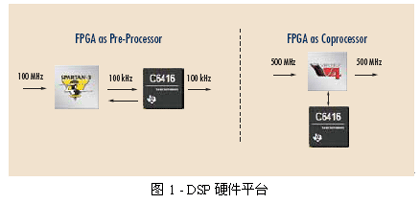

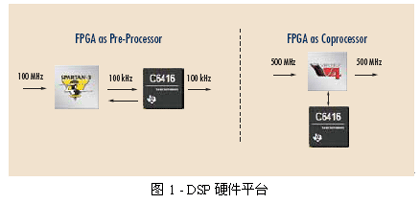

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。 盡管優勢如此明顯

2023-10-21 16:55:02 2727

2727

? ?現代處理器的主要指令集架構(ISA)包括:x86指令集架構、RISC指令集架構。

2023-12-11 09:55:10 6332

6332

FPGA 中已經燒進去了基于RISC-V 處理器(開源CPU),怎么才能把編譯好de.elf文件加載到FPGA 中執行,請各位大神幫我解答一下,感激不盡!

2017-06-21 19:30:45

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

2011-09-29 16:28:38

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

ARM處理器的指令集有哪些分類?

2021-11-30 06:43:07

ARM處理器的指令集有哪些?

2021-11-30 06:53:20

實驗三ARM微處理器指令系統一、實驗目的1. 掌握ARM微處理器指令集的書寫格式;2. 掌握ARM指令的尋址方式;3. 掌握基本的ARM指令的用法;二、實驗內容使用RealView MDK集成開發

2021-12-14 06:51:17

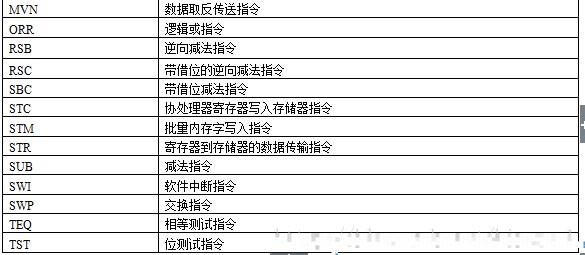

1、ARM微處理器指令系統ARM指令集可以分為跳轉指令、數據處理指令、程序狀態寄存器傳輸指令、Load/Store指令、協處理器指令和異常中斷產生指令。根據使用的指令類型不同,指令的尋址方式分為

2022-04-26 10:30:57

2.ARM微處理器的指令系統ARM微處理器的指令集是加載/存儲型的,即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。ARM

2021-12-20 06:54:28

什么是ARM指令集?ARM指令集有何作用?ARM微處理器的指令集可以分為哪幾大類?分別是什么?

2021-08-17 06:18:17

Hexagon處理器的指令編碼概述本文將講解Hexagon處理器指令以及指令包的二進制編碼,它包含如下幾個部分l指令l子指令lDuplex指令l指令類l指令包l循環包l立即操作數l擴展立即操作數l

2018-09-20 11:53:38

呵呵,s3c2410...在vivi中的s3c2410.h文件中設置時鐘時 有這么一段mrc p15,0,r1,c1,c0,0orr r1,r1,#0xc0000000;mcr p15,0,r1,c1,c0,0這段的每句 的意思是什么?為什么要用到些處理器指令?協處理器指令的作用是干什么?

2019-02-25 12:34:48

滿足以下條件:①處理器的C編譯器能產生可重入代碼;②用C語言可以開/關中斷;③處理器支持中斷,并且能夠產生定時中斷(通常在10~1 000 Hz之間);④處理器能夠支持容納一定量數據的硬件堆棧;⑤處理器

2017-08-14 09:46:10

到FPGA的較低級HDL,或可以通過廣泛存在的C交叉編譯器編譯到支持的微處理器上標準C(帶相關的庫調用)。完整的CoDeveloper開發環境包括與標準C編譯器和調試器(包括微軟公司的Visual

2015-02-02 14:18:19

個能執行幾條指令的處理模塊ip核。它的功能將很簡單。三、把處理器的框圖構建出來,分模塊寫出較為完善的IP核。其中存儲器暫時不用SDRAM,寫驅動IP還是有難度的。四、如果時間允許,給寫好的處理器擴展外部模塊如SDRAM,VGA,TFT等等。五、給FPGA燒寫nios系統。

2017-07-25 18:02:36

代碼加速和代碼轉換到硬件協處理器的方法如何采用FPGA協處理器實現算法加速?

2021-04-13 06:39:25

Processor,數字信號處理器,以下簡稱為DSP處理器。DSP處理器與單片機、ARM這種CPU類似,內部有指令集、ALU等,也有很多外設,如:串口、IIC、SPI、CAN、USB等。用得最多的DSP

2020-09-04 10:31:13

‘b1111011 ——— 7’h7b

隨后的6表示指令的14到12位,即funct3,

協處理器的rtl代碼中可見這個定義,這里的110的順序對應順序為rd,rs1,rs2,使用寄存器的話就把對應

2025-10-31 06:36:26

)和rd(讀)傳遞,不需要讀取存儲器的數據(這樣可精簡化協處理器的控制代碼)

在官方案例的基礎上 新增一個簡單的add指令 c= a + b(主要是將內聯匯編弄清楚,使用rs2)

2025-10-21 14:35:54

存儲器讀寫結果。

調用協處理器的方法:擴展一個用RTL級代碼編寫的協處理器,想個辦法調用這個獨立于流水線的計算單元,即在MCU層面,在編譯器里編寫C語言主函數中包含指定匯編指令的調用,完成驅動的配置。在

2025-10-21 10:39:24

我正在研究一個項目,我們使用PIC32 MZ2048 EFM124處理器和XC32版本1.40編譯器。與c32編譯器相比,xc32編譯器對NOP以外的指令使用分支延遲槽。這導致一些問題,因為分支延遲

2020-05-05 08:02:14

按照這句話的意思,協處理器拓展指令只能實現讀寫操作嗎,官方的案例貌似也只是讀寫指令。那如何用協處理器拓展指令實現更高級運算呢,用內聯匯編嗎

2023-08-16 07:41:54

若不按照官方文檔中的NICE核指令格式自定義指令,主處理器會如何處理該指令?主處理器正常派發該指令給協處理器,報錯或者卡死或者忽略?

2023-08-17 06:41:43

ARM通過增加硬件協處理器來支持對其指令集的通用擴展,通過未定義指令陷阱支持這些協處理器的軟件仿真。簡單的ARM核提供板級協處理器接口,因此協處理器可作為一個獨立的元件接入。高速時鐘使得板級接口非常

2022-04-24 09:36:47

本文根據FPGA的結構特點,圍繞在FPGA上設計實現八位微處理器軟核設計方法進行探討,研究了片上系統的設計方法和設計復用技術,并給出了指令集和其調試方法,提出了一種基于FPGA的微處理器的IP的設計方法。

2021-04-29 06:38:37

有助于使成本和功耗降至最低,而且還能盡可能地加速硬件部署。FPGA 非常適用于執行定點運算,并能在邏輯或基于軟件或硬件處理器的實施方案中創建高度并行的數據路徑解決方案。Virtex?-5 FPGA 產品

2018-08-03 11:15:23

mrc p15,0,r1,c1,c0,0s3c2410芯片手冊上只是說這個指令是把p15協處理器中c1和c0寄存器里面的值傳給r1.但是協處理器的結構是什么樣的?c1和c0兩個寄存器里的值怎么存到

2015-01-23 14:05:28

請問FPGA協處理器有哪些優勢?

2021-05-08 08:29:13

本帖最后由 一只耳朵怪 于 2018-6-13 16:51 編輯

如何使用預處理指令#pragma禁止優化某段代碼?哪里有c2000編譯器的預處理指令的說明資料?

2018-06-13 04:57:37

請問,DM8148 處理器的C語言指令集在哪個文檔中描述的?TMS320C674x DSP?CPU and Instruction Set 文檔中只講了匯編指令集。謝謝

2018-05-28 03:00:01

嗨,大家好 我是sandeep,是FPGA的新手。我目前正在開發一個項目,開發一個模塊,負責處理從PLC接收的數據的加密和解密任務。我需要為沒有處理器的項目選擇FPGA。那么請你幫我選擇FPGA

2019-05-16 10:20:42

微處理器指令集設計垂直指令格式指令類型及其使用頻度CISC指令集特點 RISC指令集特點指令集設計的發展微處理器指令集設計的基本要求處理器設計的藝術就

2008-10-29 17:13:03 64

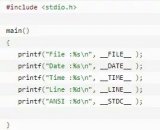

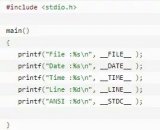

64 在將一個C源程序轉換為可執行程序的過程中, 編譯預處理是最初的步驟. 這一步驟是由預處理器(preprocessor)來完成的. 在源流程序被編譯器處理之前, 預處理器首先對源程序中的"宏(m

2009-09-20 18:17:46 47

47 本文利用頻域抽取基四算法,運用靈活的硬件描述語言-Verilog HDL 作為設計主體,設計并實現一套集成于FPGA 內部的FFT 處理器。FFT 處理器的硬件試驗結果表明該處理器的運算結

2010-01-20 14:33:54 40

40 ARM微處理器的指令系統教材 PPT

ARM處理器是基于精簡指令集計算機(RISC)原理設計的,指令集和相關譯碼機制較為簡單。ARM7TDMI(-S)具有32位ARM指令集和16位Thumb指令

2010-02-21 09:18:23 70

70 VLIW處理器的設計與實現 摘要! 介紹了基于FPGA 實現VLIW微處理器的基本方法# 對VLIW微處理器具體劃分為C 個 主要功能模塊$ 依據FPGA的設計思想#采用自頂向下和文本與原理圖相結合的流水線方式的設計方 法# 進行VLIW微處理器的5 個模塊功能設計# 從而最終實現

2011-01-25 19:05:11 21

21 超長指令字VLIW微處理器架構采用了先進的清晰并行指令設計。VLIW微處理器的最大優點是簡化了處理器的結構,刪除了處理器內部許多復雜的控制電路,它能從應用程序中提取高度并行的

2011-09-26 14:12:40 1570

1570

ARM微處理器的指令集是加載/存儲型的,也即指令集僅能處理寄存器中的數據,而且處理結果都要放回寄存器中,而對系統存儲器的訪問則需要通過專門的加載/存儲指令來完成。 ARM微處

2012-05-22 16:54:53 1604

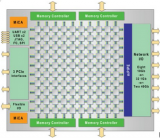

1604 SoC FPGA使用寬帶互聯干線鏈接,在FPGA架構中集成了基于ARM的硬核處理器系統(HPS),包括處理器、外設和存儲器接口。Cyclone V SoC FPGA在一個基于ARM的用戶可定制芯片系統(SoC)中集成了

2012-09-04 14:18:14 5609

5609

電子發燒友網核心提示: 獲獎的Nios II 嵌入式處理器C語言至硬件(C2H)加速編譯器將對時間要求較高的ANSI C函數轉換為FPGA中的硬件加速器,從而提高了性能。 特性: (1)ANSI/ISO C 代碼按鍵

2012-10-17 14:29:34 2394

2394

摩爾定律持續有效,半導體工藝技術步入深亞納米時代,為處理器和FPGA的融合提供了無限可能。Intel于2010年11月發布的凌動E600 C系列,即原研發代號為“Stellarton”的可配置凌動

2015-02-04 09:37:05 1320

1320 本文主要研究如何利用FPGA實現FFl’算法,研制具有自主知識產權的FFT

信號處理器

2016-03-21 16:22:52 44

44 基于FPGA的傳像光纖束圖像預處理器,下來看看

2016-08-30 15:10:14 12

12 同時多線程處理器的指令調度器設計_李樂

2017-01-08 14:55:45 0

0 多層異構粗粒度可重構處理器的編譯器后端設計_劉毅超

2017-01-07 20:43:12 1

1 有人認為諸如圖形處理器(GPU)和Tilera處理器等多核處理器在某些應用中正逐步替代現場可編程門陳列(FPGA)。理由是這些多核處理器的處理性能要高很多,例如,由于GPU起初主要負責圖形繪制,因此,其尤其善于處理單精度(SP)及(某種情況下)雙精度(DP)浮點(FP)運算。

2017-02-11 11:15:11 1342

1342

還是Intel處理器。在這一點上我們見過太多測試了,今天看點別的——大家別只看到Intel有最好的處理器,他們還有最好的編譯器,在Intel編譯器下AMD Ryzen處理器與Intel處理器的差距更大了。

2017-05-10 15:45:57 2002

2002 AMD 加速處理器(APU)產品線以及 AMD 獨立圖形處理器(GPU)加速器產品線。PGI 將與 AMD 密切合作,擴大 PGI Accelerator 指令式編譯器產品功能,直接生成 AMD

2017-09-14 15:10:41 0

0 本手冊描述了如何在Rowley Systems 上使用CrossWorks C 編譯器來創建、編譯,和調試MAXQ1103 微處理器上的應用目標程序。MAXQ1103 是美信公司特為金融終端應用而設

2017-09-22 14:17:58 17

17 本章將幫助讀者在ARM處理器上編寫高效的C代碼。本章涉及的一些技術不僅適用于ARM處理器,也適用于其他RISC處理器。本章首先從ARM編譯器及其優化入手,講解C編譯器在優化代碼時所碰到的一些問題

2017-10-17 17:22:26 2

2 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 基于ARM微處理器的指令系統

2017-10-25 11:35:38 5

5 協處理器(coprocessor),一種芯片,用于減輕系統微處理器的特定處理任務。協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。

2017-11-10 15:56:35 3161

3161 采用簡單有效的指令編碼方式縮小了代碼體積,同時給出了單周期操作多個堆棧元素的解決方法.該處理器采用FPGA實現,在XC5VLX110T芯片上的運行時鐘頻率最高達到146.7MHz。最后給出了設計的軟件仿真與硬件綜合結果。

2017-11-18 12:39:14 3992

3992 為了能夠靈活地驗證和實現自主設計的基于NoC的多核處理器,縮短NoC多核處理器的設計周期,提出了設計集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設計/驗證平臺。分析和評估了

2017-11-22 09:15:01 5266

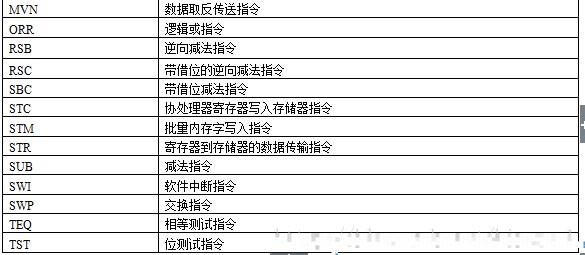

5266 協處理器共有68條不同的指令,匯編程序在遇到協處理器指令助記符時,都會將其轉換成機器語言的ESC指令,ESC指令代表了協處理器的操作碼。協處理器指令在執行過程中,需要訪問內存單元時,CPU會為其形成內存地址。協處理器在指令執行期間內利用數據總線來傳遞數據。

2018-01-09 14:58:28 2451

2451

數字信號處理軟件中循環程序在執行時間上占有很大比例,用指令緩沖器暫存循環代碼可以減少程序存儲器的訪問次數,提高處理器性能。在VLIW處理器指令流水線中增加一個支持循環指令的緩沖器,該緩沖器能夠緩存

2018-02-02 17:29:29 0

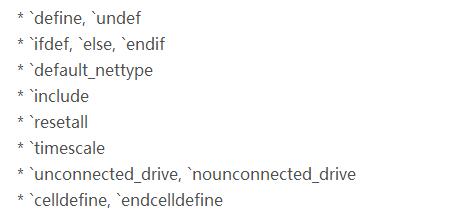

0 以`(反引號)開始的某些標識符是編譯器指令。在Verilog 語言編譯時,特定的編譯器指令在整個編譯過程中有效(編譯過程可跨越多個文件),直到遇到其它的不同編譯程序指令。

2018-03-23 13:40:40 16468

16468

本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 12

12 在下面的學習中我們對PIC系列單片機選用MPLAB軟件編寫代碼,編譯器選用CCS編譯器,不管是51單片機系統的開發還是PIC系列單片機的開發,其基礎全是C語言(或者匯編語言),所不同的是各個編譯器擁有不同的數據類型定義和各種特殊的處理器指令以及預處理指令。

2019-01-28 16:07:53 18

18 編譯器對C程序的處理可以明確地分為兩步。第一步由預編譯器完成。以#開頭的預編譯指令可能會影響編譯器設置或者進行文本替換。注意,預編譯器變量(標識符)和正常的C變量是不一樣的。預編譯完成之后,編譯器將不會看到任何預編譯指令或標識符。下面介紹常見的預編譯指令。

2019-06-05 17:52:00 2

2 超長指令字VLIW微處理器架構采用了先進的清晰并行指令設計。VLIW微處理器的最大優點是簡化了處理器的結構,刪除了處理器內部許多復雜的控制電路,它能從應用程序中提取高度并行的指令數據,并把這些機器

2020-01-31 16:55:00 1576

1576

C/C++ 程序中的源代碼中包含以 # 開頭的各種編譯指令,這些指令稱為預處理指令。預處理指令不屬于 C/C++ 語言的語法,但在一定意義上可以說預處理擴展了 C/C++。

2020-11-29 10:14:38 2793

2793 本章將介紹Nios 處理器的硬件開發環境和硬件開發的整個流程。一個簡單Nios 開發系統包括Nios 嵌入式處理器和連接外設的輸入輸出設備, 硬件開發就是利用SOPC Builder 整合處理器

2021-01-15 15:57:49 5

5 EE-149: 調試Blackfin?處理器編譯C 源代碼

2021-03-19 10:02:58 11

11 用于Blackfin?處理器的CrossCore?Embedded Studio 2.9.0 C/C++編譯器和庫手冊

2021-04-26 17:17:12 1

1 適用于Blackfin處理器的VisualDSP++?5.0 C/C++編譯器和庫手冊

2021-05-11 11:53:46 10

10 用于TigerSHARC處理器的VisualDSP++?5.0 C/C++編譯器和庫手冊

2021-05-13 19:07:27 13

13 用于SHARC?處理器的CrossCore?Embedded Studio 2.9.0 C/C++編譯器手冊

2021-05-17 08:46:26 6

6 適用于SHARC?處理器的VisualDSP++?5.0 C/C++編譯器手冊

2021-05-18 12:32:31 3

3 適用于ADSP-219x處理器的VisualDSP++3.5 C/C++編譯器和庫手冊

2021-05-24 09:02:55 2

2 針對超標量處理器中長周期執行指令延遲退休及持續譯碼導致的重排序緩存(ROB)阻塞問題,提出一種指令亂序提交機制。通過設計容量可配置的多緩存指令提交結構,實現存儲器操作指令和ALU類型指令的分類退休

2021-06-07 11:39:40 13

13 編譯時,特定的編譯器指令在整個編譯過程中有效(編譯過程可跨越多個文件),直到遇到其它的不同編譯程序指令。不完整的標準編譯器指令如下: 下面分解一下,每個指令單獨說明一下: ’define和’undef 1.’define指令 ’define指令用于文本替換,它很像C語言中#define指令。它生成一

2021-11-03 09:31:56 4784

4784

和AMD的處理器就是基于復雜指令集的。精簡指令集中常見處理器有IBM和ARM兩類。具體單片機處理器舉例:80C51單片機 ——intel (具體系列不知道)stm32——ARM Cortex M0 M3 M4 M7所以當別人問你有沒有用過ARM的時候,如果你用過stm32,那你就可以很有

2021-11-19 12:06:06 10

10 協處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔通常由主處理單元執行的運算。通常,協處理器功能在硬件中實現以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實現指令的方式,從而實現代碼加速。

2022-10-27 12:41:27 1286

1286 在嵌入式系統開發中,C預處理器是非常重要的一部分,可以在編譯之前對源代碼進行宏替換、條件編譯和包含等處理。在本文中,我們將介紹嵌入式C預處理器的基本概念和常用指令。

2023-04-13 16:11:06 1490

1490 大家天天都在使用手機,你知道你的手機使用的什么處理器?處理器又是何種架構呢?今天筆者就來談談處理器的架構和指令集。 我們知道一臺手機最重要的就是處理器,也就是處理器,那么什么是處理器呢? 處理器就是

2023-04-26 11:40:34 8363

8363

CA850 Ver.3.20 用于鏈接指令的 C 編譯器包

2023-05-04 19:04:22 0

0 在嵌入式系統開發中,C預處理器是非常重要的一部分,可以在編譯之前對源代碼進行宏替換、條件編譯和包含等處理。

2023-05-20 15:14:14 807

807 MIPS——內部無互鎖級微處理器( Microprocessor without interlocked piped stages ),采用RISC 指令集,所有的指令長度相同,運行周期也相同。

2023-06-27 16:56:17 3482

3482

Hot Chips 2023大會上,Intel首次公布了一款RISC指令集處理器,擁有獨特的8核心528線程規格。

2023-09-01 15:02:49 1856

1856

所有的預處理器命令都是以井號(#)開頭。它必須是第一個非空字符,為了增強可讀性,預處理器指令應從第一列開始。

2024-03-01 12:16:24 1619

1619

C預處理器(C Pre-Processor)也常簡寫為 CPP,是一個與 C 編譯器獨立的小程序,預編譯器并不理解 C 語言語法,它僅是在程序源文件被編譯之前,實現文本替換的功能。

2024-03-12 14:14:09 1458

1458

嵌入式微處理器是一種特殊類型的微處理器,它被設計用于嵌入在電子設備中,執行特定的任務。嵌入式微處理器的指令系統是一組機器指令集合,用于告訴處理器如何執行特定的任務。每個指令都是由一系列比特位組成

2024-05-04 11:39:00 1398

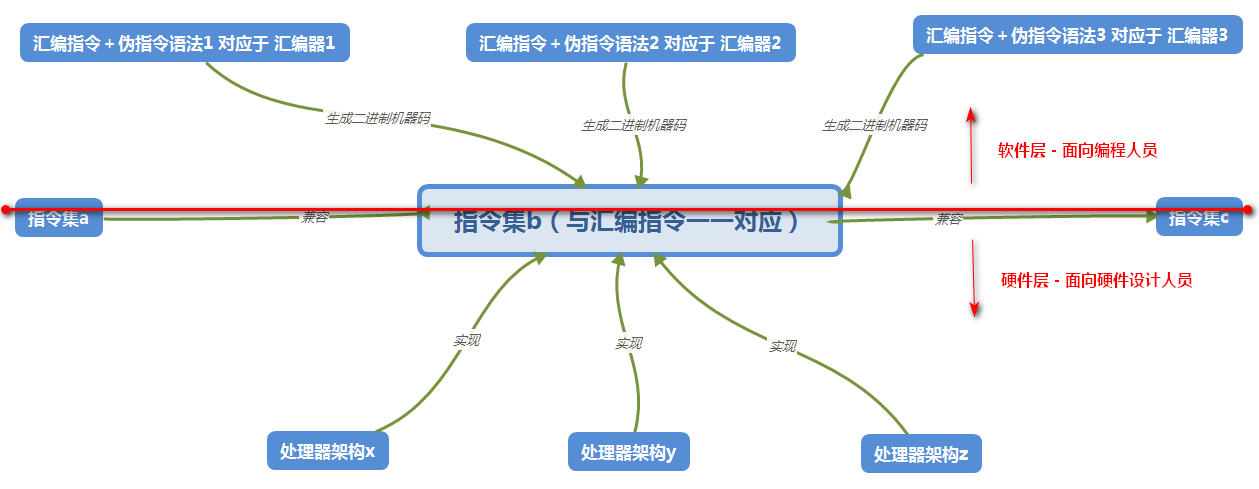

1398 微處理器的指令集架構(Instruction Set Architecture,ISA)是計算機體系結構中至關重要的部分,它定義了微處理器能夠執行的操作和指令的集合,以及這些指令如何被組織、存儲

2024-08-22 10:53:45 3256

3256 ARM處理器的指令集是一個龐大而復雜的系統,它涵蓋了多種類型的指令,用于實現數據處理、程序控制、內存訪問等多種功能。

2024-09-10 11:15:14 2198

2198 微處理器的指令集和指令系統是兩個緊密相關但又有所區別的概念,它們在微處理器的設計和運行中扮演著不同的角色。以下是對這兩個概念的詳細解析,旨在深入探討它們之間的不同點。

2024-10-05 14:57:00 1603

1603 微處理器的指令集是微處理器設計和功能實現的基礎,它決定了微處理器能夠執行哪些操作以及這些操作如何被組織和執行。隨著計算機技術的不斷發展,微處理器的指令集也在不斷更新和擴展。

2024-10-05 14:58:00 1507

1507 微處理器的指令集架構(Instruction Set Architecture,ISA)是計算機體系結構中的核心組成部分,它定義了計算機能夠執行的指令集合、數據類型、寄存器、內存訪問方式等,是連接

2024-10-05 14:59:00 1851

1851 微處理器,作為現代計算機的核心部件,負責執行存儲在內存中的指令,完成各種計算和控制任務。指令的執行過程不僅體現了微處理器的設計思想和架構特點,還直接影響到計算機的性能和效率。

2024-10-05 15:07:00 2837

2837 微處理器指令的獲取是計算機執行程序過程中的關鍵環節,它決定了微處理器如何對數據和指令進行處理。以下將詳細闡述微處理器指令的獲取過程,包括指令的來源、存儲位置、讀取方式以及相關的硬件和軟件支持。

2024-10-05 15:16:00 1598

1598 電子發燒友網站提供《EE-149: 調試Blackfin處理器編譯C源代碼.pdf》資料免費下載

2025-01-08 14:48:10 0

0

電子發燒友App

電子發燒友App

評論