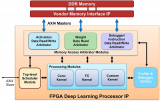

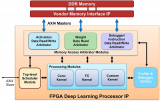

如果你已經在用 MATLAB 做深度學習,那一定知道它的訓練和仿真體驗非常絲滑。但當模型要真正落地到 FPGA 上時,往往就會卡住:怎么把網絡結構和權重優雅地搬到硬件里?

2025-09-24 10:00:11 4215

4215

由于FPGA技術和ARM技術應用越來越廣泛,通過設計并行總線接口來實現兩者之間的數據交換,可以較容易地解決快速傳輸數據的需求,因此設計滿足系統要求的FPGA并行總線顯得尤為重要。本文設計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用.

2013-08-15 10:44:19 9148

9148

高速、高精度優勢的同時也使得工程師避免了編寫FPGA硬件代碼的繁瑣。科梁結合OPAL-RT先進的解算器和模型及科梁的工程經驗,為客戶提供從功能驗證到系統測試電機模型和測試解決方案。

2017-08-09 10:52:21 3639

3639

7 系列 FPGA 幀 ECC 邏輯可檢查配置幀數據的單位或雙位錯誤。它可使用基于幀數據( BitGen 生成)計算的 13 位漢明碼校驗值

2017-09-28 06:04:00 8412

8412 圖像處理算法在各種場景中都有廣泛應用,借助于FPGA并行計算的優勢可以將算法性能有效提升,但為了提升系統整體性能,僅僅提升某一部分的性能是不夠的,一個好的方法是在FPGA內實現全部視頻輸入輸出接口

2020-11-04 12:07:05 4653

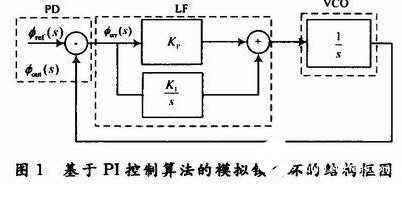

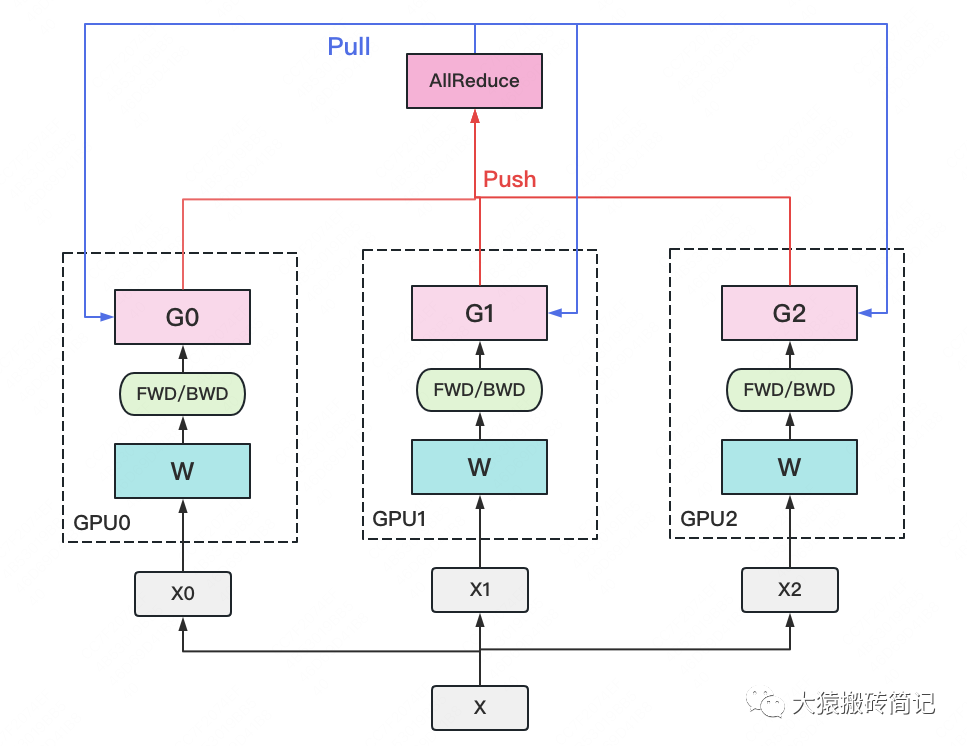

4653 在之前的內容中,我們已經介紹過流水線并行、數據并行(DP,DDP和ZeRO)。 今天我們將要介紹最重要,也是目前基于Transformer做大模型預訓練最基本的并行范式:來自NVIDIA的張量模型

2023-05-31 14:38:23 4295

4295

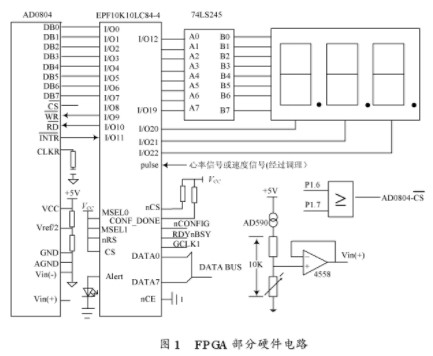

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 5867

5867

今天我們看的這篇論文介紹了在多FPGA集群上實現高級并行編程的研究,其主要目標是為非FPGA專家提供一個成熟且易于使用的環境,以便在多個并行運行的設備上擴展高性能計算(HPC)應用。

2024-07-24 14:54:16 2361

2361 在2410的NAND控制器里有硬件ECC模塊,看2410的手冊中是這么介紹的:ECC generator block executes the followings:1. When MCU

2019-05-20 02:32:08

嵌入式MCU存儲器ECC工作原理注:摘自汽車電子 expert 成長之路公眾號來簡單聊一聊ECC,ECC 是“Error Correcting Code”的簡寫,中文名稱是“錯誤檢查和糾正”。ECC

2021-11-03 08:26:19

并行測試的實現途徑分為軟件方式和硬件方式。用軟件方式實現并行測試,關鍵是對測試任務的分解和調度,但可能會產生競爭或者死鎖現象。因此,在測試資源有限并且任務分解和調度算法不成熟的情況下,用軟件實現并行

2019-08-16 06:50:47

不要花多大的心思。(3)硬件協議以下是PC上的DB25打印接口。其中的2到9引腳為8bit數據的傳輸通道。在EPP模式下,這個8bit通道是雙向的。其他比較重要的引腳有。17 地址選通 PC到FPGA

2019-08-06 05:00:00

最佳情況的電源系統是有好處的,因為在許多方面仍有太多的不確定性,比如在硬件設計完成和功耗可以測量之前,靜態小電流狀態與全速工作狀態之間的動態負載要求將如何波動。 采用并行工程(CE)技術,可以為在項目

2018-10-08 15:17:52

FPGA的并行多通道激勵信號產生模塊FPGA的并行多通道激勵信號產生模塊.docx

2012-08-11 10:35:50

輸出。這兩個芯片的管腳雖然很多,但大多數都是與硬件設計有關。其實幾乎所有的并行ADC和并行DAC與FPGA之間的接口只有一條時鐘線與一組數據總線,數據總線的位寬即為ADC/DAC的位數。每個時鐘周期

2020-09-27 09:40:08

`fpga基礎篇(二):三大并行結構最近小編比較忙,所以這期給大家介紹一個基礎篇,比較簡單,但卻是FPGA編程的基礎。我們知道FPGA與單片機最大的區別就是FPGA是并行執行的,而單片機是串行的,說

2017-04-13 10:23:27

并行編程模型是并行計算,尤其是并行軟件的基礎,也是并行硬件系統的導向,在面臨多核新挑戰的情況下,什么樣的并行編程模型在未來能成為主流,還很難說。至少到目前,還處于百家爭鳴的時代,很多模型提出,很多在應用,下面我們簡單介紹一下當前的并行編程模型現狀。

2019-07-11 08:03:33

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊主要介紹從動并行(SP)加載模式以及從動并行級聯加載模式的使用。內容包括使用從動并行加載模式的軟件配置,使用從動并行加載模式和從動并行級聯加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動并行加載的主控器件時的軟件工作流程。

2022-10-27 07:31:16

并行計算。在進行FFT 這類并行運算為主的算法時,采用FPGA的優勢不言而喻。用FPGA實現FFT算法進行諧波檢測成為了一大熱點。 以往FPGA的設計主要依靠硬件描述語言來完成。Xilinx公司推出了專門

2019-06-21 06:25:23

多核體系結構的硬件仿真平臺FPGA資源消耗隨計算核數目成線性增加。這里提出的對稱多核體系結構FPGA仿真模型,解耦合計算核數目與系統硬件開銷的線性關系,其核心設計思想是:在構建仿真系統時,使用一個與目標系統中單個計算

2019-08-23 07:06:56

等串行總線接口只能實現FPGA 和ARM 之間的低速通信 ;當傳輸的數據量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數據傳輸.

2019-09-17 06:21:10

的。多核控制器可以很好地滿足這種需求,然而對于最終的并行處理而言,它的性能很難超過FPGA。FPGA為自動化測試系統提供了無與倫比的性能和可靠性,是目前并行化編程計算硬件中的佼佼者。LabVIEW

2014-12-12 16:02:30

ARM周期模型工具提供了一個集成環境,該環境將系統驗證與硬件開發流程并行。

周期模型編譯器采用RTL硬件模型并創建一個高性能的可鏈接對象,稱為周期模型,它是周期和寄存器準確的。

周期模型編譯器提供了與驗證環境交互的API:

2023-08-16 06:30:07

DSP芯片組成并行處理系統。另外,為充分發揮 DSP芯片在復雜算法處理上的優勢及FPGA在大數據量的底層算法上的優勢,設計了一種基于FPGA控制的多DSP并行處理系統。1 系統設計基于FPGA控制的多

2019-05-21 05:00:19

本文介紹一種使用硬件描述語言VHDL來實現基于Petri網的并行控制器的方法。首先使用Petri網對問題進行建模,并對模型進行分析和控制,獲得控制器的Petri網模型;然后用VHDL對Petri網

2019-08-16 07:52:03

本文以并行多通道信號產生模型為依據,設計并實現了以FPGA為核心器件的并行多通道信號產生模塊,主要包括FPGA系統設計和多通道波形產生模塊設計。通過模塊測試后發現,該模塊具備產生高質量并行多通道激勵信號的能力。

2021-04-29 06:17:38

本帖最后由 人間煙火123 于 2018-6-15 10:30 編輯

現在想把DM365的ECC由原來的軟件ECC校驗改為硬件校驗,在TI提供的內核和u-boot中如何改?在

2018-06-15 03:28:38

Mali T604 GPU的結構是由哪些部分組成的?Mali T604 GPU的編程特性有哪些?Mali GPU的并行化計算模型是怎樣構建的?基于Mali-T604 GPU的快速浮點矩陣乘法并行化該如何去實現?

2021-04-19 08:06:26

本帖最后由 一只耳朵怪 于 2018-6-12 11:56 編輯

ECC校驗是一種內存糾錯原理,它是現在比較先進的內存錯誤檢查和更正的手段。ECC內存即糾錯內存,簡單的說,其具有發現錯誤

2018-06-12 10:06:41

proteus中有仿真模型的并行插口怎么繪制?

2019-04-23 20:14:43

上EasyGo FPGA Solver中的FPGA Coder解算軟件,可以將用戶靈活搭建的模型直接下載至FPGA中運行,而不需要進行FPGA的編譯,最

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

采用軟硬件結合的方法,給出一種基于VLIW 的并行可配置橢圓曲線密碼體制(ECC)專用指令協處理器架構。該協處理器采用點加、倍點并行調度算法,功能單元微結構采

2009-03-20 16:14:02 25

25 提出一種適用于SMP 集群的混合MPI+OpenMP 并行編程模型。該模型貼近于SMP 集群的體系結構且綜合了消息傳遞和共享內存2 種編程模型的優勢,能獲得較好的性能。討論該混合模型的實

2009-03-30 09:28:40 32

32 ECC 數字簽名算法是目前的研究熱點之一。本文根據ECC 數字簽名算法的相關理論,使用Verilog 語言實現了其完整方案,并給予相應的優化。給出了關鍵部分的仿真結果。

2009-09-12 15:39:31 16

16 算法隱含并行性的物理模型:利用物理學原理對算法的隱含并行性進行了分析,提出算法的不確定性和高熵態是隱含并行性出現的根源,但算法的隱含并行性會導致算法結果的不確定

2009-10-21 08:23:07 10

10 橢圓曲線密碼體制(Elliptic Curve Cryptosystem,ECC)是目前已知的所有公鑰密碼體制中能提供最高比特強度(strength-per-bit)的一種公鑰加密體制。研究橢圓曲線密碼算法的芯片設計有較大

2010-08-06 15:50:36 20

20 介紹了一種二進制補碼快速并行平方器的設計方法,并給出了一個6位二進制補碼平方器的例子及在MAX+PLUS II 10.0環境下的仿真結果。

關鍵詞:FPGA,二進制補碼,平方器

2009-05-17 12:59:26 3103

3103

什么是內存ECC校驗

2009-12-25 14:28:00 2512

2512 什么是ECC內存

ECC是“Error Checking and Correcting”的簡寫,中文名稱是“錯誤檢查和糾正”。ECC是一種能夠實現“錯誤檢查和糾正”的技術,ECC內存就是應用了這種技術的

2010-01-12 15:42:34 1142

1142 并行測試的實現途徑分為軟件方式和硬件方式。用軟件方式實現并行測試,關鍵是對測試任務的分解和調度,但可能會產生競爭或者死鎖現象。因此,在測試資源有限并且任務分解和調度算法不成熟的情況下,用軟件實現并行測試會很困難。用硬件方式實現并行測試時,需

2011-01-21 00:17:44 1388

1388

本文將ECC校驗算法通過硬件編程語言VHDL在AheraQuanusⅡ7.0開發環境下進行了后仿真測試,實現了NANDFlash的ECC校驗功能。本程序可實現每256Byte數據生成3ByteECC校驗數據,且通過與原始ECC數據

2011-07-17 10:55:20 7149

7149

根據某移動公司本地傳輸現網的結構特點以及ECC 管理的現狀,對 ECC 子網的優化配置方法進行詳細規范。建立本地傳輸網ECC 子網劃分的模型,對本地傳輸網的ECC 配置方法進行闡述。

2011-08-02 16:54:07 20

20 本文介紹的基于PCI總線的FPGA計算平臺的系統實現:通過在PC機上插入擴展PCI卡,對算法進行針對并行運算的設計,提升普通PC機對大計算量數字信號的處理速度。本設計采用5片FPGA芯片及

2011-08-21 18:05:31 2415

2415

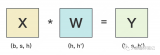

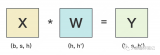

針對復雜算法中矩陣運算量大, 計算復雜, 耗時多, 制約算法在線計算性能的問題, 從硬件實現角度, 研究基于FPGA/Nios-Ⅱ的矩陣運算硬件加速器設計, 實現矩陣并行計算。首先根據矩陣運算

2011-12-06 17:30:41 89

89 通過 labview fpga定制硬件。

2016-05-17 17:47:59 28

28 基于FPGA的嵌入式多核處理器及SUSAN算法并行化

2016-08-30 18:11:47 24

24 基于FPGA的ECC快速算法研究及設計_陳俊杰

2017-01-07 19:08:43 2

2 基于FPGA的ARM并行總線研究與仿真

2017-01-24 16:54:24 21

21 一種基于門限ECC的PKI_CA模型的設計_毛穎慧

2017-03-19 11:46:13 0

0 本文介紹了FPGA電源設計并行工程的合理性,講解了并行工程(CE)技術及其作用,討論了FPGA電源系統設計的復雜性和不確定性。

2017-10-13 13:00:35 5

5 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 AES和ECC的混合加密系統的設計

2017-10-31 09:04:25 11

11 是怎么工作的! 注:這里的并行運算指的是一個模型在不同的參數配置下運行多次,并非把一個模型拆分在不同的核上并行的內容。

2017-11-15 12:16:17 6438

6438

7 系列 FPGA 幀 ECC 邏輯可檢查配置幀數據的單位或雙位錯誤。它可使用基于幀數據( BitGen 生成)計算的 13 位漢明碼校驗值。 在讀回過程中,幀 ECC 邏輯可計算使用所有幀位(包括

2017-11-15 12:25:01 2536

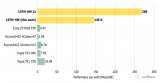

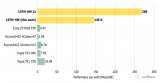

2536 限的并行性。針對這個問題,普渡大學的研究人員提出了一種LSTM在Zynq 7020 FPGA的硬件實現方案,該方案在FPGA中實現了2層128個隱藏單元的RNN,并且使用字符級語言模型進行了測試。該實現比嵌入在Zynq 7020 FPGA上的ARM Cortex-A9 CPU快了21倍。

2017-11-15 13:30:06 2522

2522

NI LabVIEW圖形化編程方法不僅省時,還很適合對多核處理器和其他并行硬件[如:現場可編程門陣列(FPGA)]進行編程。 其中一項優勢是:通過2個、4個或更多核將應用程序自動擴展至CPU,通常

2017-11-16 19:30:41 1927

1927

針對信號處理數據量大、實時性要求高的特點,從實際應用出發,設計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 3060

3060

基于串行異步收發器(UART)的通信中經常用到循環冗余校驗(CRC),常見的CRC校驗電路多為串行校驗,校驗所需時鐘周期較多,基于查找表或輸入矩陣轉換的并行算法,需要存儲余數表,占用大量的硬件資源

2017-11-18 11:24:54 2395

2395

一種可用于模型參數求解的并行迭代模型MRI。MRI模型在保持Map以及Reduce階段的基礎上,新增了Iterate階段以及相關通信協議,實現了迭代過程中模型參數的更新、分發與迭代控制;通過對MapReduce狀態機進行增強,實現了節點任務的重用,避免了迭代過程中節點任務

2017-11-23 15:04:35 1

1 重復計算稀疏矩陣向量乘,提出了新的并行計算結構。實驗分析表明,提出的架構提高了Wiedemannn算法中稀疏矩陣向量乘的并行性,同時充分利用了FPGA的片內存儲器和吉比特收發器,與目前性能最好的部分可重構計算PR模型相比,實現了2.65倍的加速性能。

2017-11-27 10:45:14 0

0 針對并行軟件的狀態空間規模大導致測試難度大的問題,提出一種基于著色Petri網(CPN)的針對待測行為的并行模型化簡方法。首先,將原模型根據模型中出現的并發變遷、同步變遷、分叉庫所、匯合庫所等特殊

2017-12-03 10:14:26 0

0 兩個顯著問題:(1)如何讓軟件設計充分發掘硬件的并行處理能力,從而提高系統的性能;(2)在系統硬件規模不斷擴大、復雜度越來越高的情況下,如何保證系統的可靠性. 任務并行程序設計模型已成為并行程序設計的主流,其通

2018-01-12 09:35:01 0

0 ,常規做法是利用插值和抽取的方法實現數字信號的變采樣處理,這種方法實現復雜,硬件成本高。文中提出了一種高速并行成型濾波器的FPGA實現方法,這種基于群延時結構的查找表算法,所需的查找表只需存儲單位沖擊響應的采樣值,

2018-02-23 10:14:22 0

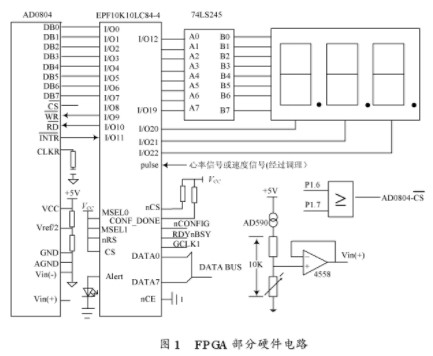

0 根據課題要求,設計FPGA部分硬件電路如圖1所示。FPGA芯片選用Altera公司的中檔器件FLEX-EPF10K10LC84-4,他是基于SRAM LUT結構的FPGA器件。根據傳送數據的方式

2019-08-21 08:01:00 6288

6288

作為集成電路設計領域現場可編程門陣列 (FPGA) 技術的創造者之一,賽靈思一直積極推廣高層次綜合 (HLS) 技術,通過這種能夠解讀所需行為的自動化設計流程打造出可實現此類行為的硬件。賽靈思剛剛推出了一本專著,清晰介紹了如何使用 HLS 技術來創建優化的硬件設計。

2018-11-10 11:01:05 3178

3178 串行總線接口只能實現FPGA 和ARM 之間的低速通信 ;當傳輸的數據量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數據傳輸.

2019-08-08 15:37:50 7134

7134

ECC的英文全稱是“ Error Checking and Correcting”(錯誤檢查和糾正),從這個名稱就可以看出它的主要功能就是“發現并糾正錯誤”。

2020-03-22 13:39:00 52409

52409 本文檔的主要內容詳細介紹的是FPGA的硬件電路設計教程和FPGA平臺資料簡介包括了:FPGA技術概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設計;V4LX160 FPGA平臺介紹;

2020-07-06 18:11:22 177

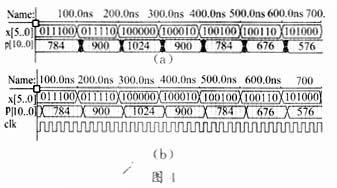

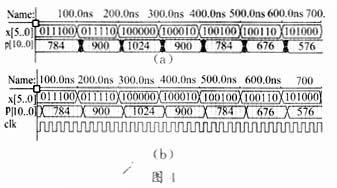

177 由于Signal Compiler模塊可以自動地將DSPbuilder建立的模型文件轉化為QuartusⅡ環境下的工程文件,因此,該設計在完成軟件仿真后結合FPGA試驗箱,在生成的工程下進行引腳

2020-08-21 10:55:00 3048

3048

本文檔的主要內容詳細介紹的是FPGA的硬件基礎教程免費下載包括了:1、 FPGA 的發展歷史,2、 FPGA 的結構,3、 FPGA 芯片選型

2020-12-09 13:47:50 38

38 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA的RAM存儲課件和工程文件。

2020-12-10 15:27:00 31

31 出了四核心嵌入式并行處理器FPEP的結構設計并建立了FPGA驗證平臺.為了對多核處理器平臺性能進行評測,提出了基于OpenMP的3種可行的圖像處理領域的經典算法SUSAN算法的并行化方法:直接并行化

2021-02-03 16:26:00 8

8 用軟件實現 CRC 校驗碼計算很難滿足高速數據通信的要求 ,基于硬件的實現方法中 ,有串行經典算法 LFSR 電路 以及由軟件算法推導出來的其它各種并行計算方法。以經典的LFSR 電路為基礎 ,研究

2021-03-28 09:34:24 30

30 提出了一種基于FPGA實現的全并行結構FFT設計方法,采用XILINX公司最新器件VirtexII Pro,用硬件描述語言VHDL和圖形輸入相結合的方法,在ISE6.1中完成設計的輸入、綜合、編譯

2021-03-31 15:22:00 11

11 /ASCⅠ和¢PU/FPGA等簡述了異構混合并行編程模型隨著各類異構混合結構的發展而做岀的改變,異構混合并行編程模型可以是對現有的一種語言進行改造和重新實現,或者是現有異構編程語言的擴展,或者是使用指導性語句異構編程,或者是容器模式協同

2021-05-13 10:30:35 13

13 K9F2G08 。特點: 系統配合 FatFs 實現了壞塊管理,硬件ECC,軟件 ECC 糾錯2、代碼分析2.1、擦寫均衡分析 在create_chain 函數中實現,每次分配都由當前scl 指向的 free cluster 開始,逐塊檢查,是否有可用 cluster 存在。如果沒...

2021-11-20 12:51:03 25

25 ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2022-04-21 08:55:22 8245

8245 本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了復現以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 1825

1825

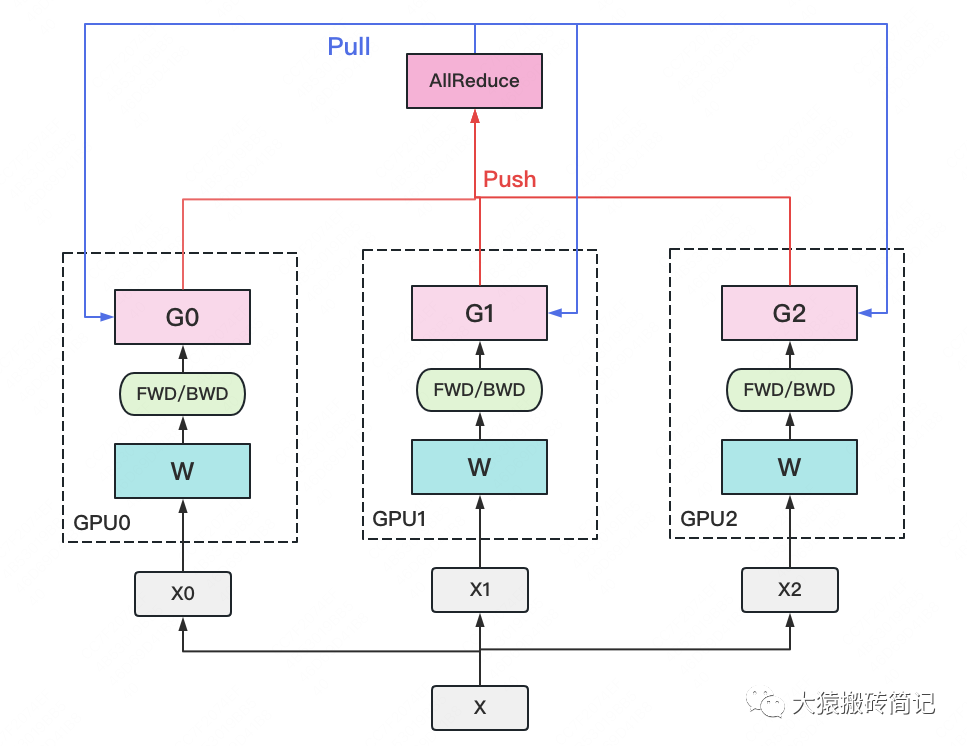

數據并行的核心思想是:在各個GPU上都拷貝一份完整模型,各自吃一份數據,算一份梯度,最后對梯度進行累加來更新整體模型。理念不復雜,但到了大模型場景,巨大的存儲和GPU間的通訊量,就是系統設計要考慮的重點了。在本文中,我們將遞進介紹三種主流數據并行的實現方式:

2023-06-16 09:54:36 4464

4464

數據并行是最常見的并行形式,因為它很簡單。在數據并行訓練中,數據集被分割成幾個碎片,每個碎片被分配到一個設備上。這相當于沿批次(Batch)維度對訓練過程進行并行化。每個設備將持有一個完整的模型副本,并在分配的數據集碎片上進行訓練。

2023-08-24 15:17:28 2496

2496

電子發燒友網站提供《無與倫比的并行處理—FPGA加速的根本基石.pdf》資料免費下載

2023-09-15 14:57:19 3

3 電子發燒友網站提供《基于FPGA的ARM并行總線設計原理.pdf》資料免費下載

2023-10-10 09:31:31 1

1 NVIDIA Megatron 是一個基于 PyTorch 的分布式訓練框架,用來訓練超大Transformer語言模型,其通過綜合應用了數據并行,Tensor并行和Pipeline并行來復現 GPT3,值得我們深入分析其背后機理。

2023-10-23 11:01:33 5453

5453

首先是FPGA硬件的變化太多,各個模塊可配參數的變化(比如卷積模塊并行數的變化),另外一個是網絡模型多種多樣以及開源的網絡模型平臺也很多(tensorflow,pytorch等)。網絡壓縮也有很多種算法,這些算法基本上都會導致網絡模型精度的降低。

2024-04-08 09:48:11 2150

2150

電子發燒友網站提供《TDAxx上的ECC/EDC.pdf》資料免費下載

2024-10-11 10:19:20 0

0 FPGA(現場可編程門陣列)加速深度學習模型是當前硬件加速領域的一個熱門研究方向。以下是一些FPGA加速深度學習模型的案例: 一、基于FPGA的AlexNet卷積運算加速 項目名稱

2024-10-25 09:22:03 1856

1856 現場可編程門陣列(FPGA)是一種高度靈活的硬件平臺,它允許開發者根據特定應用需求定制硬件邏輯。在實時信號處理和圖像處理領域,FPGA因其獨特的優勢而受到青睞。 1. 并行處理能力 FPGA的最大

2024-12-02 10:01:34 2508

2508 ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2025-03-14 13:54:12 1979

1979

在 AI 賦能工程設計的時代浪潮中,智多晶率先邁出關鍵一步——智多晶正式宣布旗下 FPGA 設計工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 設計專屬 AI 助手——晶小助!這是 FPGA 領域首次引入大模型 AI 助手,為 FPGA 工程師提供前所未有的智能交互體驗。

2025-06-06 17:06:39 1284

1284 失敗或數據靜默損壞等問題。通過Micron芯片案例,說明了BCH等算法在糾正多位錯誤上的優勢,并給出工程實踐建議:需嚴格匹配芯片規格與控制器配置,在量產前進行ECC壓力測試。文章強調,正確配置ECC可顯著提升系統可靠性,避免將軟錯誤誤判為硬件故障,是存儲系統設計中不可忽視的關鍵環節。

2025-11-25 16:12:37 390

390

電子發燒友App

電子發燒友App

評論