用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。

本項目所需應用與工具:賽靈思HLS、Plunify Cloud 以及 InTime。

前言

高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著從 C 轉化得到 RTL 基本不可能。其實,使用 FPGA 工具設置來優化設計可以最小限度地減少對性能的犧牲,這種方法是存在的。

高效地找到合適的FPGA工具設置

盡管工程師們知道 FPGA 工具的設置,但是這些設置往往并沒有充分利用。一般而言,工具設置只有在出現時序問題的時候才會派上用途。然而,對于已經達到性能目標的設計來說,如果繼續調整工具設計,仍然有10%-50%的性能提升潛力。

真正的難點在于選擇正確的工具設置,畢竟各種 FPGA 工具一般都有有30-70個不同的布局布線設置,可選的設置組合實在是太多了。您可以寫腳本來運行不同的推薦指令/策略。市面上也有工具,來自動管理并運行設計探索。

另一個難點就是不充裕的計算能力。典型的嵌入式應用是在單臺電腦上設計的。運行多個編譯需要更多的計算能力,這就要求更多的時間。如果您可以(使用云計算)并行運行,周轉時間就會變短。

如何優化高層次的設計 - “Sobel濾鏡”項目

這是一個用于視屏處理的參考設計,來自賽靈思的官網 https://china.xilinx.com/support/documentation/application_notes/xapp890... 。該設計的功能是 Sobel 濾鏡,目標器件是擁有雙核Dual ARM? Cortex?-A9MPCore 的 FPGA。

我們使用賽靈思 HLS 來打開這個設計。

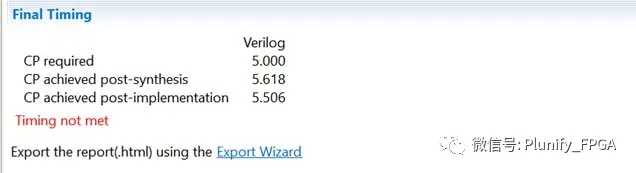

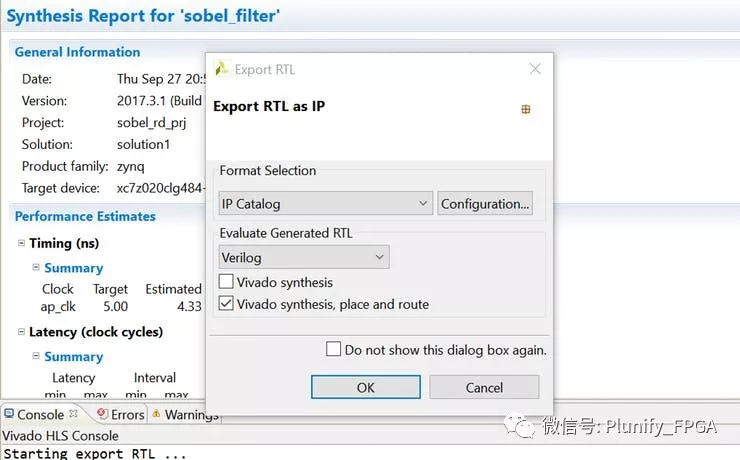

圖三:從HLS輸出Vivado項目

它會在后臺執行 Vivado,并生成一個項目文件(XPR)。它同時也會編譯設計,您應該在控制臺(Console)看到真實的時序細節。一旦完成,您可以在 /solution/impl/verilog/ 文件夾下找到項目文件。

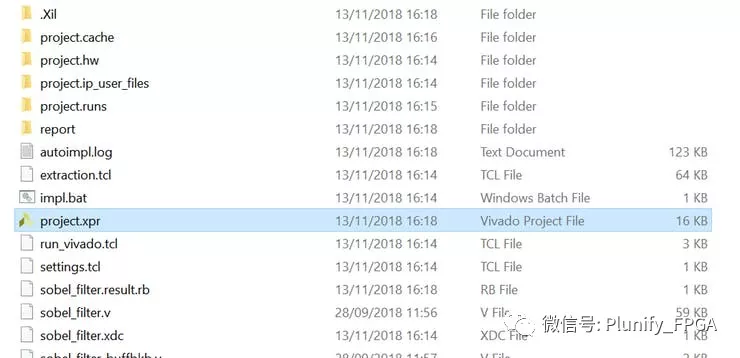

圖四:Vivado 項目文件

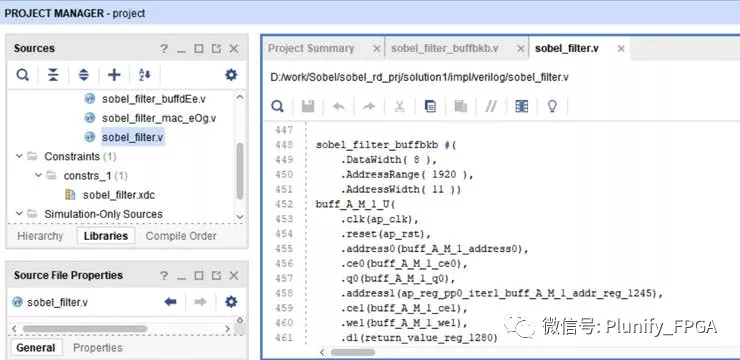

找到這個 XPR 文件之后,您可以用 Vivado 打開它來驗證。您將看到生成好的 RTL 源文件。

圖五:從 HLS 生成的 RTL

時序優化

下一步,是使用 InTime 設計探索工具,當然,您也可以自己寫腳本來嘗試 Vivado 工具中自帶的指令和策略。請申請 InTime 的免費試用在本地運行,也可以注冊一個 Plunify Cloud 云平臺的賬戶,試用所提供的免費云幣來在云端運行預置好的 FPGA 工具。

啟動 InTime 之后,打開項目文件。在選擇 Vivado 版本時,請使用“相同的”版本。例如,如果您使用2017.3 HLS,請選擇2017.3 Vivado。

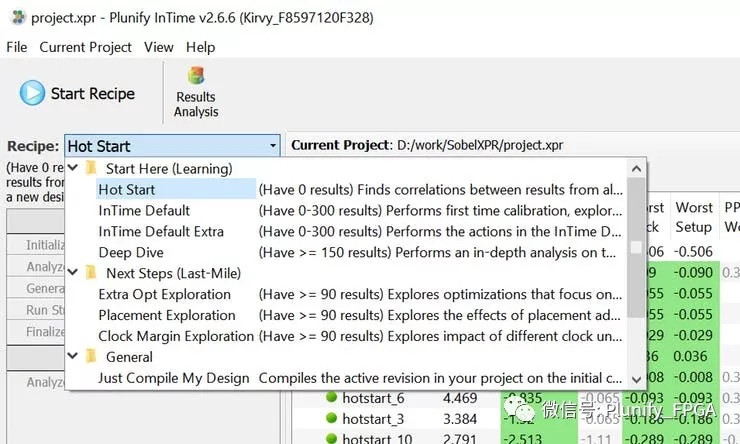

選擇“Hot Start”配方(recipe)。此配方包含一系列更具以往其他設計的經驗而推薦的策略。

圖六:選擇 "Hot Start" 配方

點擊“Start Recipe”來開始優化。如果您在云端運行,您應該并行運行多個編譯來減少周轉時間。

優化過程和結果

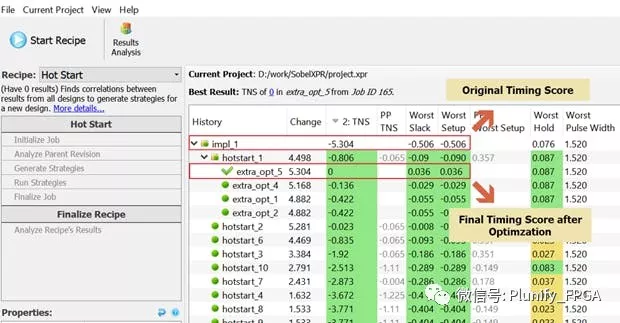

第一輪結束之后 (“Hot Start”配方),最好的結果是“hotstart_1”策略。然而,它仍然距離目標時序90ns。

我們在“HotStart_1”的結果上使用了第二個配方,叫做“Extra Opt Exploration”。這一輪將集中優化關鍵的路徑。這是一次迭代優化,并且只要仍有提升,就不斷地重復自己。如果達到時序目標或者不再提升的時候,它就會停止。

圖七:僅通過工具設置完成時序收斂

經過兩輪優化,總共15此編譯后,設計達到了目標時序,200MHz。而這一切完全沒有修改 RTL 源代碼。

讓性能更進一步

讓性能更進一步需要各方面的優化 – 結構設計、代碼和工具。工具設置的探索可以克服高層次設計的性能犧牲,并且不會讓生產效率的好處減少。對于高層次設計的工程師來說,這是一種共贏。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636265

發布評論請先 登錄

HLS設計中的BRAM使用優勢

如何在vivadoHLS中使用.TLite模型

當不同的數據放在同一個Flash頁面上時,請問如何在不影響其他數據的情況下更改一些單獨的數據?

如何在Unified IDE中創建視覺庫HLS組件

如何使用AMD Vitis HLS創建HLS IP

FX2LP如何在不更改硬件的情況下對其進行重新編程?

Vivado HLS設計流程

如何在不改變RTL代碼的情況下,優化FPGA HLS設計

如何在不改變RTL代碼的情況下,優化FPGA HLS設計

評論