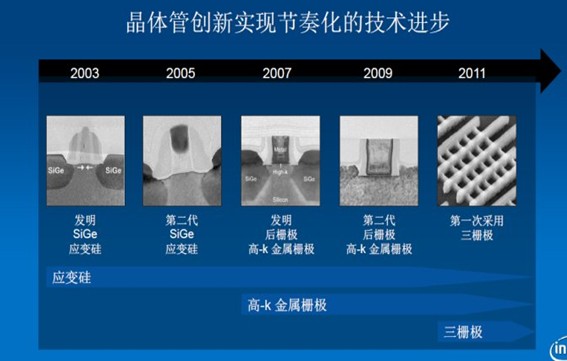

在22nm,或許是16nm節(jié)點,我們將需要全新的晶體管。而在這其中,爭論的焦點在于究竟該采用哪一種技術(shù)。這場比賽將關(guān)乎到晶體管的重新定義。在22/20nm邏輯制程的開發(fā)中,業(yè)界都爭先

2012-03-06 10:08:16 2292

2292 據(jù)香港《南華早報》網(wǎng)站5月27日報道,現(xiàn)如今,市場上最先進的計算機芯片使用7納米晶體管。中國科學(xué)院微電子研究所微電子設(shè)備與集成技術(shù)領(lǐng)域的專家殷華湘說,他的團隊已經(jīng)研發(fā)出3納米晶體管——相當于一條人類DNA鏈的寬度,在一個指甲蓋大小的芯片上能安裝數(shù)百億個這種晶體管。

2019-05-28 11:33:06 2837

2837 在9月的臺灣SEMICON國際半導(dǎo)體展上,臺積電(TSMC)首席執(zhí)行官Mark Lui認為摩爾定律仍然有效。他表示,由于先進工藝技術(shù)(如納米片)或3D FinFETS中的全柵晶體管技術(shù)的發(fā)展

2019-10-15 15:11:02 6162

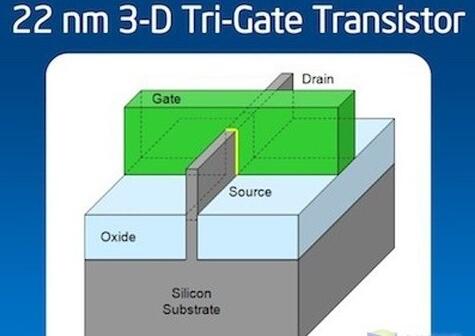

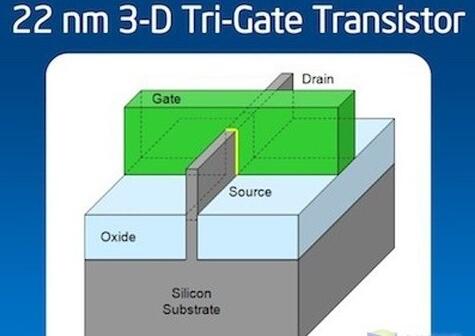

6162 什么是3D晶體管?3D晶體管,從技術(shù)上講,應(yīng)該是三個門晶體管。傳統(tǒng)的二維門由較薄的三維硅鰭(fin)所取代,硅鰭由硅基垂直伸出。

2012-08-08 11:12:01 3657

3657 Achronix Semiconductor公司今日宣布:公司已開始將其業(yè)界領(lǐng)先的Speedster?22i HD1000可編程邏輯器件(FPGA)發(fā)運給客戶。該器件采用英特爾領(lǐng)先的22納米3D

2013-02-21 15:00:59 1594

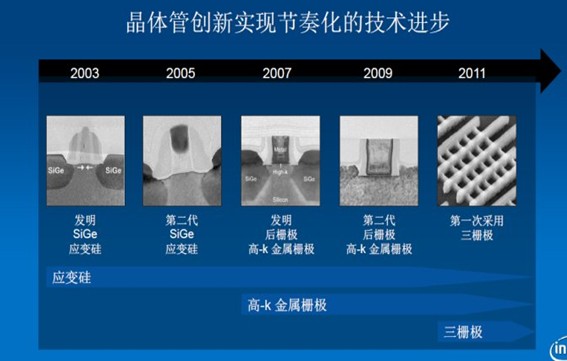

1594 目前3D晶體管成為代工產(chǎn)業(yè)重點關(guān)注的技術(shù),但很多人關(guān)于這個技術(shù)的細節(jié)不是很了解,我們在這里介紹一下。

2015-12-28 14:34:12 12814

12814

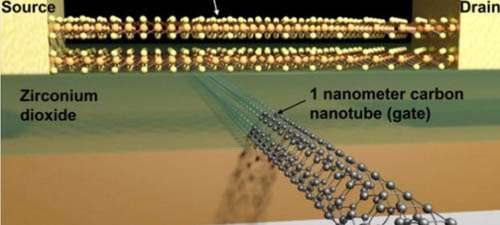

臺積電共同執(zhí)行長劉德音先前在出席活動時才透露,目前已組成團隊著手3 納米研發(fā),業(yè)界一片驚奇,而且現(xiàn)在不只3 納米,1 納米也來了!隸屬美國能源部的勞倫斯伯克利國家實驗室Ali Javey 團隊即宣稱,突破了物理極限,成功創(chuàng)造1 納米晶體管。

2016-10-08 14:51:21 2833

2833

近日公布2011年“科技創(chuàng)新獎”,英特爾的3-D三柵極晶體管設(shè)計獲得半導(dǎo)體類別創(chuàng)新大獎。英特爾的3-D三柵極晶體管結(jié)構(gòu)代表著從2-D平面晶體管結(jié)構(gòu)的根本性轉(zhuǎn)變

2011-10-23 01:01:04 1184

1184 2012年4月23日,英特爾宣布采用3D三柵極晶體管設(shè)計,最小線寬為22納米的Ivy Bridge微處理器量產(chǎn)成功,并于4月29日開始全球銷售。

2012-05-13 09:35:43 4929

4929 其實早在2002年Intel即發(fā)現(xiàn)了這一技術(shù),一直處于試驗演示階段,現(xiàn)在終于把它變成了現(xiàn)實,Intel打算把它融入到22nm的“Ivy Bridge”芯片,Ivy Bridge晶體管的數(shù)量將達到10億。

2020-04-07 09:01:21

3D顯示技術(shù)的原理是什么?3D顯示技術(shù)有哪些應(yīng)用?3D拍好了到底怎么樣傳輸?

2021-05-31 06:53:03

晶體管技術(shù)方案面臨了哪些瓶頸?

2021-05-26 06:57:13

晶體管分類 按半導(dǎo)體材料和極性分類 按晶體管使用的半導(dǎo)體材料可分為硅材料晶體管和鍺材料晶體管。按晶體管的極性可分為鍺NPN型晶體管、鍺PNP晶體管、硅NPN型晶體管和硅PNP型晶體管。 按結(jié)構(gòu)

2010-08-12 13:59:33

晶體管參數(shù)測量技術(shù)報告摘 要晶體管的參數(shù)是用來表征管子性能優(yōu)劣和適應(yīng)范圍的指標,是選管的依據(jù)。為了使管子安全可靠的工作,必須注意它的參數(shù)。本文主要論述以AduC812為核心的晶體管參數(shù)測試系統(tǒng),該系

2012-08-02 23:57:09

的hFE檔測量。測量時,應(yīng)先將萬用表置于ADJ檔進行調(diào)零后,再撥至hFE檔,將被測晶體管的C、B、E三個引腳分別插入相應(yīng)的測試插孔中(采用TO-3封裝的大功率晶體管,可將其3個電極接出3根引線后,再分

2012-04-26 17:06:32

晶體管測量模塊的基本特性有哪些?晶體管測量模塊的基本功能有哪些?

2021-09-24 07:37:23

從事電子設(shè)計7年了,發(fā)覺這兩本書挺好的,發(fā)上來給大家分享一下附件晶體管電路設(shè)計(上)放大電路技術(shù)的實驗解析.pdf42.5 MB晶體管電路設(shè)計(下)FET_功率MOS_開關(guān)電路的實驗解析.rar.zip47.2 MB

2018-12-13 09:04:31

晶體管的主要參數(shù)有哪些?晶體管的開關(guān)電路是怎樣的?

2021-06-07 06:25:09

晶體管概述的1. 1948年、在貝爾電話研究所誕生。1948年,晶體管的發(fā)明給當時的電子工業(yè)界來帶來了前所未有的沖擊。而且,正是這個時候成為了今日電子時代的開端。之后以計算機為首,電子技術(shù)取得急速

2019-07-23 00:07:18

有效芯片面積的增加,(2)技術(shù)上的簡化,(3)晶體管的復(fù)合——達林頓,(4)用于大功率開關(guān)的基極驅(qū)動技術(shù)的進步。、直接工作在整流380V市電上的晶體管功率開關(guān)晶體管復(fù)合(達林頓)和并聯(lián)都是有效地增加

2018-10-25 16:01:51

晶體管概述的1. 1948年、在貝爾電話研究所誕生。1948年,晶體管的發(fā)明給當時的電子工業(yè)界來帶來了前所未有的沖擊。而且,正是這個時候成為了今日電子時代的開端。之后以計算機為首,電子技術(shù)取得急速

2019-05-05 00:52:40

)用業(yè)收集電子。晶體管的發(fā)射極電流IE與基極電流IB、集電極電流IC之間的關(guān)系如下:IE=IB+IC3.晶體管的工作條件晶體管屬于電流控制型半導(dǎo)體器件,其放大特性主要是指電流放大能力。所謂放大,是指當

2013-08-17 14:24:32

圖像中放、伴音中放、緩沖放大等)電路中使用的高頻晶體管,可以選用特征頻率范圍在30~300MHZ的高頻晶體管,例如3DG6、3DG8、3CG21、2SA1015、2SA673、2SA733、S9011

2012-01-28 11:27:38

【不懂就問】圖中的晶體管驅(qū)動電路,在變壓器Tr的副邊輸出電阻R3上并聯(lián)的二極管D2,說D2的作用是在輸入端有正脈沖輸入時使得變壓器次級產(chǎn)生的的正脈沖通過D2,直接驅(qū)動MOSFET管Q2,達到提高導(dǎo)

2018-07-09 10:27:34

是碳化硅(SiC)襯底上的氮化鎵(GaN)高電子遷移率晶體管(HEMT)。這種GaN內(nèi)匹配(IM)場效應(yīng)晶體管與其他技術(shù)相比,提供了優(yōu)異的功率附加效率。GaN與硅或砷化鎵相比具有更高的性能,包括更高

2018-08-13 10:58:03

Finfet技術(shù)(3D晶體管)詳解

2012-08-19 10:46:17

JY-3晶體管測試儀技術(shù)說明書

2012-08-03 00:00:14

。圖片:D. Hisamoto等人,1990年 英特爾在 2012 年宣布使用批量配置(22 納米技術(shù))(圖 11)。 圖 11.英特爾的鰭式場效應(yīng)晶體管。圖片:英特爾公司 一些基本功能

2023-02-24 15:20:59

multisim仿真中高頻晶體管BFG35能用哪個晶體管來代替,MFR151管子能用哪個來代替?或是誰有這兩個高頻管子的原件庫?求大神指教

2016-10-26 11:51:18

本帖最后由 王棟春 于 2021-1-5 22:40 編輯

《晶體管電路設(shè)計與制作》是“圖解實用電子技術(shù)叢書”之一。本書首先對各種模擬電路的設(shè)計和制作進行詳細敘述;然后利用可在微機

2021-01-05 22:38:36

與銷售集團總裁Stacy Smith英特爾公司執(zhí)行副總裁兼制造、運營與銷售集團總裁Stacy Smith全球首次展示“Cannon Lake”10納米晶圓,采用超微縮技術(shù),擁有世界上最密集的晶體管和最小

2017-09-22 11:08:53

片晶體管通常基于納米片堆疊技術(shù),納米片作為晶體管的溝道部分,其厚度和寬度可以精確控制,以實現(xiàn)更好的靜電控制和更高的驅(qū)動電流。叉片晶體管可以實現(xiàn)垂直堆疊,即多個晶體管層疊在一起。這種堆疊方式進一步提高了

2025-06-20 10:40:07

世界首款3D芯片工藝即將由無晶圓半導(dǎo)體公司BeSang授權(quán)。 BeSang制造了一個示范芯片,在邏輯控制方面包含1.28億個縱向晶體管的記憶存儲單元。該芯片由韓國國家Nanofab和斯坦福

2008-08-18 16:37:37

互補晶體管的匹配

2019-10-30 09:02:03

當3D電影已成為影院觀影的首選,當3D打印已普及到雙耳無線藍牙耳機,一種叫“3D微波”的技術(shù)也悄然而生。初次聽到“3D微波”,你可能會一臉茫然,這個3D微波是應(yīng)用在哪個場景?是不是用這種技術(shù)的微波爐1秒鐘就能把飯煮熟?O M G!我覺得很有必要給大家科普一下!

2019-07-02 06:30:41

調(diào)制和振蕩器。晶體管可以獨立封裝,也可以封裝在非常小的區(qū)域內(nèi),容納1億個或更多晶體管集成電路的一部分。(英特爾 3D 晶體管技術(shù))嚴格來說,晶體管是指基于半導(dǎo)體材料的所有單一元件,包括由各種半導(dǎo)體材料

2023-02-03 09:36:05

顯示器和透明太陽能電池板產(chǎn)品的出現(xiàn)。 在許多透明電子系統(tǒng)中,晶體管都是至關(guān)重要的部件。如今,這種器件通常是薄膜晶體管形式,由In2O3、ZnO2、SnO2等透明導(dǎo)電氧化物材料制成。 不過,薄膜晶體管

2020-11-27 16:30:52

達林頓晶體管是一對雙極晶體管,連接在一起,從低基極電流提供非常高的電流增益。輸入晶體管的發(fā)射極始終連接到輸出晶體管的基極;他們的收藏家被綁在一起。結(jié)果,輸入晶體管放大的電流被輸出晶體管進一步放大

2023-02-16 18:19:11

電場控制材料的電導(dǎo)率。 鰭式場效應(yīng)晶體管是一種非平面器件,即不受單個平面的限制。它也被稱為3D,因為具有第三維度。 為避免混淆,必須了解不同的文獻在提及鰭式場效應(yīng)晶體管器件時使用不同的標簽

2023-02-24 15:25:29

各位高手,小弟正在學(xué)習(xí)單結(jié)晶體管,按照網(wǎng)上的電路圖做的關(guān)于單結(jié)晶體管的仿真,大多數(shù)都不成功,請問誰有成功的單結(jié)晶體管的仿真仿真啊,可以分享下嗎。

2016-03-04 09:15:06

,導(dǎo)致流過晶體管的電流為零的大耗盡層。在這種情況下,晶體管被關(guān)閉。 截斷區(qū)域特征如下所示: 圖3.截斷區(qū)域特征。圖片由Simon Munyua Mugo提供 晶體管操作類似于單刀單擲固態(tài)開關(guān)

2023-02-20 16:35:09

什么是微波功率晶體管?如何提高微波功率晶體管可靠性?

2021-04-06 09:46:57

來至網(wǎng)友的提問:如何選擇分立晶體管?

2023-11-24 08:16:54

晶體管依照用途大致分為高頻與低頻,它們在型號上的大致區(qū)別是什么?例如《晶體管電路設(shè)計》中列舉的:高頻(2SA****,2SC*****)、低頻(2SB****,2SD****)。現(xiàn)在產(chǎn)品設(shè)計中最常用的型號是哪些?

2017-10-11 23:53:40

晶體管為保持ON狀態(tài)的最低電壓、定義VI(on)為min錯誤觀點1:由0開始依次加入輸入電壓。2:達到1.8V時,數(shù)字晶體管啟動。3:因在規(guī)格書規(guī)定的3V(min) 以下,故判斷為不合格。正確觀點A

2019-04-22 05:39:52

混淆VI(on): 數(shù)字晶體管為保持ON狀態(tài)的最低電壓、定義VI(on)為min錯誤觀點1:由0開始依次加入輸入電壓。2:達到1.8V時,數(shù)字晶體管啟動。3:因在規(guī)格書規(guī)定的3V(min) 以下,故

2019-04-09 21:49:36

急需一種流動性更強的新材料來替代硅。三五族材料砷化銦鎵就是候選半導(dǎo)體之一,普渡大學(xué)通過這種材料做出了全球首款3D環(huán)繞閘極(gate-all-around)晶體管。此外,三五族合金納米管將把閘極長度

2011-12-08 00:01:44

(電阻器)組成。構(gòu)成晶體管的硅是形成地球的巖石中大量含有的物質(zhì)。因此,晶體管也俗稱"石",設(shè)計者常用"…之石"的叫法3. 按集成度分類為滿足客戶需求,ROHM在分立式

2019-05-05 01:31:57

效率和功率密度。GaN功率晶體管作為一種成熟的晶體管技術(shù)在市場上確立了自己的地位,但在軟開關(guān)應(yīng)用中通常不被考慮使用。雖然在硬開關(guān)應(yīng)用中使用GaN可以顯著提高效率,但軟開關(guān)轉(zhuǎn)換器(如LLC)對效率和頻率

2023-02-27 09:37:29

3D視覺技術(shù)有何作用?常見的3D視覺方案主要有哪些?

2021-11-09 07:46:56

正在從二維走向三維世界——芯片設(shè)計、芯片封裝等環(huán)節(jié)都在向3D結(jié)構(gòu)靠攏。晶體管架構(gòu)發(fā)生了改變當先進工藝從28nm向22nm發(fā)展的過程中,晶體管的結(jié)構(gòu)發(fā)生了變化——傳統(tǒng)的平面型晶體管技術(shù)(包括體硅技術(shù)

2020-03-19 14:04:57

的GAA晶體管結(jié)構(gòu),三星通過使用納米片設(shè)備制造出MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應(yīng)管),該技術(shù)可以顯著增強晶體管性能,取代FinFET晶體管技術(shù)。 此外,MBCFET技術(shù)還能兼容現(xiàn)有的FinFET制造工藝的技術(shù)及設(shè)備,從而加速工藝開發(fā)及生產(chǎn)。

2020-07-07 11:36:10

這個達林頓晶體管廠家是哪家

2022-05-30 16:36:56

本帖最后由 eehome 于 2013-1-5 10:10 編輯

高清圖詳解英特爾最新22nm 3D晶體管

2012-08-05 21:48:28

高清圖詳解英特爾最新22nm_3D晶體管

2012-08-02 23:58:43

晶體管實驗:實驗一 三極晶體管與場效應(yīng)晶體管的特性圖示一、實驗?zāi)康?.掌握半導(dǎo)體管特性圖示儀的使用方法。2.掌握測量晶體管輸入輸出特性的測量方法。3.觀察、了

2009-03-06 14:08:16 37

37 英飛凌科技公司(Infineon),設(shè)在慕尼黑的實驗室最近取得了新的突破——這里的研究人員成功開發(fā)出全球最小的納米晶體管,其溝槽長度僅為18納米,幾乎是當前最先進的晶

2006-03-11 22:10:39 1263

1263 晶體管(transistor)

4

5納米工藝的四核處理器已能容納8億個晶體管

2009-11-05 10:34:25 1669

1669 晶體管出現(xiàn)的意義

晶體管的出現(xiàn),是電子技術(shù)之樹上綻開的一朵絢麗多彩的奇葩。 同電子管相比,晶體管具有諸多優(yōu)越性: ①晶體管的構(gòu)

2009-11-05 10:46:47 3960

3960 CMOS晶體管,CMOS晶體管是什么意思

金屬-氧化物-半導(dǎo)體(Metal-Oxide-Semiconductor)結(jié)構(gòu)的晶體管簡稱MOS晶體管,有P型MOS管和N型MOS管之分

2010-03-05 15:22:51 4129

4129 在本周于舊金山召開的英特爾開發(fā)者大會(IDF)中,英特爾將再揭示其采用三柵極(tri-gate)3D晶體管技術(shù)的22nm元件細節(jié),并進一步說明超輕薄筆電(Ultrabook)的超薄、超低功耗設(shè)計概念。

2011-09-16 09:23:43 1145

1145 晶體管是現(xiàn)代電子學(xué)的基石,而Intel 此舉堪稱晶體管歷史上最偉大的里程碑式發(fā)明,甚至可以說是重新發(fā)明了晶體管。半個多世紀以來,晶體管一直都在使用2-D 平面結(jié)構(gòu),現(xiàn)在終于邁入

2012-01-18 15:28:52 147

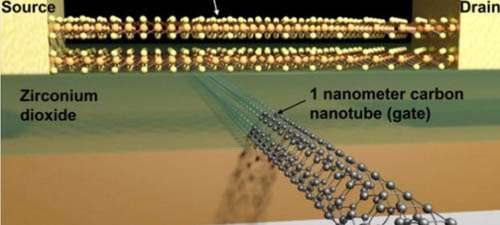

147 來自IBM、蘇黎世理工學(xué)院和美國普渡大學(xué)的工程師近日表示,他們構(gòu)建出了首個10納米以下的碳納米管(CNT)晶體管

2012-02-04 09:45:29 1105

1105 Achronix 半導(dǎo)體公司今日宣布了其 Speedster22i HD和HP產(chǎn)品系列的細節(jié),它們是將采用英特爾22nm 3D晶體管技術(shù)工藝制造的首批現(xiàn)場可編程門陣列(FPGA)產(chǎn)品。Speedster22i FPGA產(chǎn)品是業(yè)內(nèi)唯一

2012-04-25 09:12:05 1560

1560 為了在硅芯片上擠入更多的元件,英特爾已開始大規(guī)模生產(chǎn)基于3-D晶體管的處理器。這一舉動不僅延長了摩爾定律(根據(jù)該定律,每塊芯片上的晶體管數(shù)量每兩年就會翻一番)的壽命

2012-07-09 11:11:34 1346

1346

《晶體管精華集錦》技術(shù)專題主要介紹了晶體管新品資訊、晶體管原理、晶體管手冊、晶體管電路圖、晶體管電路設(shè)計、晶體管應(yīng)用(主要含晶體管收音機、晶體管測試儀)以及常見的晶體管(如:場效應(yīng)晶體管,mos晶體管,絕緣柵雙極晶體管等)。本專題內(nèi)容豐富、包羅萬象,希望對各位有所幫助!

2012-08-03 09:12:48

本文通過高清圖詳解Intel最新22nm 3D 晶體管 。業(yè)界一直傳說3D三柵級晶體管技術(shù)將會用于下下代14nm的半導(dǎo)體制造,沒想到英特爾竟提前將之用于22nm工藝,并且于上周四向全世界表示將在

2012-08-03 17:09:18 0

0 Intel2011年5月6日研制成功的世界上第一個3D晶體管“Tri-Gate”現(xiàn)在已經(jīng)逐步進入大家的視線了,本文將介紹3D晶體管的一些優(yōu)點。

2012-08-08 11:49:46 2303

2303 本文核心議題: 通過本文介紹,我們將對Intel 22nm 3D三柵極晶體管技術(shù)有著詳細的了解。業(yè)界一直傳說3D三柵級晶體管技術(shù)將會用于下下代14nm的半導(dǎo)體制造,沒想到英特爾竟提前將之用

2012-08-15 10:45:27 8565

8565

英特爾已經(jīng)準備把第一個3D晶體管結(jié)構(gòu)導(dǎo)入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 1252

1252

英特爾已經(jīng)準備把第一個3D晶體管結(jié)構(gòu)導(dǎo)入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 1528

1528 英特爾已經(jīng)準備把第一個3D晶體管結(jié)構(gòu)導(dǎo)入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 5599

5599 近日消息,英特爾計劃將“3D晶體管”工藝應(yīng)用到SoC移動芯片上,以獲得產(chǎn)品性能飛躍性提升,但對于“3D晶體管”技術(shù)是否適用于SoC芯片的制造,參與舊金山國際電子產(chǎn)品大會的專家們

2012-12-11 09:05:45 1434

1434 FinFET的芯片。在2月份舉行的這次Common Platform 2013技術(shù)論壇上,IBM除了展示FinFET這種3D晶體管技術(shù)外,還展示了諸如硅光子晶體管,碳納米管等前沿技術(shù)。

2013-02-20 23:04:30 8361

8361 米特拉表示,“如果利用碳納米管晶體管取代硅晶體管,效能比可提高1000倍。”

2016-08-22 14:03:54 1290

1290 新的微加工技術(shù)可用于生產(chǎn)有史以來最小的3D晶體管,尺寸是目前主流商用產(chǎn)品的三分之一。

2018-12-12 09:40:48 3709

3709 現(xiàn)如今,市場上最先進的計算機芯片使用7納米晶體管。中國科學(xué)院微電子研究所微電子設(shè)備與集成技術(shù)領(lǐng)域的專家殷華湘說,他的團隊已經(jīng)研發(fā)出3納米晶體管——相當于一條人類DNA鏈的寬度,在一個指甲蓋大小的芯片上能安裝數(shù)百億個這種晶體管。

2019-06-13 16:08:27 5958

5958 他于近日在底特律對數(shù)百名工程師表示:“這片晶片是上周五制造的……這是鑄造廠制造的第一塊單片3D集成電路。”晶圓上有多個芯片,由一層CMOS碳納米管晶體管和一層RRAM存儲單元構(gòu)成,這些存儲單元相互疊放

2019-10-13 16:50:00 3322

3322 CPU里的晶體管都是集成的超微晶體管,一個22納米工藝的i5可能集成上十億的晶體管。

2020-01-31 16:10:00 15286

15286 但是,這并不代表著對碳納米管半導(dǎo)體技術(shù)的研發(fā)會一帆風順。1998年首個碳納米管晶體管研發(fā)至今,碳納米管半導(dǎo)體技術(shù)一直遭遇材料上的瓶頸。長期以來,最小碳納米管CMOS器件的柵長停滯在20nm(2014年 IBM)。

2020-08-31 15:00:50 4507

4507 全環(huán)繞柵極晶體管的出現(xiàn)滿足了以上所有需求,從而允許摩爾定律在5納米之后進一步前進。首先其生產(chǎn)工藝與鰭式晶體管相似,關(guān)鍵工藝步驟幾乎一樣(這點我們會在之后的文章中進一步講解)。其次,全環(huán)繞柵極晶體管

2020-09-29 13:54:39 4508

4508 隨后,晶體管的小型化之路趨向緩慢。《日經(jīng)》稱,從32納米到近期的10納米,雖然芯片制造商一直在標榜芯片制程的縮小。但從2005年前后,這些數(shù)字不再是柵極的實際尺寸了。如今,所謂的“10納米”或“7納米”,只是芯片制造商的一種品牌標簽。

2020-11-17 16:41:16 3067

3067 來自復(fù)旦大學(xué)微電子學(xué)院的消息,該校周鵬團隊針對具有重大需求的3-5納米節(jié)點晶體管技術(shù),驗證了雙層溝道厚度分別為0.6 /1.2納米的圍柵多橋溝道晶體管(GAA,Gate All Around),實現(xiàn)了高驅(qū)動電流和低泄漏電流的融合統(tǒng)一,為高性能低功耗電子器件的發(fā)展提供了新的技術(shù)途徑

2020-12-24 12:38:46 4445

4445 ? ? FinFET晶體管架構(gòu)是當今半導(dǎo)體行業(yè)的主力軍。但是,隨著器件的持續(xù)微縮,短溝道效應(yīng)迫使業(yè)界引入新的晶體管架構(gòu)。在本文中,IMEC的3D混合微縮項目總監(jiān)Julien Ryckaert勾勒出了

2020-12-30 17:45:16 4074

4074 過時。IBM?在 2021?年就證明了這一點,其突破性的 2?納米芯片技術(shù)顛覆了市場。這個新的制造時代得益于減少芯片納米的競賽。? 今天,晶體管的標準長度是10納米,而且隨著最新研究,頂級公司已經(jīng)生產(chǎn)了5納米或7納米的芯片。從歷史

2022-01-07 10:12:35 743

743 FinFET確切的說,是一個技術(shù)的代稱。世界上第一個3D三維晶體管是由英特爾在2011年5月宣布研制成功,當時英特爾稱其為 “Tri-Gate”(三柵極晶體管)。

2022-07-08 15:04:26 2297

2297 MicroFAB-3D雙光子聚合3D納米光刻機是一款超緊湊、超高分辨率交鑰匙型3D打印機。雙光子聚合3D納米光刻機基于雙光子聚合(TPP)激光直寫技術(shù),兼容多種高分子材料,包括生物材料。MicroFAB-3D 3D納米光刻機幫助您以百納米級的分辨率生產(chǎn)出前所未有的復(fù)雜的微部件.

2022-08-08 13:54:18 8187

8187

碳納米管具有高穩(wěn)定性和卓越的電子特性,已成為替代晶體管中硅的主要候選材料。在11 月 17 日發(fā)表于《科學(xué)》雜志的一篇評論文章中,西北大學(xué)的Mark Hersam及其合作者概述了碳納米管在高性能 IC 以及適用于物聯(lián)網(wǎng)的低成本/低性能電子產(chǎn)品中的機遇和剩余挑戰(zhàn)

2022-11-25 10:03:36 1999

1999 使用 3D 納米打印

2022-12-28 09:51:07 1449

1449 50 V、3 A PNP 低 VCEsat 晶體管-PBSS5350D

2023-02-07 19:25:42 0

0 50 V、3 A PNP 低 VCEsat 晶體管-PBSS5350D-Q

2023-02-09 21:24:56 0

0 在半導(dǎo)體行業(yè)的最初幾十年里,新的工藝節(jié)點只需縮小晶體管的物理尺寸并將更多晶體管塞到芯片上即可實現(xiàn)性能、功耗和面積增益,這稱為經(jīng)典縮放。集成電路工作得更好,因為電信號在每個晶體管之間傳播的距離更短。

2023-07-16 15:47:43 1457

1457 最近有許多正在全球范圍內(nèi)研究和開發(fā)的技術(shù),例如晶體管GAA(Gate All around)、背面供電以及3D IC。

2023-07-26 18:21:58 6699

6699

IBM 的概念納米片晶體管在氮沸點下表現(xiàn)出近乎兩倍的性能提升。這一成就預(yù)計將帶來多項技術(shù)進步,并可能為納米片晶體管取代 FinFET 鋪平道路。更令人興奮的是,它可能會導(dǎo)致更強大的芯片類別的開發(fā)。

2023-12-26 10:12:55 1206

1206 11月7日,有報道稱,美國麻省理工學(xué)院的研究團隊利用超薄半導(dǎo)體材料,成功開發(fā)出一種前所未有的納米級3D晶體管。這款晶體管被譽為迄今為止最小的3D晶體管,其性能與功能不僅與現(xiàn)有的硅基晶體管相當,甚至在某些方面還超越了后者。

2024-11-07 13:43:10 1592

1592 新的晶體管技術(shù)。加州大學(xué)圣巴巴拉分校的研究人員在這一領(lǐng)域邁出了重要一步,他們利用二維(2D)半導(dǎo)體技術(shù),成功研發(fā)出新型三維(3D)晶體管,為半導(dǎo)體技術(shù)的發(fā)展開啟了新的篇

2025-03-20 15:30:45 1074

1074

電子發(fā)燒友App

電子發(fā)燒友App

評論