SkyWater Technology Foundry生產(chǎn)出了首批可以匹敵先進硅芯片性能的3D納米管晶圓片。

這是一些你在政府主辦的技術(shù)會議上不經(jīng)常看到的自發(fā)的掌聲。據(jù)悉,在近日的DARPA電子復興倡議峰會上,當時麻省理工學院的助理教授Max Shulaker拿著一片3D碳納米管IC走上舞臺,在某種程度上,它標志著DARPA將落后的晶圓廠變得可以生產(chǎn)與世界上最先進的晶圓廠競爭的芯片的計劃走出了堅實的一步。

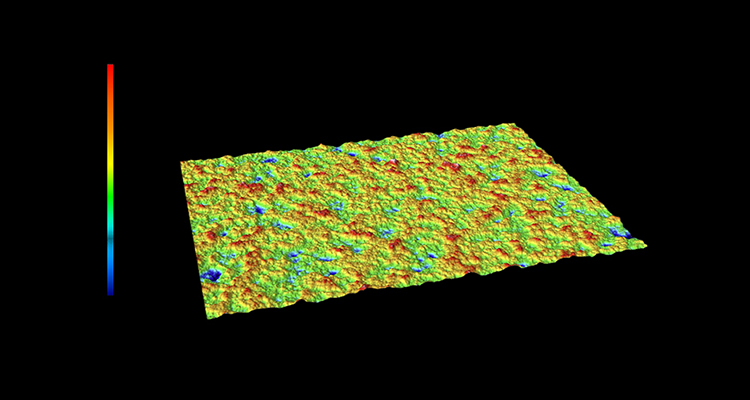

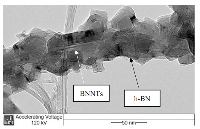

他于近日在底特律對數(shù)百名工程師表示:“這片晶片是上周五制造的……這是鑄造廠制造的第一塊單片3D集成電路。”晶圓上有多個芯片,由一層CMOS碳納米管晶體管和一層RRAM存儲單元構(gòu)成,這些存儲單元相互疊放,并通過稱為VIAS的密集連接器垂直連接在一起。DARPA資助的3DSoC項目背后的想法是,采用兩種技術(shù)的多層芯片將比現(xiàn)在的7納米芯片具有50倍的性能優(yōu)勢。考慮到新芯片所基于的平版印刷工藝(90納米節(jié)點)是2004年最新的尖端技術(shù),這一目標尤其雄心勃勃。

這個項目剛剛運行了一年左右的時間,DARPA希望在持續(xù)運行三年半之后,就可以生產(chǎn)出帶有5000萬邏輯門電路、4G字節(jié)非易失性存儲器、每平方毫米存在900萬個互聯(lián)通道的芯片。互聯(lián)通道之間的傳輸速度為每秒50太比特,每比特的功率消耗小于兩個皮焦耳。

當然,Shulaker目前展示的內(nèi)容還不能做到這一切。但是,這是該計劃進展過程中的一個重要里程碑。與Skywater Technology Foundry和其他合作伙伴一起,“我們徹底改造了我們?nèi)绾沃圃爝@項技術(shù),將其從一項僅在我們的學術(shù)實驗室工作的技術(shù)轉(zhuǎn)變?yōu)橐豁椏梢远椰F(xiàn)在已經(jīng)在商業(yè)制造設(shè)施內(nèi)工作的技術(shù)。”他說:“這是可以在美國的商業(yè)晶圓廠中實施的技術(shù)。”

與當今的2-D硅相比,該技術(shù)的潛在優(yōu)勢的關(guān)鍵在于能夠堆疊多層CMOS邏輯和非易失性存儲器,同時將這些層連接起來,3DSoC團隊稱之為“層”,垂直連接的數(shù)量級更窄、更密集。比其他任何3D技術(shù)都要先進。

這種技術(shù)在硅中是不可能實現(xiàn)的,因為構(gòu)建一層硅邏輯所需的溫度高達1000攝氏度——足以摧毀其下的硅層。3DSoC技術(shù)使用碳納米管晶體管代替,它可以在低于450攝氏度的溫度下制造。同樣,RRAM層也采用低溫工藝制造。因此,可以在不傷害下面層的情況下構(gòu)建多個層。

3DSoC團隊是如何從實驗室好奇心轉(zhuǎn)變?yōu)樯虡I(yè)流程的?“這是一個循序漸進的方法,”Skywater首席技術(shù)官Brad Ferguson告訴IEEE Spectrum。例如,他們分別計算了NMOS碳納米管晶體管和PMOS晶體管的工藝流程,并在制造任何將它們組合成CMOS電路的晶圓之前,分別為每一個晶圓制造出單獨的晶圓。他們也分別制造了RRAM的晶圓,然后計算出與該層的垂直連接。“這種循序漸進的方法確實消除了很多風險……在我們學習的過程中。”

Ferguson說,下一個重要的里程碑是在年底前集成兩層納米管晶體管RRAM。接下來的階段,Skywater和團隊的其他成員將致力于提高產(chǎn)量。他說:“我們正在(為RRAM)實現(xiàn)經(jīng)濟上可行的鉆頭產(chǎn)量。”

在最后一個階段,合作伙伴和潛在客戶將使用流程設(shè)計工具包(第一個版本現(xiàn)已完成)來制造原型芯片。從那里,Skywater將能夠圍繞這一過程建立業(yè)務,并將該技術(shù)授權(quán)給其他鑄造廠。

同樣令人興奮的是,業(yè)績的增長可能會繼續(xù)改善。該工藝可以升級到65納米或更先進的制造節(jié)點,從而獲得更高的密度和更快、更強大的系統(tǒng)。Shulaker說:“一旦3D SoC在寬松成熟的90納米節(jié)點上實現(xiàn),我們就可以依靠傳統(tǒng)技術(shù)進行數(shù)十年的創(chuàng)新。

-

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466053 -

存儲器

+關(guān)注

關(guān)注

39文章

7739瀏覽量

171674 -

納米管

+關(guān)注

關(guān)注

0文章

33瀏覽量

12194

原文標題:首批3D納米管和RRAM集成電路問世

文章出處:【微信號:IEEE_China,微信公眾號:IEEE電氣電子工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

晶圓表面的納米級缺陷光學3D輪廓測量-3D白光干涉儀

納米壓印的光柵圖形形貌3D測量-3D白光干涉儀應用

SOI晶圓片的結(jié)構(gòu)特性及表征技術(shù)

白光干涉儀在晶圓深腐蝕溝槽的 3D 輪廓測量

白光干涉儀在肖特基二極管晶圓的深溝槽 3D 輪廓測量

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

再生晶圓和普通晶圓的區(qū)別

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產(chǎn)業(yè)的前沿技術(shù)

下一代高速芯片晶體管解制造問題解決了!

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測量的設(shè)備

用于切割晶圓 TTV 控制的硅棒安裝機構(gòu)

瑞樂半導體——AVS 無線校準測量晶圓系統(tǒng)讓每一片晶圓都安全抵達終點

從焊錫膏到3D堆疊:材料創(chuàng)新如何重塑芯片性能規(guī)則?

氮化硼納米管在芯片熱界面領(lǐng)域?qū)?b class='flag-5'>性能可提升10-20%,成本僅增加1-2%

首批可以匹敵先進硅芯片性能的3D納米管晶圓片生產(chǎn)出了

首批可以匹敵先進硅芯片性能的3D納米管晶圓片生產(chǎn)出了

評論