從臺積電到阿斯麥爾(ASML),一段時間以來美國頻頻借助各種手段,將商業(yè)問題政治化,打壓中國的半導(dǎo)體行業(yè)。但《日本經(jīng)濟(jì)新聞》在10月21日的一篇評論里指出,隨著半導(dǎo)體技術(shù)的革新,以及中國科技的發(fā)展,未來半導(dǎo)體技術(shù)的大趨勢,其實有利于中國。

《日經(jīng)》:半導(dǎo)體科技發(fā)展趨勢,有利于中國 原日本半導(dǎo)體巨頭爾必達(dá)社長,現(xiàn)中國芯片制造商紫光集團(tuán)的高級副總裁坂本幸雄,在文中對中國半導(dǎo)體行業(yè)的前景尤為樂觀:“當(dāng)今世界,后來者擁有更好的機(jī)會,趕上現(xiàn)在的領(lǐng)導(dǎo)者。” 他還在文中援引一名中國商界人士的話說:“中國科技行業(yè)的領(lǐng)袖們現(xiàn)在感謝特朗普,因為他幫助他們下定決心,自主開發(fā)技術(shù)。” 文章指出,歷史上技術(shù)范式的改變,常常能為行業(yè)的新參與者創(chuàng)造機(jī)會。如今,坂本幸雄也從當(dāng)今半導(dǎo)體行業(yè)的技術(shù)趨勢中,看出了這種趨勢。

晶體管小型化遇瓶頸,3D技術(shù)崛起長期以來,半導(dǎo)體行業(yè)都受制于“摩爾定律”,即集成電路芯片上可以容納的晶體管數(shù)目,大約每24個月便會增加一倍。但實際上,大約2005年前后,芯片表面晶體管和電路尺寸的縮小化之路遇到了瓶頸。當(dāng)時,晶體管的尺寸已縮小至30納米左右,而這一尺寸,是由一種叫做“柵極”(gate)的中央電極來衡量的。 隨后,晶體管的小型化之路趨向緩慢。《日經(jīng)》稱,從32納米到近期的10納米,雖然芯片制造商一直在標(biāo)榜芯片制程的縮小。但從2005年前后,這些數(shù)字不再是柵極的實際尺寸了。如今,所謂的“10納米”或“7納米”,只是芯片制造商的一種品牌標(biāo)簽。 例如,東京大學(xué)的平本俊郎教授就向《日經(jīng)》表示,去年臺積電制造的7納米芯片,實際的柵極尺寸為18納米左右。而這,已經(jīng)與過去柵極尺寸也為32納米的32納米芯片,有了明顯的偏差。

臺積電生產(chǎn)的芯片 官方圖 由于晶體管小型化的難度,以及成本都在不斷上升,因此各大芯片制造商目前已轉(zhuǎn)向一種三維技術(shù),即利用傳統(tǒng)晶圓表面上方的空間,將更多晶體管裝載到芯片上。如今最先進(jìn)的NAND閃存芯片,即在最底層的晶圓裸片上,堆疊了96至128層的集成電路。 隨著層數(shù)的增加和芯片的增厚,晶體管的小型化過程在閃存領(lǐng)域發(fā)生了逆轉(zhuǎn)。業(yè)內(nèi)專家介紹稱,如今閃存芯片的典型晶體管尺寸大約在22至 32納米范圍內(nèi),比幾年前閃存芯片中使用的14納米晶體管要大。 而這種芯片制造技術(shù)從晶體管小型化到三維技術(shù)的重要轉(zhuǎn)變,可能會影響業(yè)界對芯片制造過程中最困難的部分——光刻技術(shù)的態(tài)度。 光蝕刻法是一種工藝,在硅晶圓的光敏表面上,通過一個稱為光掩膜的玻璃板將光投射到硅晶圓上,在玻璃掩膜上可以畫出電路計劃的圖像。這就像傳統(tǒng)的照片顯影過程,在透明膠片上捕捉到的圖像,通過投射光線穿過負(fù)片,對準(zhǔn)感光紙,將其印在紙上。 隨著電路進(jìn)一步小型化,這一過程需要短波光,來獲得更好的分辨率。最先進(jìn)的微型化技術(shù)需要超紫外或極紫外(EUV)光譜范圍的不可見光。

從光刻機(jī)中“解放”《日經(jīng)》稱,如今阿斯麥爾是光刻機(jī)產(chǎn)業(yè)內(nèi)的壟斷企業(yè),一臺EUV光刻機(jī)的售價大約在1.2億至1.7億美元之間。然而,芯片制造商購買的阿斯麥爾光刻機(jī),實際上只能應(yīng)用于整個芯片制造過程的極小部分,也只能帶來適度的微型化效果。

阿斯麥爾光刻機(jī) 阿斯麥爾官方圖 如今,EUV光刻機(jī)只能用于制造邏輯芯片,如電腦的微型處理器,智能手機(jī)的系統(tǒng)芯片,以及游戲和人工智能領(lǐng)域的圖形處理器等。由于由于電路組成的復(fù)雜性,邏輯芯片尚不能完全使用三維技術(shù)。 對芯片制造商來說,只為制造這些芯片就使用EUV光刻機(jī),成本和難度可能并不那么合理。 實際上,如果一家芯片制造商要使用EUV光刻機(jī),它還需要使用許多其他工藝,來優(yōu)化EUV光刻技術(shù),這就意味著廠商要投入大量資金,來購買各種先進(jìn)設(shè)備。而裝備越先進(jìn),供應(yīng)商就越少,美國的禁令也就越有效。 但是,如今閃存芯片的制造過程已經(jīng)可以跳過EUV光刻機(jī)。 并且,如果能跳過EUV光刻機(jī)的限制,那么芯片制造商的選擇就更多了。《日經(jīng)》稱,日本佳能和尼康,如今也能生產(chǎn)非EUV光刻機(jī)。迄今為止,美國并未禁止這兩家廠商對中國芯片制造商出貨。 另一方面,包括華為在內(nèi),一些中國公司也一直在努力開發(fā)自己的光刻機(jī)。紫光集團(tuán)旗下的長江存儲也在今年宣布成功研發(fā)128層QLC3DNAND閃存(型號:X2-6070),并已在多家控制器廠商SSD等終端存儲產(chǎn)品上通過驗證。 《日經(jīng)》認(rèn)為,當(dāng)前美國方面似乎將限制中國的重點放在EUV光刻機(jī)上,但中國正在積累三維芯片制造技術(shù),這最終將應(yīng)用于先進(jìn)的邏輯芯片,幫助中國避免依賴基于EUV光刻機(jī)的芯片微型化。 并且,從長遠(yuǎn)來看中國有能力提高芯片所有相關(guān)領(lǐng)域的技術(shù),如材料、光學(xué)、化學(xué)、晶圓制造過程控制、表面檢測和功能測試等。 不少專業(yè)人士,也看好中國在芯片制造領(lǐng)域的潛能。曾在中芯國際擔(dān)任首席技術(shù)官的生駒俊明表示,基于他在中國的經(jīng)驗,他認(rèn)為中國有足夠數(shù)量的有能力的科學(xué)家和工程師來開發(fā)自己的芯片制造設(shè)備和芯片設(shè)計軟件。 東京科學(xué)大學(xué)教授若林秀樹表示,開發(fā)芯片制造設(shè)備和材料的整個供應(yīng)鏈不是一朝一夕就能完成的。但他表示,“中國有可能在10至20年內(nèi)成為這一領(lǐng)域的主導(dǎo)國家,因為它在所有科學(xué)和工程領(lǐng)域都擁有大量人才。” 對中國這樣的追趕者而言,技術(shù)趨勢也是一個優(yōu)勢。信息技術(shù)分析機(jī)構(gòu)高德納公司(Gatner)研究副總裁薩繆爾·王(Samuel Wang)表示:“新技術(shù),如新材料、3D、人工智能輔助芯片設(shè)計和基于云技術(shù)的制造協(xié)作,都將為新興企業(yè)創(chuàng)造新的機(jī)會。”

責(zé)任編輯:lq

-

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30768瀏覽量

264440 -

晶體管

+關(guān)注

關(guān)注

78文章

10396瀏覽量

147863 -

人工智能

+關(guān)注

關(guān)注

1817文章

50106瀏覽量

265561

原文標(biāo)題:日媒:半導(dǎo)體科技發(fā)展趨勢有利于中國

文章出處:【微信號:guanchacaijing,微信公眾號:科工力量】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

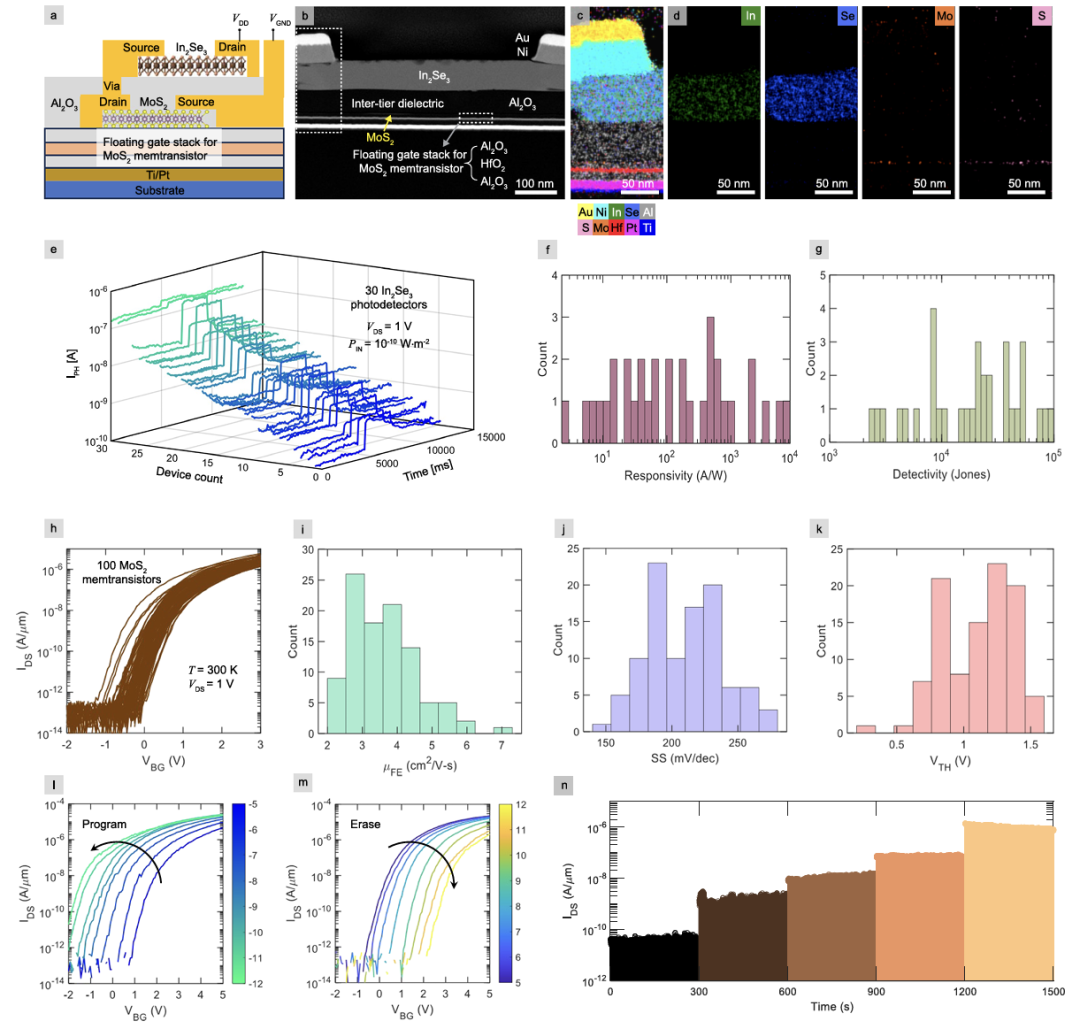

2D材料3D集成實現(xiàn)光電儲備池計算

Neway電機(jī)方案的小型化設(shè)計

MUN5136數(shù)字晶體管技術(shù)解析與應(yīng)用指南

PD快充MOS管高性能低內(nèi)阻SGT工藝場效應(yīng)管HG5511D應(yīng)用方案

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

多值電場型電壓選擇晶體管結(jié)構(gòu)

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

iTOF技術(shù),多樣化的3D視覺應(yīng)用

華大九天推出芯粒(Chiplet)與2.5D/3D先進(jìn)封裝版圖設(shè)計解決方案Empyrean Storm

晶體管架構(gòu)的演變過程

下一代高速芯片晶體管解制造問題解決了!

ZSKY-D882-SOT-89-3L NPN硅功率晶體管規(guī)格書

多值電場型電壓選擇晶體管結(jié)構(gòu)

晶體管電路設(shè)計(下)

下一代3D晶體管技術(shù)突破,半導(dǎo)體行業(yè)迎新曙光!

晶體管小型化遇瓶頸,3D技術(shù)崛起

晶體管小型化遇瓶頸,3D技術(shù)崛起

評論