12月20日,第七屆全國光子和集成電路“創業之芯”大賽總決賽在浙江麗水經開區隆重舉行。本屆活動旨在借助大賽匯聚產學研用優質資源,推動半導體產業高質量發展,提升區域集成電路產業的創新能力和競爭力,為城市發展注入新動能。

2025-12-30 15:39:03 290

290 Molex推出了Temp-Flex TwinMax耐高溫低損耗雙軸電纜是一種具有多阻抗,范圍的平衡傳輸線纜,適用于連接數據中心和電信設備中的10、12和28 Gbps速率電路

2025-12-25 13:46:31

在HFSS仿真鈮酸鋰電光調制器T型電極時,盡管電極設為了完美電導體,介質的介質損耗角正切設為0,dB(S21)仍然有比較大的損耗,導致用ABCD矩陣計算時損耗較大,這是什么原因引起的,如何解決?

2025-12-16 14:36:49

村田LQW15AN系列電感通過 高Q值、低直流電阻(Rdc)、小尺寸封裝及高頻穩定性 等特性,成為高頻射頻電路中實現低損耗的核心解決方案,其技術優勢與應用場景高度契合5G通信、Wi-Fi 6

2025-12-04 16:10:27 470

470

(Terabit)以太網等技術的普及,數據中心必須采用先進的解決方案,以確保高帶寬、低延遲,并最大程度地減少信號衰減。低損耗光纖連接已成為滿足這些性能需求的關鍵技術,在 AI 驅動的環境中提供了顯著的優勢。 接下來,小編將對 AI 數據中心中的低損耗光纖連接進行簡要探

2025-11-25 10:24:15 109

109 信維低損耗MLCC電容在提升電路效率方面表現優異,其核心優勢體現在 低損耗特性、高頻響應能力、小型化設計、高可靠性 以及 廣泛的應用適配性 ,具體分析如下: 一、低損耗特性直接提升電路效率 低介質

2025-11-24 16:30:00 632

632 村田電容在高頻電路中通過材料創新、結構優化與系列化設計,成為低損耗解決方案的核心選擇,其優勢體現在高頻性能、低損耗特性、溫度穩定性及定制化方案四個維度。 一、高頻性能:突破GHz級信號傳輸瓶頸 村田

2025-10-30 16:52:30 563

563 在超高純度晶圓制造過程中,盡管晶圓本身需達到11個9(99.999999999%)以上的純度標準以維持基礎半導體特性,但為實現集成電路的功能化構建,必須通過摻雜工藝在硅襯底表面局部引入特定雜質。

2025-10-29 14:21:31 622

622

在功率半導體封裝領域,晶圓級芯片規模封裝技術正引領著分立功率器件向更高集成度、更低損耗及更優熱性能方向演進。

2025-10-21 17:24:13 3874

3874

一、引言

隨著半導體技術向小型化、高性能化發展,3D 集成封裝技術憑借其能有效提高芯片集成度、縮短信號傳輸距離等優勢,成為行業發展的重要方向 。玻璃晶圓因其良好的光學透明性、化學穩定性及機械強度

2025-10-14 15:24:56 316

316

以下,晶圓表面需達到亞納米級的平整度(如RMS 微觀結構區域的均勻去除:在三維集成電路(如FinFET晶體管或3D NAND閃存)中,不同材料的交疊區域存在物理特性差異,如何實現全局與局部同步平坦化成為關鍵難題。例如,多層金屬互連層間的

2025-10-13 10:37:52 470

470 、切片、拋光等工序制成,未經任何使用歷史。其原材料通常來自二氧化硅礦石提煉的高純硅料,經過嚴格控溫的長晶過程形成圓柱形單晶硅棒,再切割成薄片后成為集成電路制造的基礎

2025-09-23 11:14:55 774

774

對需要高精度、高頻段、遠距離傳輸的場景來說,SMA 低損耗款不是 “可選項”,而是 “必選項”—— 普通款的損耗看似不大,但疊加后會嚴重影響系統性能,而低損耗款通過材質、結構、工藝的優化,能最大限度 “守住” 信號能量,提升系統效率、降低成本。

2025-09-19 10:10:00 1754

1754

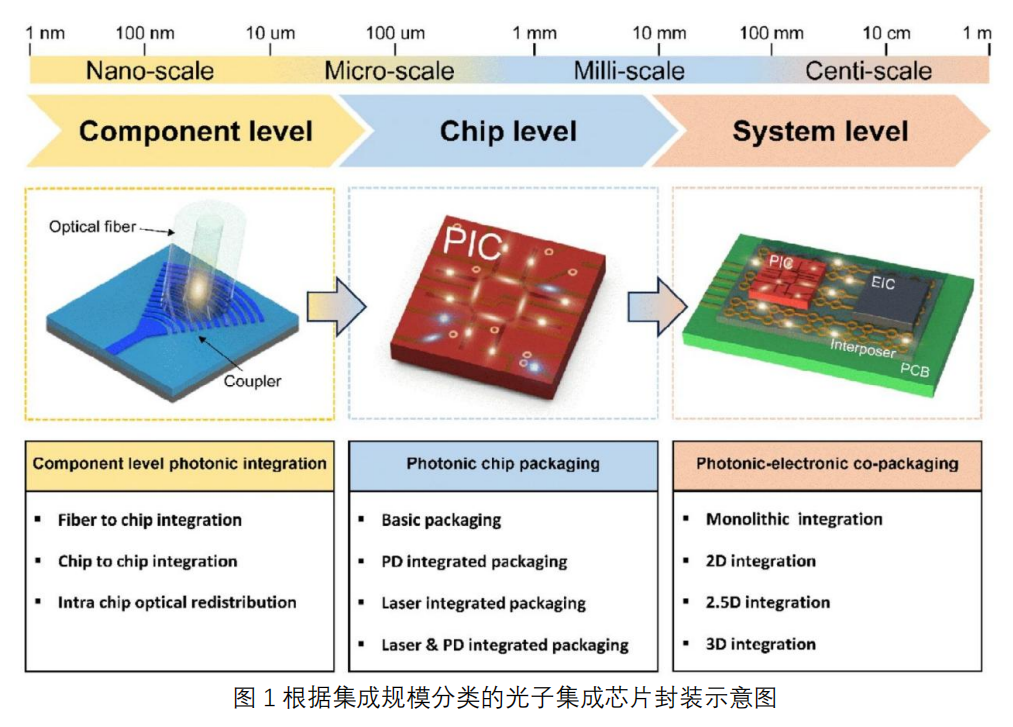

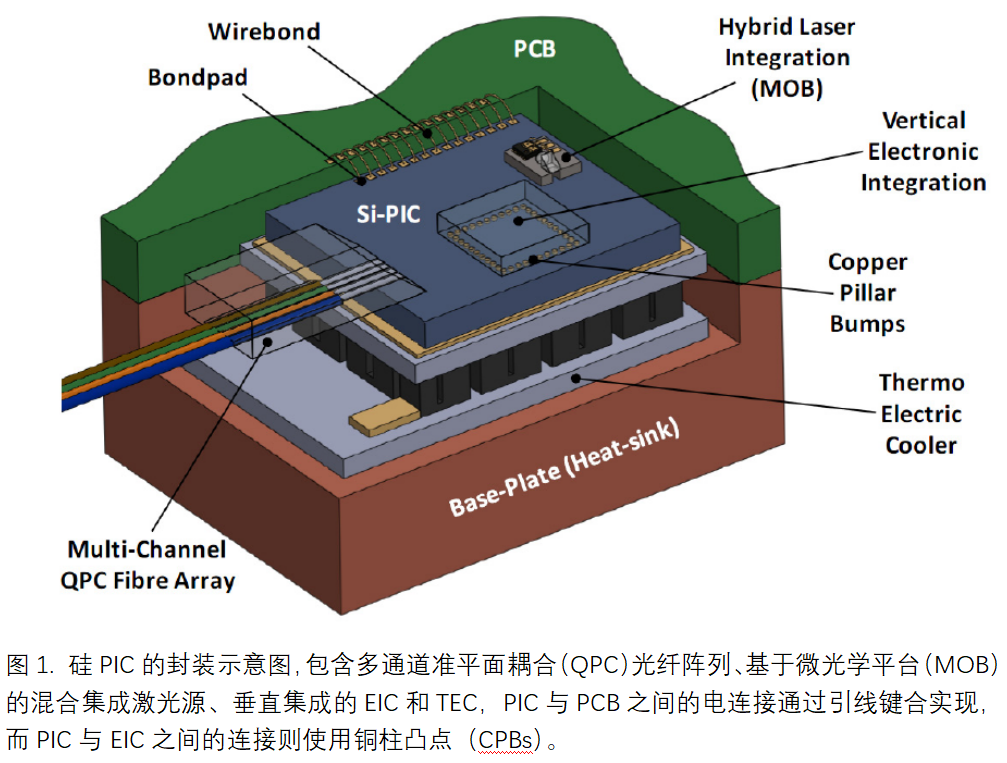

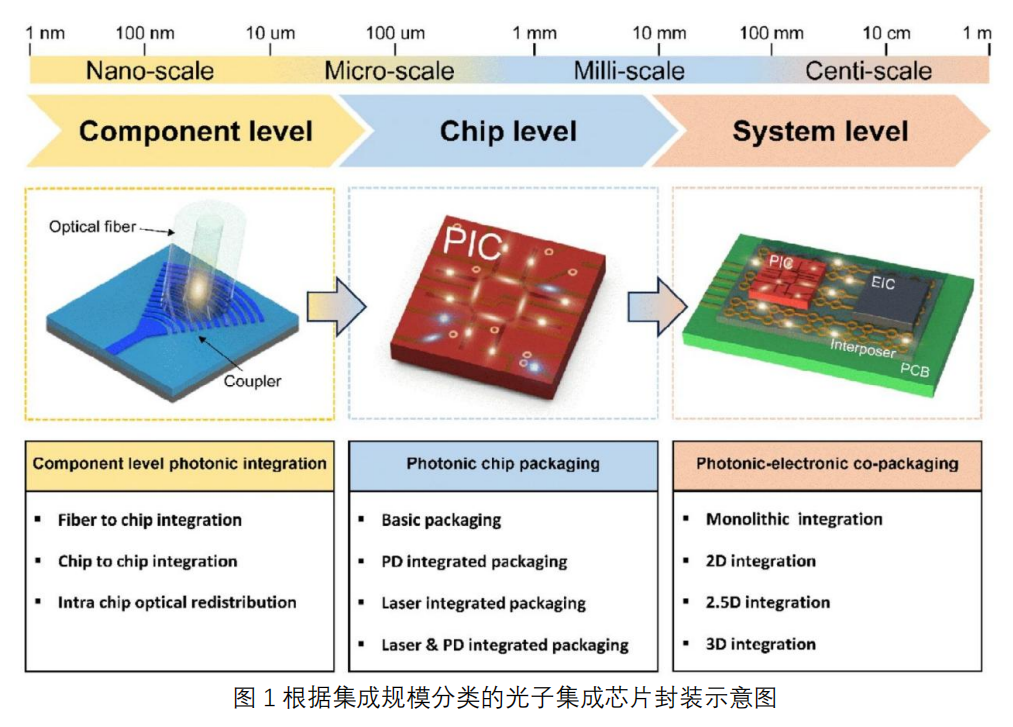

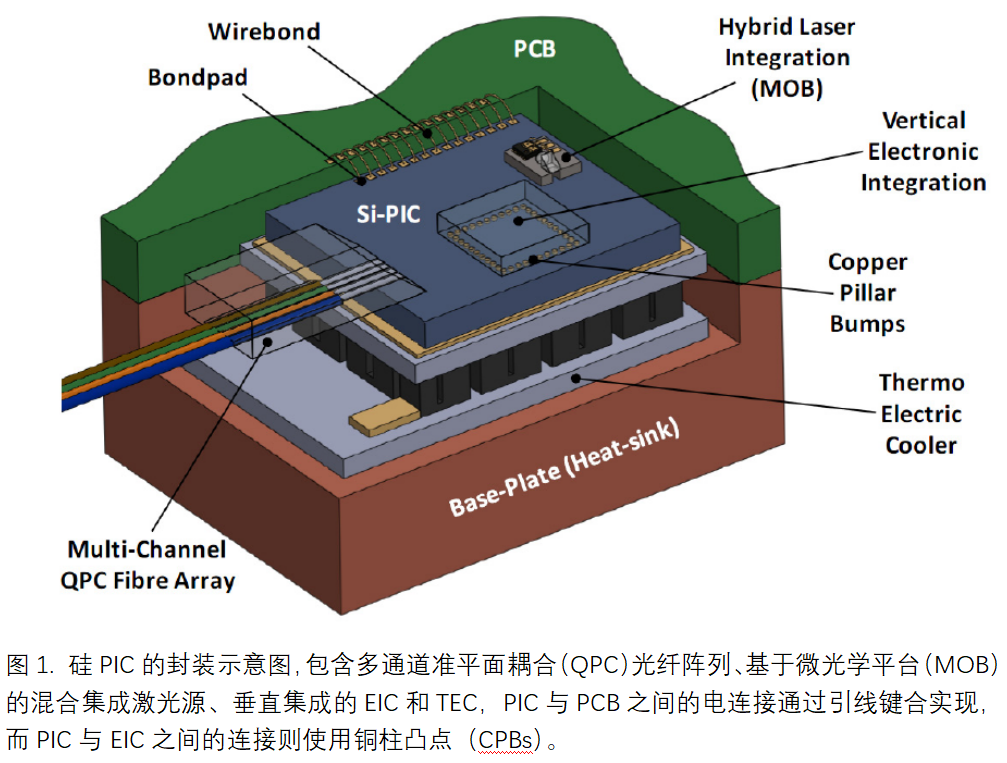

據中心領域的快速發展,對高速數據處理與傳輸提出了更高要求。為滿足 這些需求,器件封裝技術的發展聚焦于實現小型化、高效率和高性能,而光子集成芯片封裝 正是滿足這些需求的理想方案。本文綜述了光子集成芯片封裝在元件級、芯片級和

2025-09-18 11:10:56 887

887

翻譯自 Lee Carroll在 2016年發表的文章 摘要 晶圓廠提供的光子集成電路PIC的多項目晶圓(MPW)服務,使得研究人員和中小型企業(SMEs)能夠低成本完成硅光子芯片的設計和制造。盡管

2025-08-28 10:11:17 1063

1063

簡單來說,Die(發音為/da?/,中文常稱為裸片、裸晶、晶粒或晶片)是指從一整片圓形硅晶圓(Wafer)上,通過精密切割(Dicing)工藝分離下來的、單個含有完整集成電路(IC)功能的小方塊。

2025-08-21 10:46:54 3216

3216 在半導體制造的精密世界里,每一個微小的改進都可能引發效率的飛躍。今天,美能光子灣科技將帶您一探晶圓背面磨削工藝中的關鍵技術——總厚度變化(TTV)控制的奧秘。隨著三維集成電路3DIC制造技術

2025-08-05 17:55:08 3372

3372

電子發燒友網為你提供()低損耗雙向功率分配器/合路器 2.2–2.8 GHz相關產品參數、數據手冊,更有低損耗雙向功率分配器/合路器 2.2–2.8 GHz的引腳圖、接線圖、封裝手冊、中文資料、英文

2025-07-30 18:34:36

晶圓清洗機中的晶圓夾持是確保晶圓在清洗過程中保持穩定、避免污染或損傷的關鍵環節。以下是晶圓夾持的設計原理、技術要點及實現方式: 1. 夾持方式分類 根據晶圓尺寸(如2英寸到12英寸)和工藝需求,夾持

2025-07-23 14:25:43 929

929 不同晶圓尺寸的清洗工藝存在顯著差異,主要源于其表面積、厚度、機械強度、污染特性及應用場景的不同。以下是針對不同晶圓尺寸(如2英寸、4英寸、6英寸、8英寸、12英寸等)的清洗區別及關鍵要點:一、晶圓

2025-07-22 16:51:19 1332

1332

在集成電路生產過程中,晶圓背面二氧化硅邊緣腐蝕現象是一個常見但復雜的問題。每個環節都有可能成為晶圓背面二氧化硅邊緣腐蝕的誘因,因此需要在生產中嚴格控制每個工藝參數,尤其是對邊緣區域的處理,以減少這種現象的發生。

2025-07-09 09:43:08 761

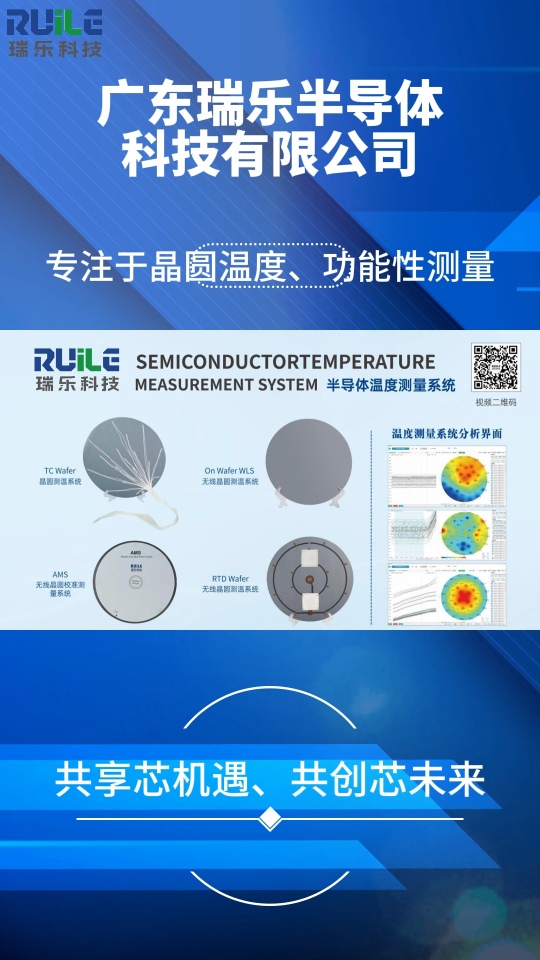

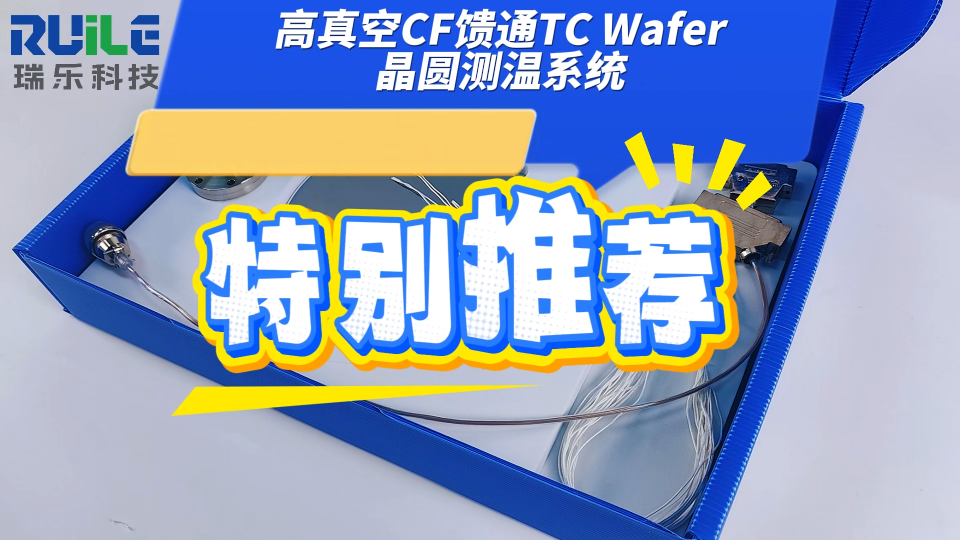

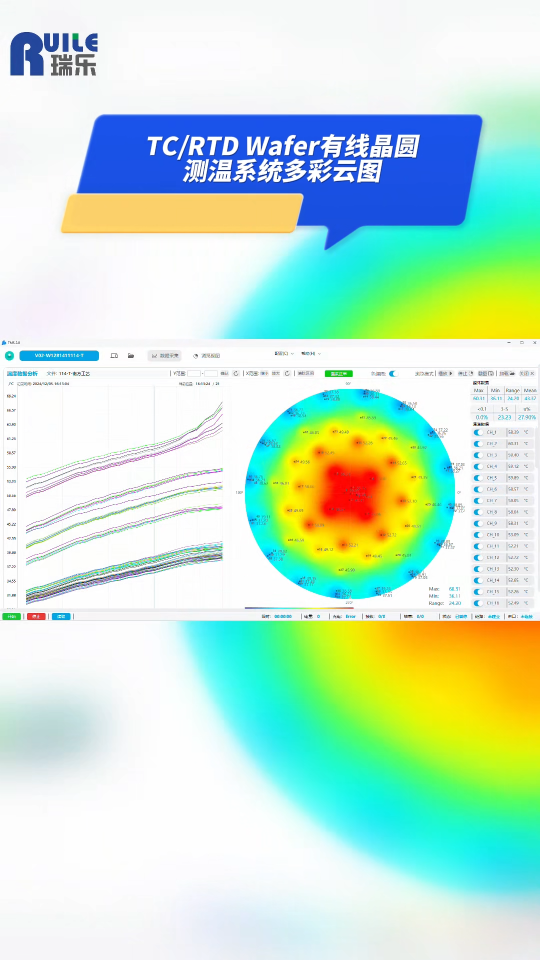

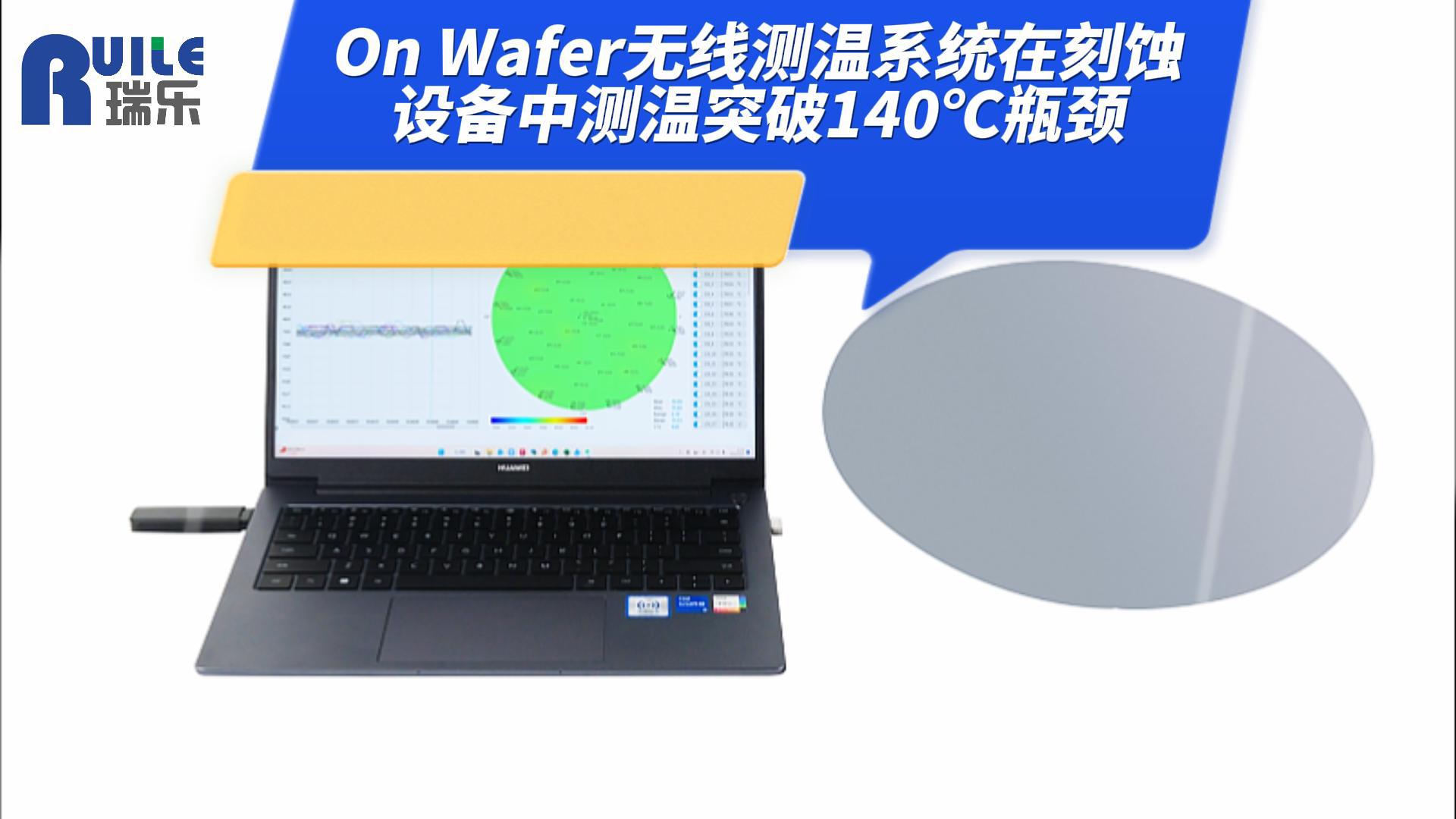

761 On Wafer WLS無線晶圓測溫系統通過自主研發的核心技術將傳感器嵌入晶圓集成,實時監控和記錄晶圓在制程過程中的溫度變化數據,為半導體制造過程提供一種高效可靠的方式來監測和優化關鍵

2025-06-27 10:37:30

并購重組審核委員會審議通過,后續尚需取得中國證監會同意注冊的決定后方可實施。 芯聯集成是全球領先的集成電路晶圓代工企業之一,根據ChipInsights發布的《2024年全球專屬晶圓代工排行榜》,芯聯集成躋身2024年全球專屬晶圓代工榜單前十,中

2025-06-25 18:11:40 1062

1062

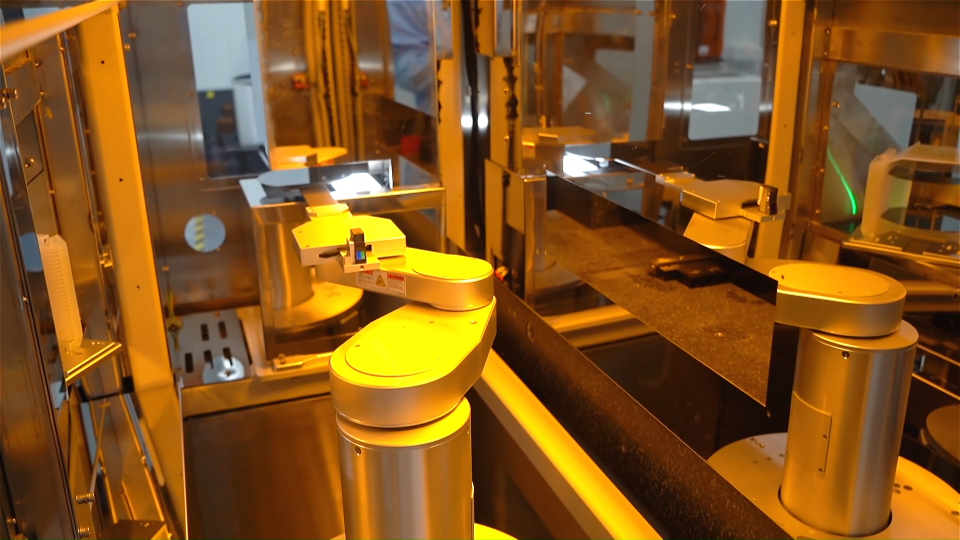

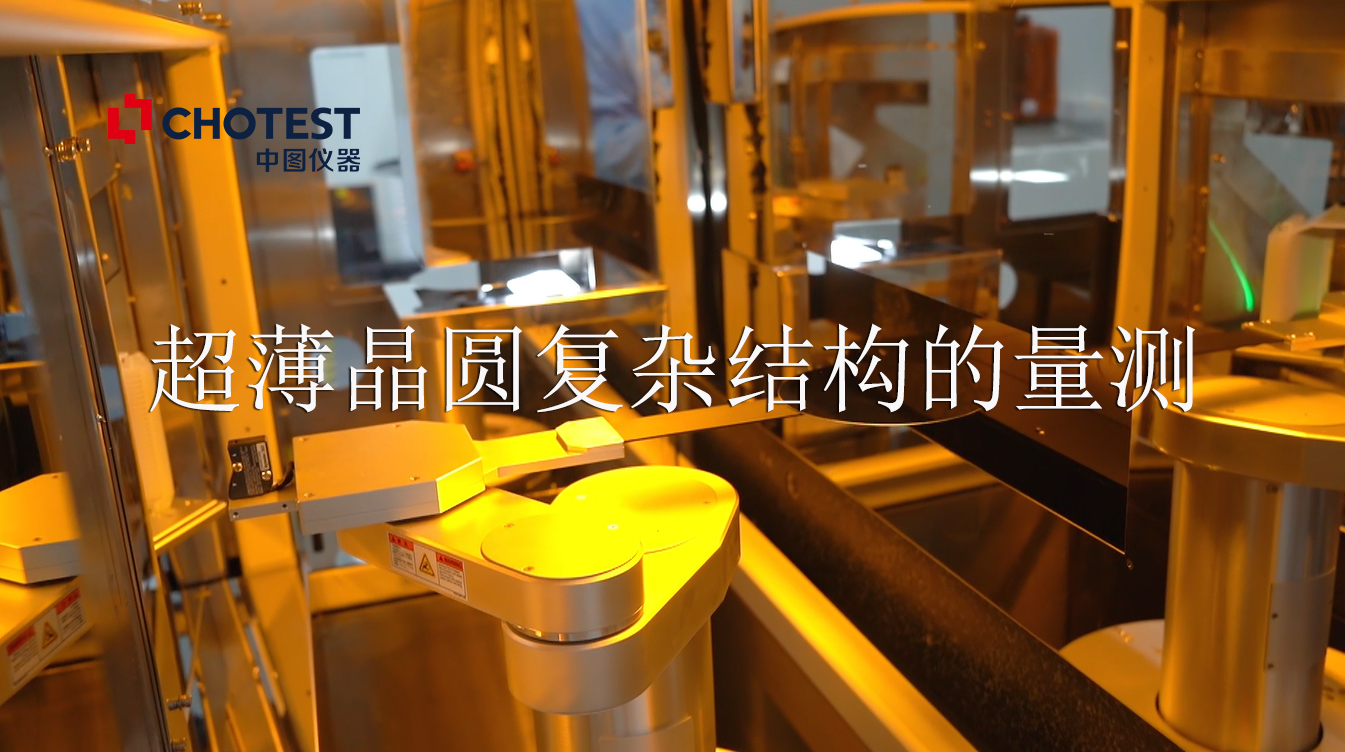

WD4000晶圓厚度測量設備兼容不同材質不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數據更準確。它通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩定計算晶圓厚度,TTV,BOW

2025-06-18 15:40:06

高反射率的物體表面,從納米到微米級別工件的厚度、粗糙度、平整度、微觀幾何輪廓、曲率等,實現砷化鎵、氮化鎵、磷化鎵、鍺、磷化銦、鈮酸鋰、藍寶石、硅、碳化硅、玻璃不同

2025-06-16 15:08:07

摘要:本文探討晶圓邊緣 TTV 測量在半導體制造中的重要意義,分析其對芯片制造工藝、器件性能和生產良品率的影響,同時研究測量方法、測量設備精度等因素對測量結果的作用,為提升半導體制造質量提供理論依據

2025-06-14 09:42:58 552

552

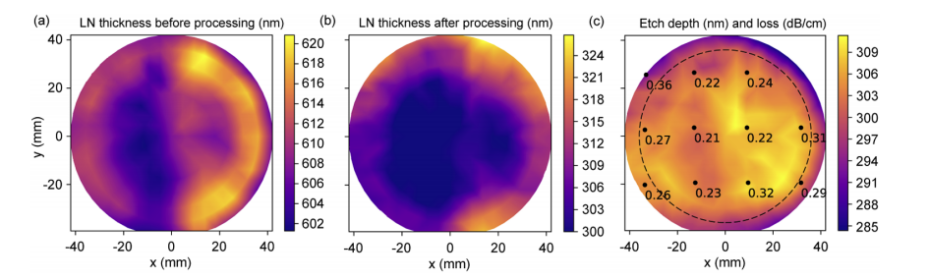

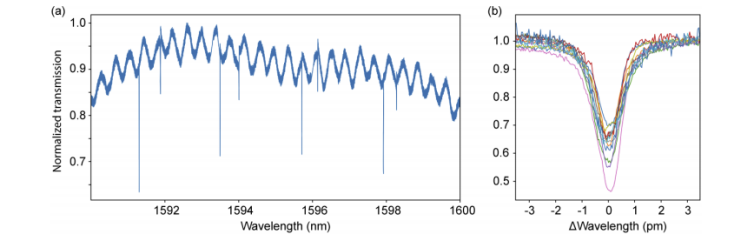

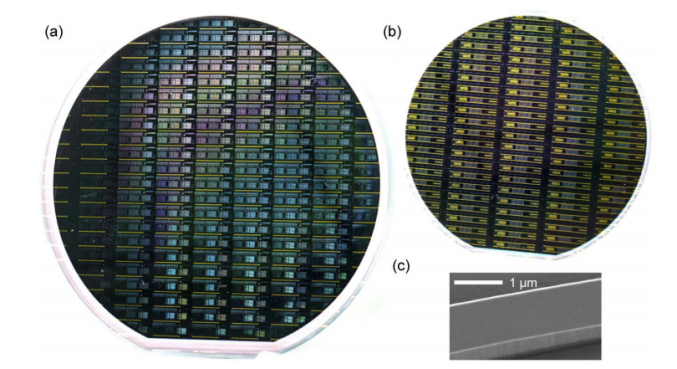

電子發燒友網綜合報道 近日消息,上海交大無錫光子芯片研究院(CHIPX)取得重大進展,其在國內首個光子芯片中試線成功下線首片6英寸薄膜鈮酸鋰光子芯片晶圓,并同步實現了超低損耗、超高帶寬的高性能薄膜鈮

2025-06-13 01:02:00 4852

4852 的 Ari Novack 和 Matthew Streshinsky 創立。 Enosemi 專注于光子集成電路(PIC)研發 ,而且僅僅有

2025-06-04 16:38:27 1152

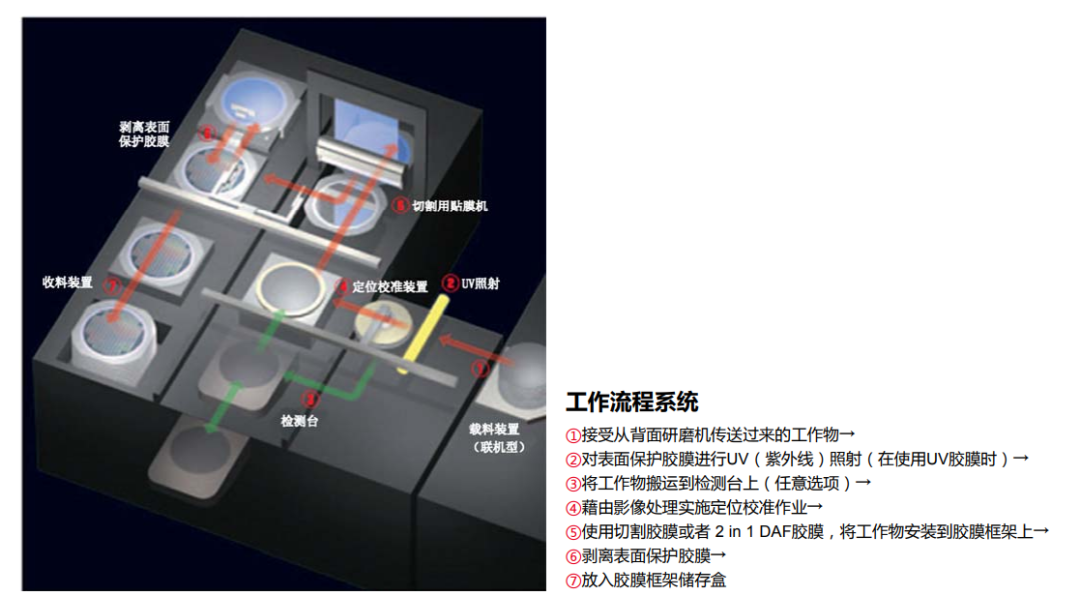

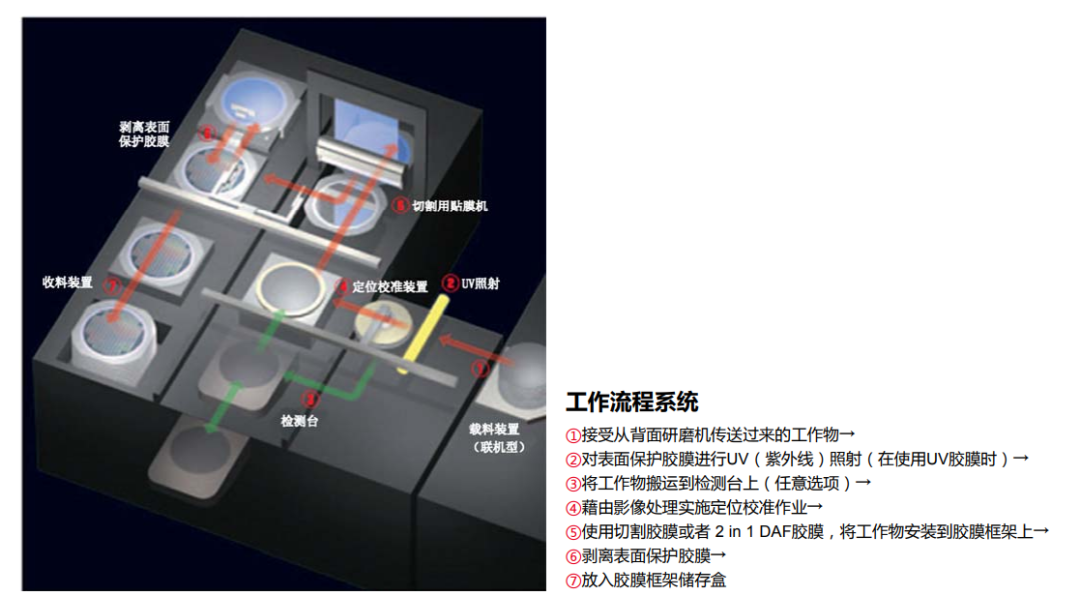

1152 貼膜是指將一片經過減薄處理的晶圓(Wafer)固定在一層特殊的膠膜上,這層膜通常為藍色,業內常稱為“ 藍膜 ”。貼膜的目的是為后續的晶圓切割(劃片)工藝做準備。

2025-06-03 18:20:59 1180

1180

反應表面形貌的參數。可實現砷化鎵、氮化鎵、磷化鎵、鍺、磷化銦、鈮酸鋰、藍寶石、硅、碳化硅、玻璃不同材質晶圓的量測。兼容不同材質不同粗糙度、可測量大翹曲wafer、

2025-05-30 11:03:11

晶圓是半導體制造的核心基材,所有集成電路(IC)均構建于晶圓之上,其質量直接決定芯片性能、功耗和可靠性,是摩爾定律持續推進的物質基礎。其中晶圓的厚度(THK)、翹曲度(Warp) 和彎曲度(Bow

2025-05-28 16:12:46

關鍵詞:鍵合晶圓;TTV 質量;晶圓預處理;鍵合工藝;檢測機制 一、引言 在半導體制造領域,鍵合晶圓技術廣泛應用于三維集成、傳感器制造等領域。然而,鍵合過程中諸多因素會導致晶圓總厚度偏差(TTV

2025-05-26 09:24:36 854

854

摘要:本文針對濕法腐蝕工藝后晶圓總厚度偏差(TTV)的管控問題,探討從工藝參數優化、設備改進及檢測反饋機制完善等方面入手,提出一系列優化方法,以有效降低濕法腐蝕后晶圓 TTV,提升晶圓制造質量

2025-05-22 10:05:57 511

511

摘要:本文聚焦于降低晶圓 TTV(總厚度偏差)的磨片加工方法,通過對磨片設備、工藝參數的優化以及研磨拋光流程的改進,有效控制晶圓 TTV 值,提升晶圓質量,為半導體制造提供實用技術參考。 關鍵詞:晶

2025-05-20 17:51:39 1028

1028

前言在半導體制造的前段制程中,晶圓需要具備足夠的厚度,以確保其在流片過程中的結構穩定性。盡管芯片功能層的制備僅涉及晶圓表面幾微米范圍,但完整厚度的晶圓更有利于保障復雜工藝的順利進行,直至芯片前制程

2025-05-16 16:58:44 1110

1110

在半導體制造流程中,晶圓在前端工藝階段需保持一定厚度,以確保其在流片過程中的結構穩定性,避免彎曲變形,并為芯片制造工藝提供操作便利。不同規格晶圓的原始厚度存在差異:4英寸晶圓厚度約為520微米,6

2025-05-09 13:55:51 1976

1976 在半導體制造流程中,晶圓揀選測試(Wafer Sort)堪稱芯片從“原材料”到“成品”的關鍵質控節點。作為集成電路制造中承上啟下的核心環節,其通過精密的電學測試,為每一顆芯片頒發“質量合格證”,同時為工藝優化提供數據支撐。

2025-04-30 15:48:27 5746

5746

的功率驅動部分。前級控制電路容易實現集成,通常是模擬數字混合集成電路。對于小功率系統,末級驅動電路也已集成化,稱之為功率集成電路。功率集成電路可以將高電壓、大電流、大功率的多個半導體開關器件集成在同一個

2025-04-24 21:30:16

本書共13章。第1章緒論,介紹國內外電機控制專用集成電路發展情況,電機控制和運動控制、智能功率集成電路概況,典型閉環控制系統可以集成的部分和要求。第2~7章,分別敘述直流電動機、無刷直流電動機、步進

2025-04-22 17:02:31

資料介紹本文系《中國集成電路大全》的接口集成電路分冊,是國內第一次比較系統地介紹國產接口集成電路的系列、品種、特性和應用方而知識的書籍。全書共有總表、正文和附錄三部分內容。總表部分列有國產接口

2025-04-21 16:33:37

ME-Pro是概倫電子自主研發的用于聯動集成電路工藝與設計的創新性驗證評估平臺,為集成電路設計、CAD、工藝開發、SPICE模型和PDK專業從業人員提供了一個共用平臺。

2025-04-16 09:34:33 1687

1687

本文介紹了半導體集成電路制造中的晶圓制備、晶圓制造和晶圓測試三個關鍵環節。

2025-04-15 17:14:37 2159

2159

光庫科技96 GBaud和130 GBaud薄膜鈮酸鋰(TFLN)相干驅動調制器(CDM)產品現已實現面向全球頭部客戶批量出貨。

2025-03-27 13:43:28 937

937 光庫科技自主研發的AM70超高速薄膜鈮酸鋰(TFLN)調制器正式進入規模量產階段,并開始向全球客戶批量交付。

2025-03-25 10:09:35 1252

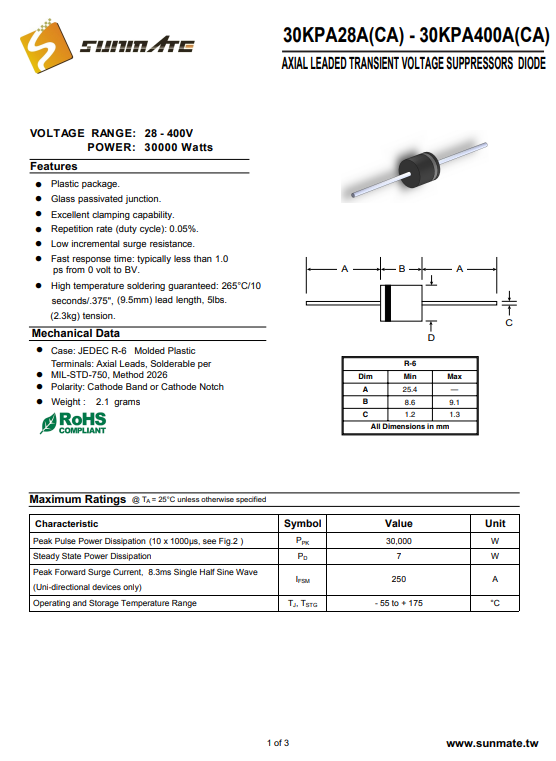

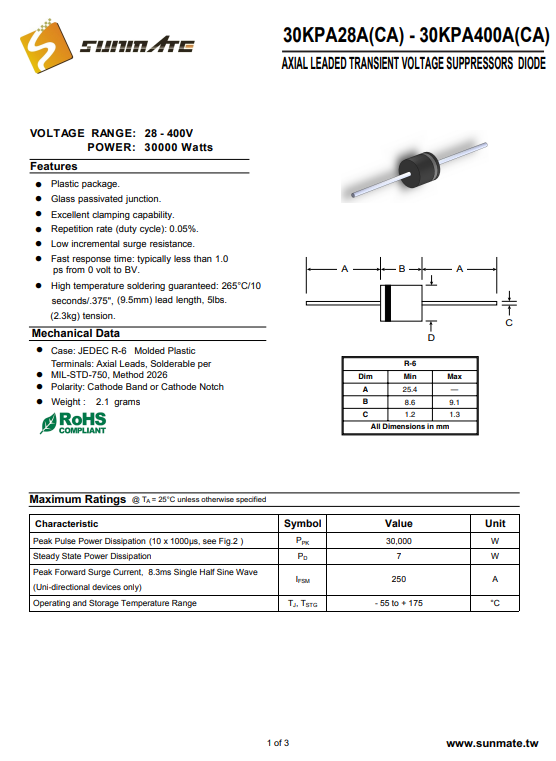

1252 30KPA168A單向二極管:高耐壓,低損耗,性能卓越

2025-03-15 14:19:52 17238

17238

半導體芯片集成電路(IC)工藝是現代電子技術的核心,涉及從硅材料到復雜電路制造的多個精密步驟。以下是關鍵工藝的概述:1.晶圓制備材料:高純度單晶硅(純度達99.9999999%),通過直拉法

2025-03-14 07:20:00 1443

1443

本文介紹了集成電路和光子集成技術的發展歷程,并詳細介紹了鈮酸鋰光子集成技術和硅和鈮酸鋰復合薄膜技術。

2025-03-12 15:21:24 1689

1689

圓不僅是芯片制造的基礎材料,更是連接設計與現實的橋梁。在這張畫布上,光刻、刻蝕、沉積等工藝如同精妙的畫筆,將虛擬的電路圖案轉化為現實的功能芯片。 晶圓:從砂礫到硅片 晶圓的起點是普通的砂礫,其主要成分是二氧化硅(SiO?

2025-03-10 17:04:25 1544

1544 隨著半導體技術的飛速發展,晶圓級封裝(WLP)作為先進封裝技術的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。在晶圓級封裝過程中,Bump工藝扮演著至關重要的角色。Bump,即凸塊,是晶圓級封裝中

2025-03-04 10:52:57 4980

4980

硅作為半導體材料在集成電路應用中的核心地位無可爭議,然而,隨著科技的進步和器件特征尺寸的不斷縮小,硅集成電路技術正面臨著一系列挑戰,本文分述如下:1.硅集成電路的優勢與地位;2.硅材料對CPU性能的影響;3.硅材料的技術革新。

2025-03-03 09:21:49 1385

1385

CSBA系列通過采用低損耗金屬磁粉芯材料和優化的線圈結構,進一步降低磁芯損耗和電阻損耗,從而提升氮化鎵電源的整體效率。例如,在數據中心服務器電源中,低損耗電感可減少能源浪費,符合綠色節能的發展趨勢。

2025-02-20 10:50:17 1010

1010

集成電路為什么要封膠?漢思新材料:集成電路為什么要封膠集成電路封膠的主要原因在于提供多重保護和增強性能,具體來說包括以下幾個方面:防止環境因素損害:集成電路在工作過程中可能會受到靜電、濕氣、灰塵等

2025-02-14 10:28:36 957

957

一、集成電路的引腳識別 集成電路是在同一塊半導體材料上,利用各種不同的加工方法同時制作出許多極其微小的電阻、電容及晶體管等電路元器件,并將它們相互連接起來,使之具有特定功能的電路。半導體集成電路

2025-02-11 14:21:22 1903

1903 在半導體制造的復雜流程中,晶圓歷經前道工序完成芯片制備后,劃片工藝成為將芯片從晶圓上分離的關鍵環節,為后續封裝奠定基礎。由于不同厚度的晶圓具有各異的物理特性,因此需匹配不同的切割工藝,以確保切割效果與芯片質量。

2025-02-07 09:41:00 3050

3050

據新華社報道,日前,自南開大學獲悉,南開大學攜手香港城市大學,成功研制出薄膜鈮酸鋰光子毫米波雷達芯片,在毫米波雷達領域取得重大突破。這一創新成果,為未來6G通信、智能駕駛、精準感知等前沿領域

2025-02-06 09:42:57 665

665

在當今數字化的時代,電子技術改變著我們的生活方式。而集成電路,作為電子技術的核心驅動力,更是發揮著至關重要的作用。 集成電路,簡稱 IC,是將大量的晶體管、電阻、電容等電子元件以及它們之間的連線

2025-02-05 11:06:00 646

646 在半導體制造領域,晶圓作為芯片的基礎母材,其質量把控的關鍵環節之一便是對 BOW(彎曲度)的精確測量。而在測量過程中,特氟龍夾具的晶圓夾持方式與傳統的真空吸附方式有著截然不同的特性,這些差異深刻影響

2025-01-21 09:36:24 520

520

來源:Yole Group 光子集成電路正在通過實現更快的數據傳輸、推進量子計算技術、以及變革醫療行業來徹底改變多個領域。在材料和制造工藝的創新驅動下,光子集成電路有望重新定義光學技術的能力,并在

2025-01-13 15:23:03 1082

1082 在半導體制造領域,晶圓的加工精度和質量控制至關重要,其中對晶圓 BOW(彎曲度)和 WARP(翹曲度)的精確測量更是關鍵環節。不同的吸附方案被應用于晶圓測量過程中,而晶圓的環吸方案因其獨特

2025-01-09 17:00:10 639

639

晶圓是集成電路、功率器件及半導體分立器件的核心原材料,超過90%的集成電路均在高純度、高品質的晶圓上制造而成。晶圓的質量及其產業鏈供應能力,直接關乎集成電路的整體性能和競爭力。今天我們將詳細介紹

2025-01-09 09:59:26 2100

2100

。在此之前,皖芯集成的注冊資本僅為5000.01萬元。 本次增資完成后,晶合集成持有皖芯集成的股權比例變更為43.75%,仍為第一大股東。 據TrendForce公布的24Q1全球晶圓代工廠商營收排名,晶合集成位居全球前九,是中國大陸本土第三的晶圓代工廠商。

2025-01-07 17:33:09 778

778

隨著半導體技術的飛速發展,晶圓級封裝(Wafer Level Packaging, WLP)作為一種先進的封裝技術,正逐漸在集成電路封裝領域占據主導地位。晶圓級封裝技術以其高密度、高可靠性、小尺寸

2025-01-07 11:21:59 3190

3190

電子發燒友App

電子發燒友App

評論