翻譯自Lee Carroll在2016年發表的文章

摘要

晶圓廠提供的光子集成電路PIC的多項目晶圓(MPW)服務,使得研究人員和中小型企業(SMEs)能夠低成本完成硅光子芯片的設計和制造。盡管這些硅光芯片可以在探針臺上測試,但如果不將它們封裝起來,就無法開發成樣機,無法在實驗室外進行測試。PIC的光子封裝比電子封裝更具挑戰性,成本高出幾個數量級,因為它需要可靠的um級光學對準、精確的溫度控制,且通常需要高度的垂直和水平電學集成。光子封裝或許是開發具有商業價值的集成光子器件過程中最顯著的瓶頸。本文闡述了如何滿足硅PIC封裝的光、電和熱要求,以及在實現規模化量產之前還需要做的工作。

關鍵詞:

光子封裝;硅光子學;集成光學;光電子學;光子集成電路(PICs)

1. 引言

過去十年,硅光子學被視為在電信、數通、醫療技術、安全和傳感等領域實現革命性進展的平臺[1-3]。其背后的主要驅動力是,小型化高集成度的光子系統,這些子系統可以利用CMOS電子學的幾十年豐富制造經驗、技術和可擴展性[4]。最終目標是開發出具有集成電路EIC類似的低成本、高容量光子集成芯片(PICs),并充分利用硅平臺的全部潛力—即硅光子用于高速信號傳輸和感知,CMOS電子用于后續的邏輯運算和計算[5]。

人們已經開發了系列硅光子元件,這些元件作為基礎“構件”,在幾家硅晶圓廠提供的MPW服務中使用[6-8]。這些元件包括一維(1D)和二維(2D)光柵耦合器、邊耦合器、條形/脊形波導和交叉結構、多模干涉(MMI)分束器、階梯光柵和陣列波導(AWG)復用器/解復用器、熱可調諧微環諧振器、高速鍺光電二極管、熱光移相器、電吸收調制器(EAMs)等。從理論上講,數千個這樣的光子元件,或許還有幾十個簡單的硅光芯片(PIC)設計,可以布局在單個MPW“區塊”(通常為10-30mm2)上,學術研究人員和中小型企業(SMEs)通常將其用作光子設計的測試平臺。然而,開發創新的PIC并在實驗室環境中(無論是在光學平臺上還是在探針臺上)展示其功能,只是邁向實用器件的第一步,這些器件需要能夠吸引投資并在市場上產生關注度和價值。在將硅PIC產品化的過程中,相關的技術挑戰往往被低估,甚至在硅PIC設計階段被完全忽視,這導致第一代樣機的性能顯著下降,制造成本不必要地增加。

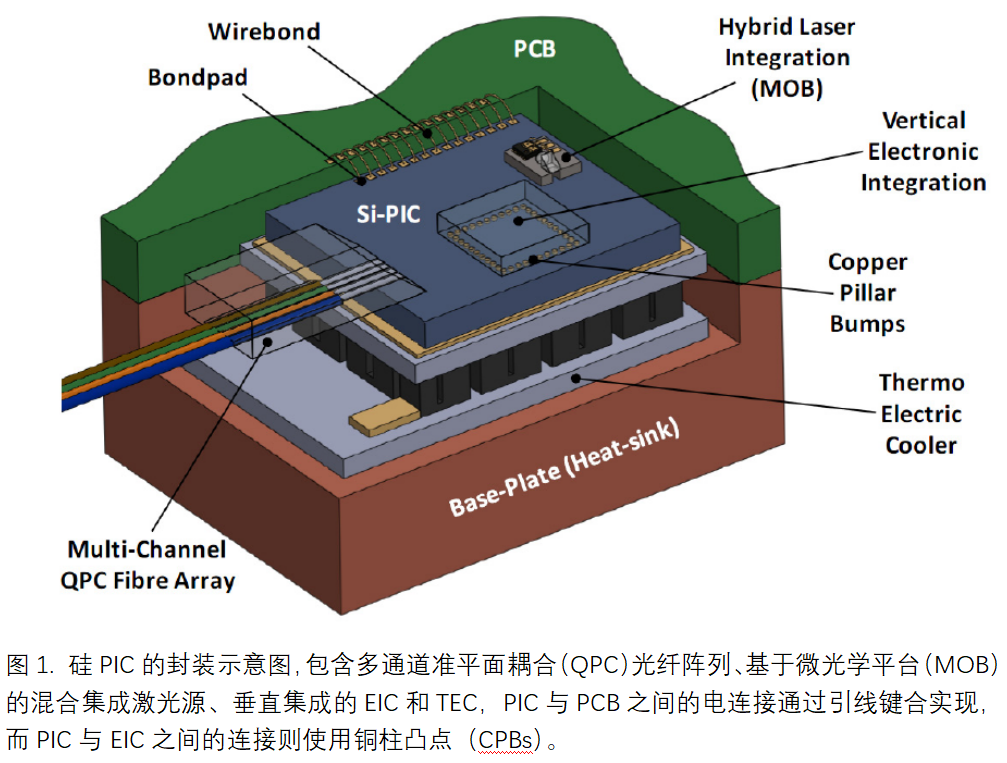

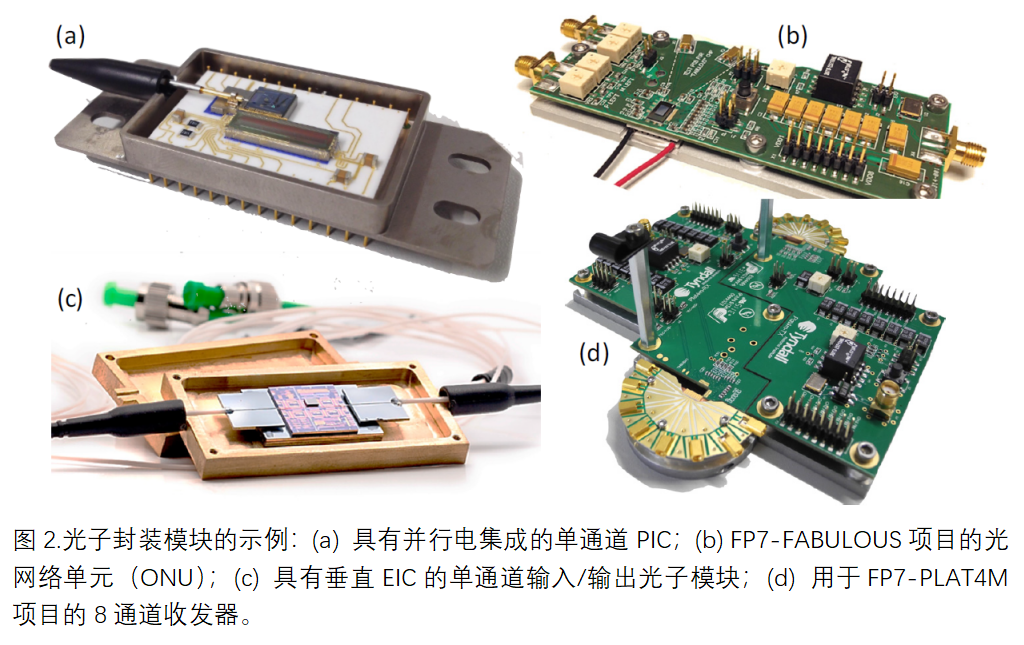

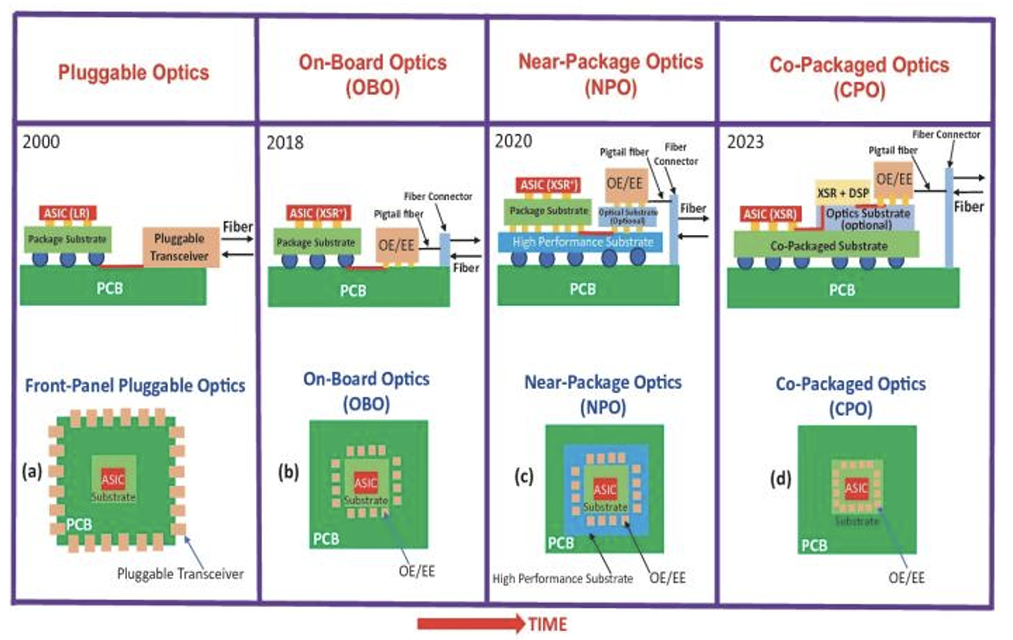

“光子封裝”技術涵蓋了多種技術和專業能力,這些技術和能力用于在PIC與外部建立光學、電學、熱學、機械、甚至化學連接[9-12]。“光子封裝“除了包括大家數值的光纖與PIC的耦合,還包括在PIC上集成激光芯片、微光學元件、電芯片和微流體器件;將高速25Gbps傳輸線通過阻抗匹配的方式從外部連接到PIC上;以及為保證PIC正常工作所需的高效熱管理—見圖1和圖2。

雖然滿足這些光子封裝要求中的任何一項可能都不難,但要在一個獨立可靠的器件中實現全部這些要求以進行現場樣機測試卻不容易,在更先進的光子器件中更是如此,這些器件需要同時采用多種不同的封裝技術,例如多通道光纖與PIC耦合、垂直集成的驅動芯片、高速連接以及TEC[12]。為確保這些器件在制造和組裝后能完全正常工作,需要在硅PIC設計階段就采用封裝設計規則(PDRs)。本文介紹光子封裝中需考慮的各種光學、電學和熱學因素,作為封裝設計規則的“入門指南”,同時也介紹了一些有助于光子器件產業化的趨勢。

2. 光學封裝

硅作為間接帶隙半導體,用于激光發射的直接帶隙復合概率非常低。因此,所需的光信號必須來自外部激光源,要么間接(即從分立激光器件通過光纖耦合光),要么直接(即III-V族器件/材料與硅PIC的混合/異質集成)。激光與PIC的間接和直接耦合有許多方式,每種方式還可以根據所采用的耦合方案進一步細分,例如光柵耦合、邊耦合、倏逝耦合等。光纖與PIC的間接耦合常用于電信和數通應用,因為它允許通過光纖網絡傳輸信息,而集成光源直接耦合則用于安全和傳感應用。

2.1. 光纖與PIC的耦合

單模光纖SMF與硅PIC上典型波導之間傳輸光的主要挑戰在于兩種材料系統的模場直徑MFD存在巨大差異。在通信波長(1260-1650nm)下,光纖中的模場直徑約為10μm且呈圓對稱,而PIC中的模場直徑通常呈橢圓形,尺寸為0.5×0.3μm[13]。因此,除了兩種波導的模場尺寸存在一個數量級的差異外,如果單模光纖模式中電場的未知且不穩定方向與PIC波導的基偏振方向(電信和數通應用通常為TE橫電,傳感應用通常為TM橫磁)不一致,還會帶來偏振相關損耗PDL。因此,通常需要某種形式的“偏振管理”以確保光纖與PIC耦合——要么直接在耦合器元件本身(如二維光柵耦合器[14]),要么在PIC的后續階段(如必要用于濾波和旋轉偏振的波導元件[15])。如下面三個小節描述的,光纖與PIC的耦合主要有三種方法:邊耦合、光柵耦合,以及最近出現的倏逝耦合,每種方法都有其自身的性能優勢和局限性,適用于特定的應用。表1給出了這些不同耦合方法對比。

2.1.1. 邊耦合

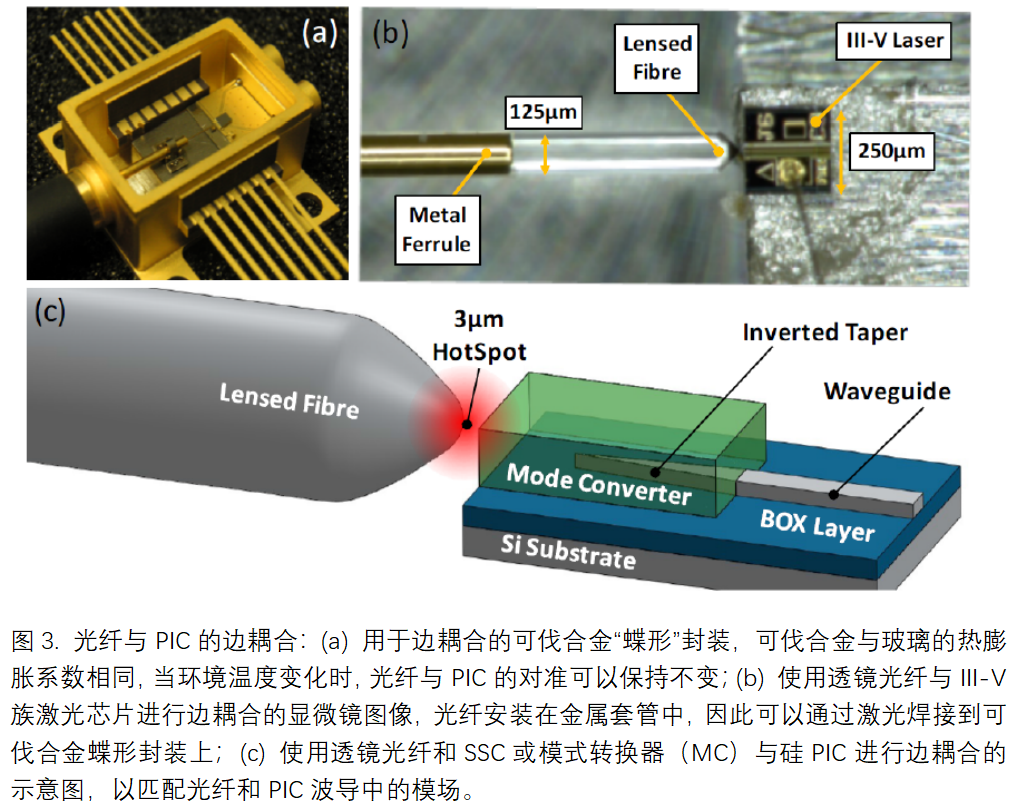

邊耦合是激光芯片商業封裝中一種成熟的方法[16],具有低耦合損耗(小于1dB)、寬光譜、偏振無關等優良特性 [17],但在硅光子學領域尚未被廣泛采用。硅PIC的典型邊耦合器由嵌入氮化物模場轉換器SSC或后處理沉積的聚合物倒錐結構(長度為100-300μm)組成的SSC,以將PIC上波導模式的MFD增加到約3×3μm[18,19],這與透鏡SMF-28光纖或超高數值孔徑(UHNA)光纖形成良好的模場重疊,見圖3。

由于需沉積和蝕刻3-5um SiON層來制作集成的模式適配器,很難成為標準構件(主要是因為SiON層給晶圓帶來了高應變),因此晶圓廠將難以在MPW中引入模場轉換。在Si-PIC上添加邊耦合器也會增加制造后的處理成本,因為它需要對PIC邊緣進行精確的切割和拋光,或者需深蝕刻(>60um)光刻以創建一個刻面和V槽(用于使用無源對準方式將光纖與PIC波導對準),這種方式的主要缺陷是V槽占用了Si-PIC上較大空間。

大多數情況下,邊耦合在PIC和透鏡光纖之間進行。光纖端面的透鏡形成3μm直徑的光“熱點”,使光纖模式與PIC上的模場轉換器的模場直徑更好地匹配。這種邊耦合器的1dB對準公差通常為亞微米級(約±500nm),因此需要有源對準以降低插入損耗[18,19]。鑒于此對準公差與多通道光纖陣列的制造公差相當,邊耦合幾乎總是僅用于單通道光纖與PIC的耦合。此外,通常需要將安裝在金屬套管中的透鏡光纖和PIC激光焊接到可伐合金封裝上,以確保熱脹冷縮引起的位移不會影響光纖與PIC的耦合(可伐合金是一種鐵-鎳-鈷合金,具有與光纖中的玻璃匹配的熱膨脹系數),見圖3。此外,這種金屬間的鍵合比環氧樹脂鍵合更不易因老化環境影響而發生微小的對準漂移[16]。顯然,當前最先進的邊耦合的對準公差和材料要求過高,難以可靠地滿足中高產量(每年10?-10?個器件)的需求。

邊耦合通常用于硅光子學中的非線性應用,這些應用通常需要較高的輸出光功率(約1W)來完成四波混頻和其他非線性相互作用。邊耦合器的寬帶特性意味著可以準確測量泵浦、信號和空閑通道的相對強度(因為所有三個波長都經歷相同的插入損耗),從而可以精確計算非線性轉換效率。為防止損壞模式適配器,帶有邊耦合器的非線性應用模塊必須采用密封封裝,否則,由透鏡光纖聚焦的高光功率形成的“熱點”的電場梯度可能會產生光鑷效應,將空氣中的微粒和有機污染物吸引到模式適配器的端面,如果這些污染物吸收了相當一部分光功率,可能會由于端面的局部加熱而導致模式適配器的災難性失效。這種失效在SU-8和PMMA模式適配器中更為常見,而在集成的SiON模式適配器中則較少見,因為介電材料比聚合物光刻膠更耐受熱分解。

與光柵耦合器陣列相比,邊耦合器陣列具有更低的插損和更寬帶寬,許多研究小組和公司正在研究降低邊耦合對準公差的方案[21,22],目的是放寬對準公差或提高制造公差[23],以滿足電信和數通應用中的多通道邊耦合需求。當前MPW光柵耦合器的損耗和帶寬通常被公司和標準化機構視為光子器件商業應用的重大障礙。

2.1.2. 光柵耦合

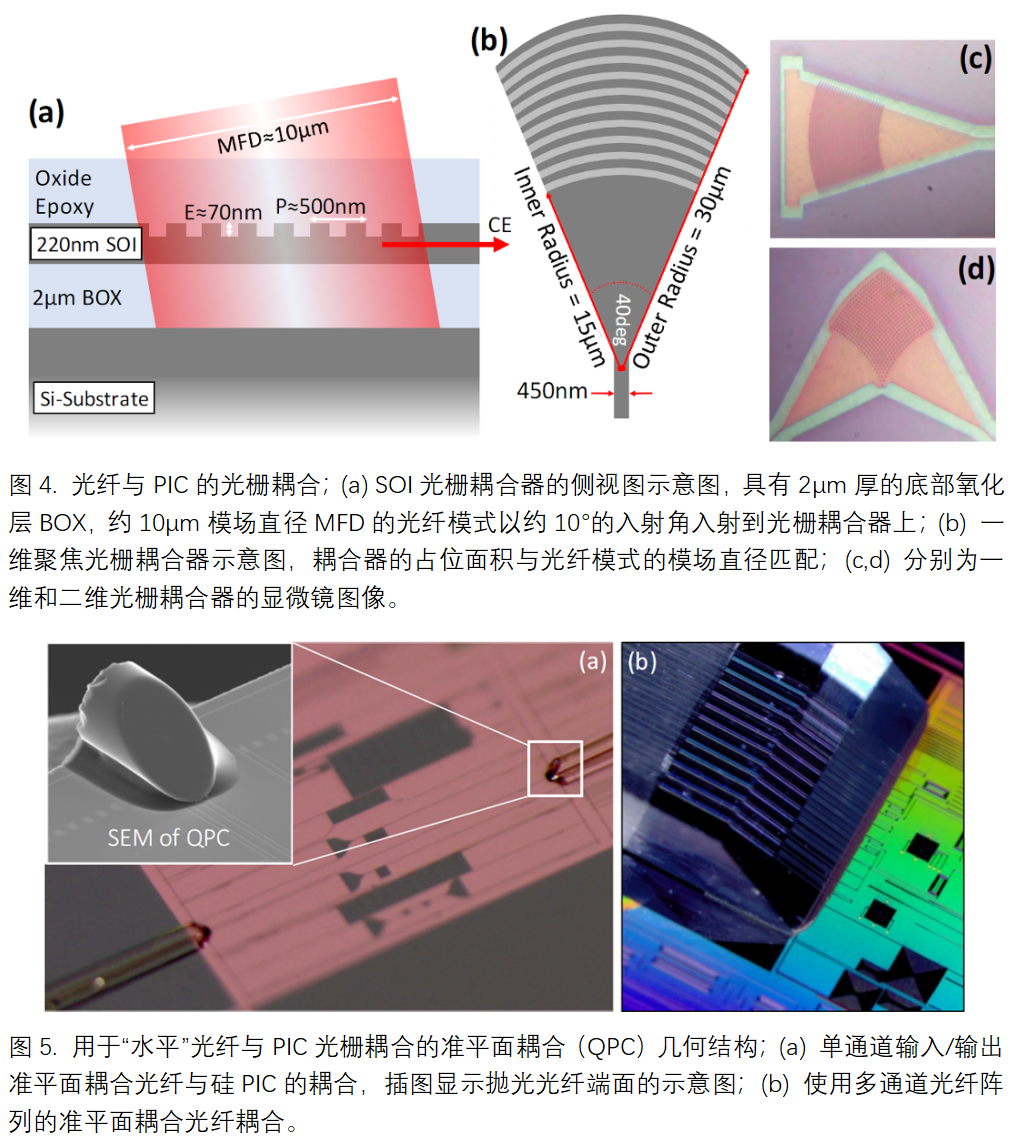

邊耦合最常見的替代方案是光柵耦合,其在PIC的波導層中光刻蝕刻亞微米周期結構,以創建相干干涉條件,將光纖模式衍射耦合到PIC波導中[24,25],見圖4。光柵耦合器大概102μm大小以在匹配標準電信光纖8-10μm的模場直徑,由約20個部分蝕刻到220nm硅層中的周期性溝槽陣列組成[12]。耦合器的峰值波長λ、溝槽間距P、光柵耦合器區域的有效折射率n?、氧化層的折射率n?和光纖模式的入射角θ之間存在簡單關系:λ=P(n??n?sinθ),其中n?的值由溝槽的蝕刻深度和占空比以及光纖模式的偏振決定。通常采用近法線入射角(θ≈10°),以向耦合模式提供方向性,并減少向光纖的背反射。然而,從封裝的角度來看,近法線入射的光纖與PIC耦合可能會導致器件體積龐大且機械性能不佳。為解決這一問題,已開發出一種用于光纖與PIC耦合的“準平面”方法,其中光纖端面被拋光至約40°,以創建全內反射條件,將光纖模式以正確的10°角導向光柵耦合器[26,27],見圖5。這種幾何結構形成了幾乎“二維”的封裝,在其中更容易滿足電信光纖的最小彎曲半徑(≈5cm),同時保持合理的器件占位面積。

光柵耦合器比邊耦合器具有更寬松的對準公差,面內±2.5μm錯位通常產生1dB的代價[13]。光柵耦合器放置位置靈活,無需放置在芯片邊緣,可以放置在PIC表面的任何位置,也不需要切割和拋光等后續工藝,使得硅PIC在封裝前就可以進行晶圓級測試和表征。盡管有這些優點,但光柵耦合的插損要高于邊耦合。好消息是,光柵耦合器設計的最新研究進展已經開始縮小這一性能差距,有報道稱在SOI平臺中,均勻和切趾光柵耦合器的插入損耗分別為1.6dB和1.2dB(測量)[28,29]。更先進但商業化較低的光柵耦合器設計(在后工藝步驟中添加金屬背反射層)可實現0.6dB的插入損耗[30],這表明先進的光柵耦合器已與邊耦合器具有相同水平的性能,并具有寬松的對準公差。

因為通信光的偏振未知且不穩定,而標準的“一維”光柵耦合器通常偏振相關,這使得它們不適合電信和數通連接。一種解決方案是二維光柵耦合器,它由兩個正交的一維光柵耦合器疊加而成,可以接收任何偏振狀態的光纖模式,并將其衍射到兩個均為TE偏振的PIC上的波導中[31]。最近關于硅光子學二維光柵耦合器優化的工作預測,帶背反射器和不帶背反射器的設計的插入損耗分別為1.0dB和2.0dB,偏振相關損耗PDL低至0.3dB[32,33]。

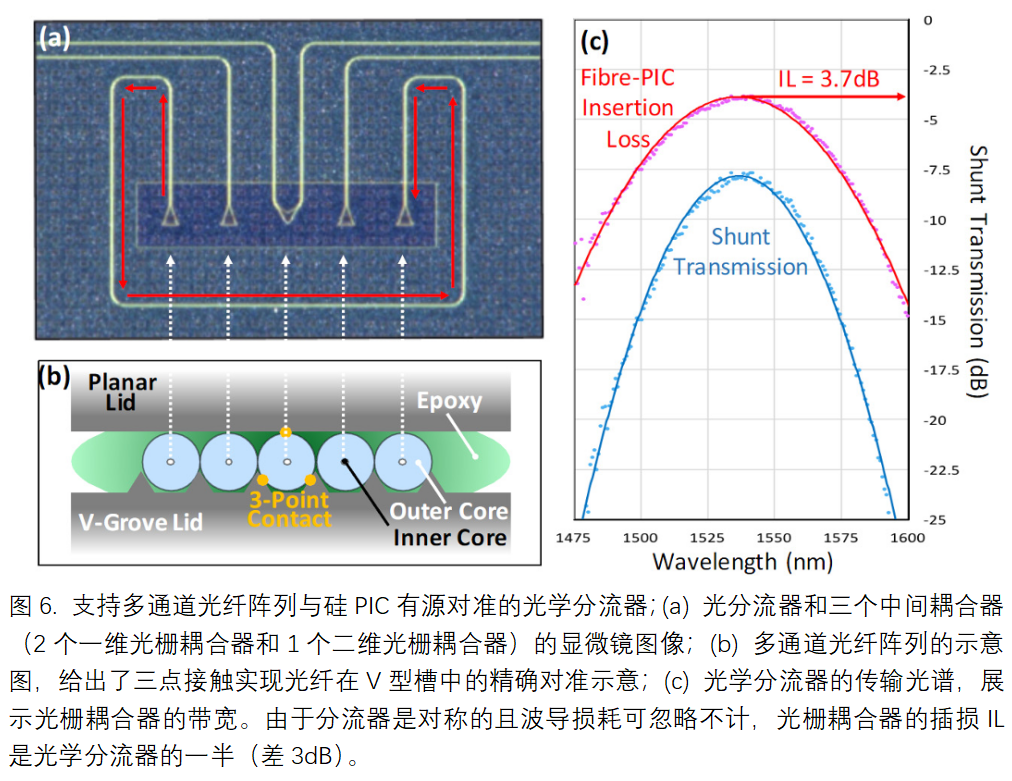

對于許多通信領域應用,通常需要將多個通道封裝到同一個PIC上,目標甚至是128和256個通道。不必單通道對準,可使用“光分流器”來同時將每個光纖與匹配的光柵耦合器對準[34]。在這種方法中,需構建一個精密光纖陣列,它使用一塊玻璃板,在玻璃板上精確蝕刻有一系列平行的V槽,間距通常為127μm或250μm,以對應標準電信光纖的直徑,還有一個平的玻璃“蓋子”,見圖6。當光纖插入V型槽通道并蓋上蓋子后,三點接觸條件確保了不同通道的精確位置和間距。這些光纖陣列中光纖內芯的標稱中心度為±0.5μm,這完全在光柵耦合器±2.5μm的1dB對準公差范圍內。因此,當第一個和最后一個光柵耦合器通過分流波導連接時,使分流傳輸最大化的光纖陣列單次有源對準也會將所有中間光纖通道相對于其光柵耦合器對準(公差為±0.5μm)。一旦完成單通道或多通道光纖與PIC的對準,就使用低收縮折射率匹配的紫外(UV)固化環氧樹脂將其固定。

盡管分流對準有助于降低光纖與PIC封裝的單通道封裝成本,但需要采用一次有源對準步驟,而實現量產封裝需要采用無源對準方案。最近有研究展示的“倒裝芯片”光纖與PIC對準方法 [35],它使用分束器系統將光纖陣列中的內芯與PIC上的匹配光柵耦合器進行視覺對準,公差為±1μm,無需有源對準。由于這在光柵耦合器的1dB對準公差范圍內,這種方法仍然具有低耦合損耗,但比有源對準至少快一個數量級。另一種無源對準方案使用大面積30μm×30μm光柵耦合器,其提供±10μm的1dB對準公差,目前也在研究中。它的主要缺點是光譜帶寬減小,這導致其不適合波分復用應用。

2.1.3. 倏逝耦合

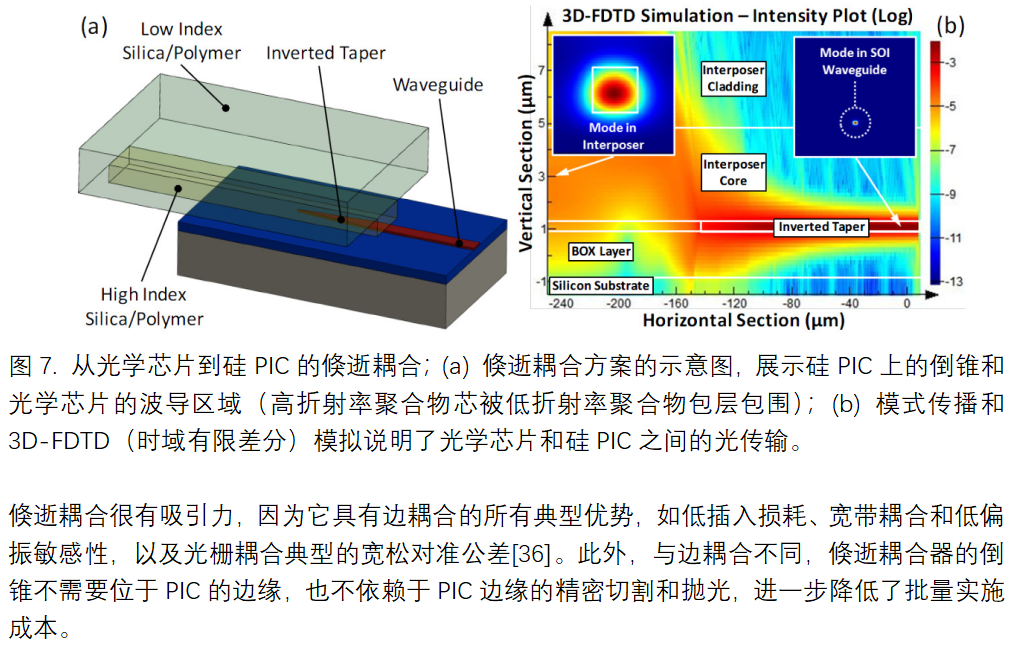

2015年,IBM-蘇黎世首次將一種稱為“倏逝耦合”的新方法應用于硅光子學 [36]。與邊耦合類似,它使用倒錐從PIC波導中高效提取模式。然而,該模式不是被PIC上的模場轉換器捕獲,而是倏逝耦合到另一個光學芯片上的第二個波導中,該光學芯片與PIC面對面非常接近,見圖7。然后,光芯片上的折射率和模場直徑可以輕松匹配標準單模光纖,從而實現兩步(光纖-芯片-PIC)耦合過程。目前,芯片與芯片的倏逝耦合僅在硅PIC和基于聚合物的光芯片之間得到證明,但沒有明顯的理由表明這種方法不能轉移到基于玻璃或SiON的光芯片上,以用于更可靠的光子器件。

2.2. 激光與PIC的集成

對于光子學中的許多傳感應用,希望在硅PIC上本地生成連續波或調制光信號。由于沒有可與CMOS單片集成的激光二極管,這要么需要(i)III-V族材料與硅PIC的異質集成;要么需要(ii)III-V族器件與硅PIC的混合集成。

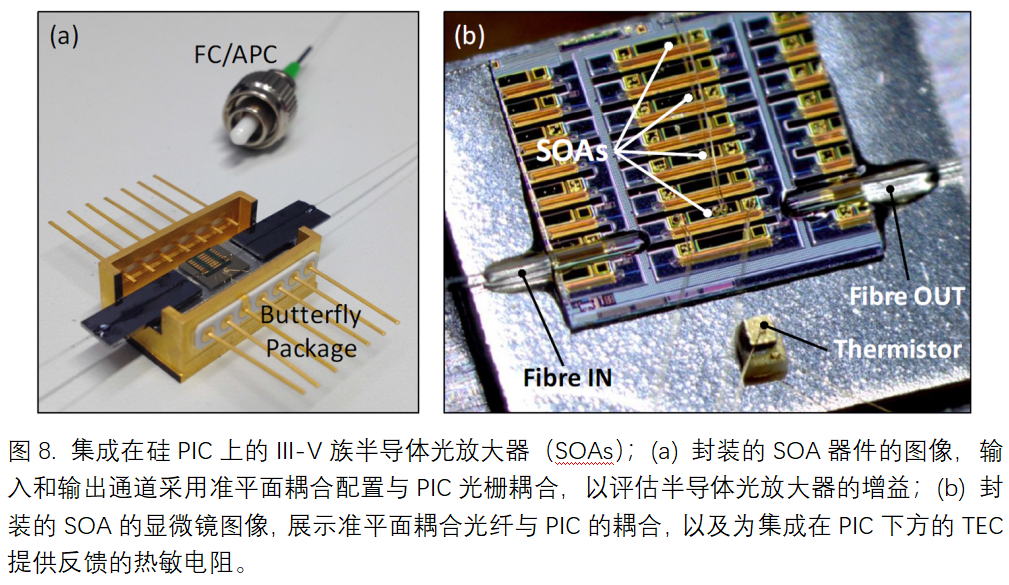

異質集成是將具有光學增益的III-V族材料鍵合到硅PIC上(直接鍵合或通過中間聚合物粘合劑層),然后蝕刻材料以創建激光腔條件。根據應用的不同,腔可以通過兩個蝕刻端面、兩個布拉格反射器,或者使用微環來形成[37,38]。產生的激光發射隨后倏逝耦合到PIC上的波導中。異質集成可以被視為一種后處理步驟,而不是光子封裝,通常用于制造半導體放大器(SOAs),其提供光增益以抵消硅PIC上的插損和波導損耗[39],見圖8。這些集成的半導體光放大器的光增益具有強的熱依賴性,需要溫度穩定以實現穩定的性能。

混合集成涉及將光從分立的III-V族激光器件耦合到硅PIC上,要么直接耦合,要么通過微光機電(μOEM)平臺。混合集成方案的集成密度往往低于異質集成方案,但具有使用“已知優良器件”的優勢,具有更高的良率和更好的性能分布。兩種很有前景的混合集成方案是微光學平臺和直接VCSEL集成。

2.2.1. 微光學平臺

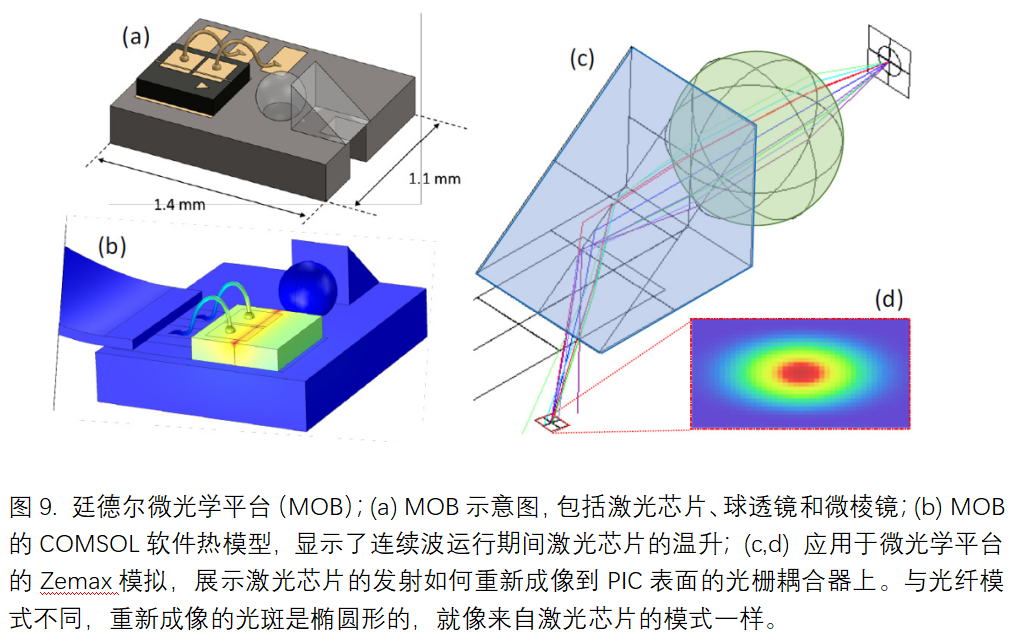

Luxtera和廷德爾國家研究所都展示了微光學平臺(MOB)[40,41]。這些微光學平臺由AlN或Si底座組成,其上安裝有邊發射激光芯片、用于準直和聚焦的球透鏡以及用于光束轉向的反射鏡(或全內反射元件),見圖9。密封的Luxtera微光學平臺還包括一個微光學隔離器,以減少對激光芯片的反饋。微光學平臺的功能是將來自邊緣發射激光的光重新成像到PIC表面的光柵耦合器上,具有所需的近法線入射角。可以使用PIC上的標準一維光柵耦合器,但為更好地匹配來自微光學平臺的橢圓光斑而設計的定制光柵耦合器具有更低的插損。

在廷德爾微光學平臺中,300μm的球透鏡在精密激光鉆孔中自對準,然后為微棱鏡反射元件的對準和安裝提供固定參考點。微光學平臺的總面積約為1×1mm,激光芯片、微透鏡和微棱鏡的單個元件的最大尺寸為300μm。組裝完成后,微光學平臺相對于硅PIC上的光柵耦合器進行有源對準,1dB對準公差與光纖與PIC耦合相當(±2.5μm)。如果沒有足夠的散熱,微光學平臺上的激光芯片可能會過熱,導致性能下降或燒毀。微光學平臺與PIC以及TEC之間良好的熱接觸對于微光學平臺的穩定運行是必要的[42]。

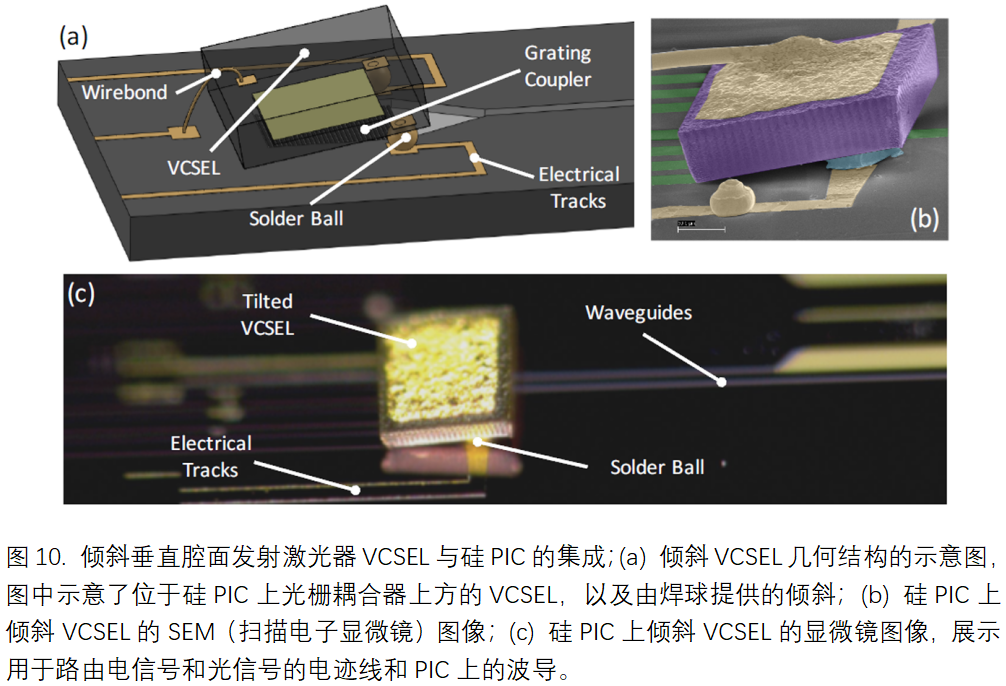

2.2.2. 垂直腔面發射激光器集成

垂直腔面發射激光器(VCSELs)的直接集成也是混合集成的一種很有前景的途徑。與微光學平臺(1×1mm)相比,VCSEL芯片(250×250μm)的占位面積顯著減小,可以實現非常高的集成度。已有采用平面VCSEL與PIC的集成方案,其中基于光刻膠的“楔形物”用于將VCSEL模式折射到光柵耦合器上,具有所需的近法線入射角[43]。或者,可以設計光柵耦合器將垂直腔面發射激光器模式耦合到一對相對的波導中,在相位補償后可以將其重新組合到單個通道中[44]。還可以使用傾斜垂直腔面發射激光器方法,其中垂直腔面發射激光器通過不對稱分布的焊球直接倒裝到PIC上[45],見圖10。通過控制可用于焊料潤濕的鍵合焊盤的接觸面積,可以優化垂直腔面發射激光器的傾斜角度。這種傾斜垂直腔面發射激光器方法允許與PIC的倒裝芯片無源對準,以實現商業化量產快速組裝。

3. 電封裝

對于電信和數通應用,光子器件需要高速且超高帶寬地運行。這通常需要將多個25Gbps電通道多路復用/解復用為單N×25Gbps光通道,其中N=4、6、12等。需要將這些高速電信號從厘米級SMA(超小型A版)/SMK(超小型K版)連接器高效、低反射、無偽影地路由到PIC上的微觀結構。如果需要與PIC進行大量電連接,或者需要在多個通道上進行精確(亞納秒)的開關控制,還需要EIC驅動芯片的垂直集成。

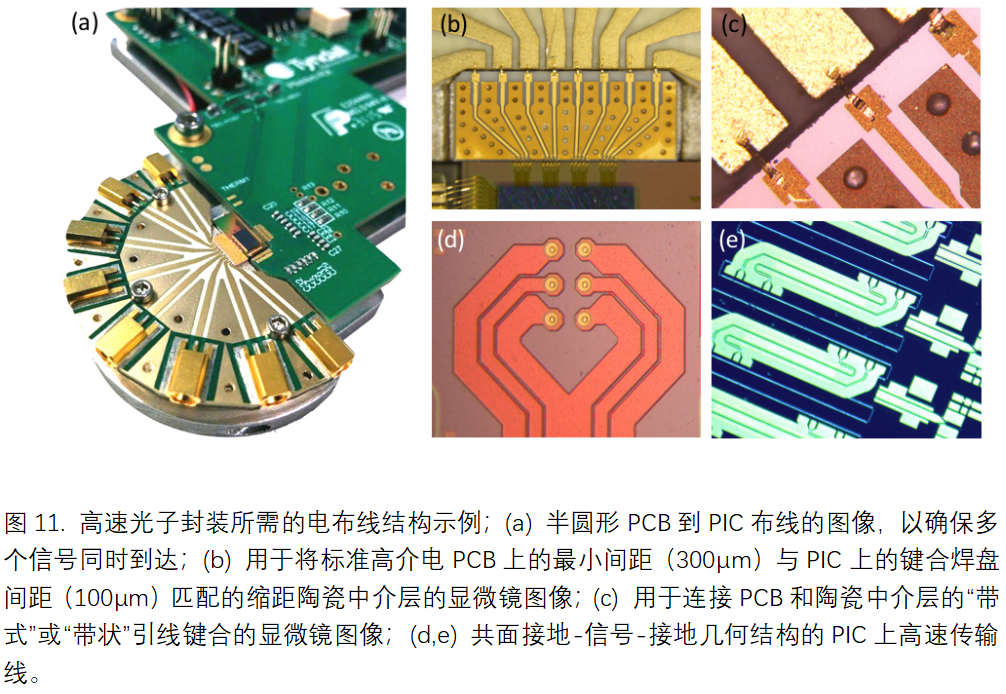

3.1. 高速布線

高速SMA(18-25GHz)和SMK(46GHz)連接器在PCB上的面積約為1cm2,而PIC上電鍵合焊盤的間距通常為100μm。因此,高速50Ω傳輸線的間距必須在連接器和PIC之間減小兩個數量級,同時需控制不同通道的路徑長度以保持信號時序。這通常導致PIC被圓形或半圓形PCB包圍,其面積與電通道數量的平方成正比,見圖11。

在標準高介電(D?≈10)PCB上,最小特征尺寸將50Ω傳輸線的間距限制在約300μm,這比PIC上的鍵合焊盤間距大3倍。這個“差距”可以通過使用基于有限元模式(FEM)高頻結構模擬器(HFSS)設計的縮距多層陶瓷中介層來彌合。與PCB相比,中介層提供更小的特征尺寸和更高的制造公差。中介層與PIC上的鍵合焊盤之間的電連接使用10-20μm直徑的金線鍵合實現。對于直流(DC)連接,使用圓形橫截面的引線鍵合,但對于高速連接,“帶狀”或“帶式”引線鍵合具有更高的單位體積表面積,由于趨膚效應,對高速信號的電阻更低。

為減少感應效應,所有引線鍵合應盡可能短且直。這通常意味著PIC應嵌入到PCB中,以實現“齊平”引線鍵合。一旦連接到PIC,引線鍵合對任何剪切力都非常敏感,因此PIC、中介層和PCB必須在機械封裝中剛性連接。引線鍵合的“滴膠”封裝(使用硅樹脂或環氧樹脂)可以提供進一步的保護,但只能用于不會干擾光纖與PIC耦合或其他集成元件的封裝中。

一旦傳輸到PIC,高速信號必須從鍵合焊盤路由到/來自相關的PIC上元件。盡管PCB和中介層上可以采用不同的橫截面幾何結構(微帶、帶狀線和共面傳輸線),但硅晶圓廠的設計規則通常將高速傳輸線限制為共面幾何結構。為避免顯著的損耗和反射,必須使用HFSS在硅晶圓廠可用的特定材料和層厚度的邊界條件內優化這些PIC上的傳輸線[6-8]。

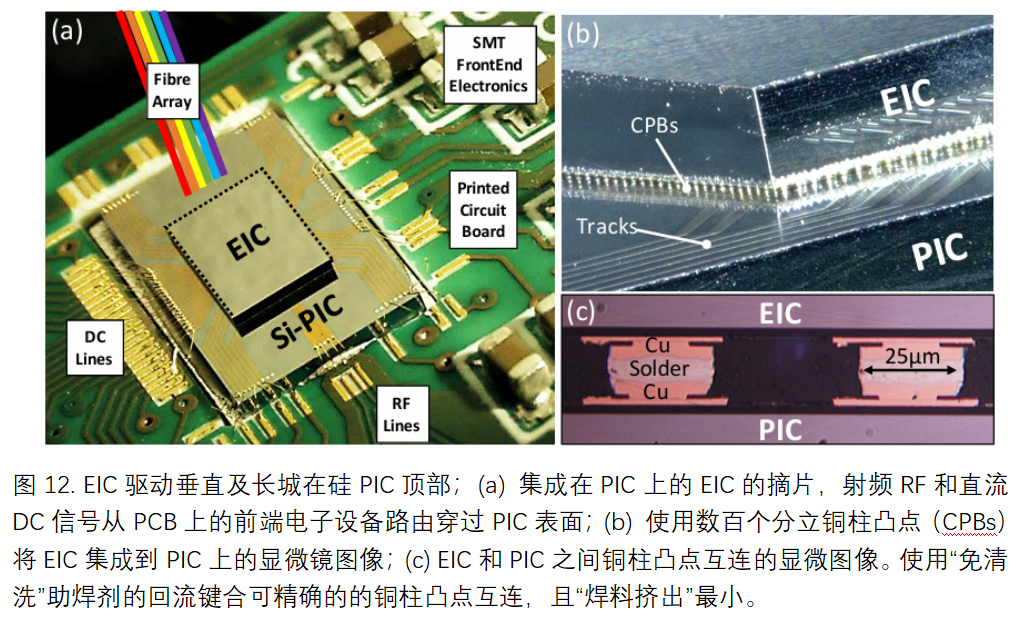

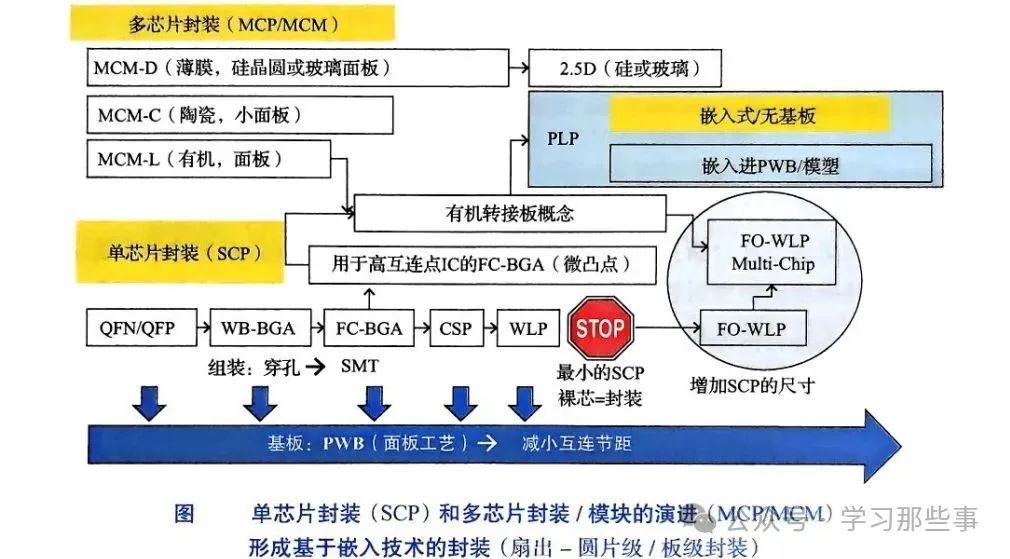

3.2. 垂直集成

將光子和電子功能單片集成到單個芯片上通常是大規模硅光子學的最終目標[4]。然而,在中低產量(每年10?-10?個芯片)下,將電子和光子功能垂直集成到兩個單獨的硅芯片上可以帶來經濟優勢,因為可以采用不同的CMOS制程。具體而言,PIC的制造公差可以使用功能45nm制程在相對低成本的200mm晶圓上完成,而高性價比的EIC可能需要300mm晶圓上的14nm制程上進行。PIC的面積(10-30mm2)通常比典型的EIC大得多,因為有大型光子元件(AWGs、延遲線等)以及為光纖與PIC耦合預留的空間,因此不在更昂貴的CMOS制程上“浪費”這部分空間可以顯著降低總體成本。

EIC與PIC的垂直集成可以使用焊球凸點(SBBs)或銅柱凸點(CPBs)互連實現,這些互連提供兩個芯片之間的電機熱接口[46,47]。特別是,垂直集成改善了與PIC的高速電子接口,它使用短的(≈10μm)凸點互連取代了長的(100-500μm)可能彎曲的引線鍵合,從而最大限度地減少了寄生感應效應[48-50],見圖12。除了高速、高密度電子集成外,焊球凸點和銅柱凸點提供的機械連接還允許橋接不同的功能技術,如MEMS(微機電系統)、III-V族、非CMOS ASIC(專用集成電路)等[3]。

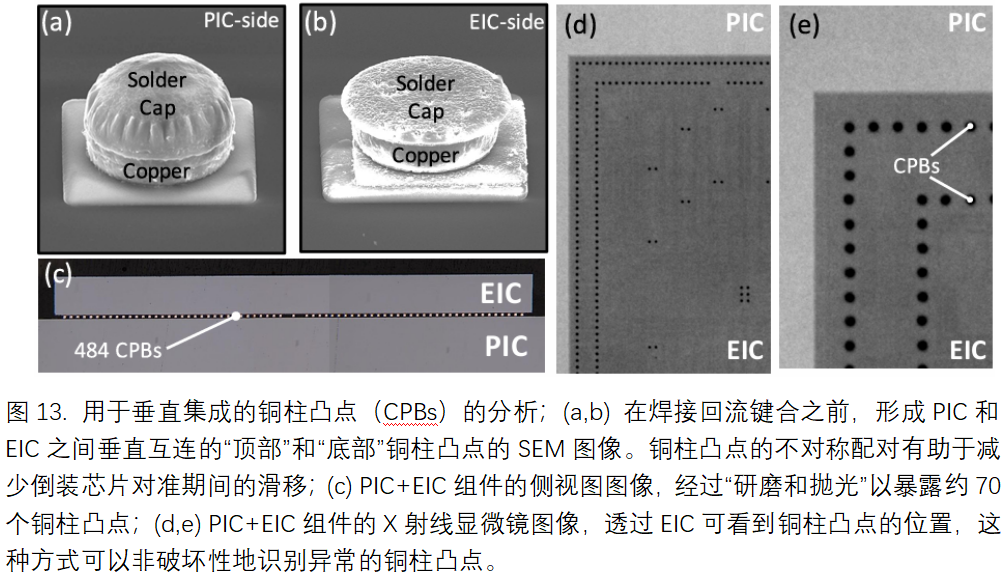

銅柱凸點的直徑通常為20-30μm,通過在PIC和EIC上的凸點下金屬焊盤上電鍍銅,然后沉積(無鉛)Sn-Ag-Cu焊料帽形成。通過使用倒裝芯片系統的分束器相機對準兩個芯片上的匹配銅柱凸點對;使兩個芯片接觸;然后應用熱壓焊或回流焊將成對的焊料帽融合在一起,實現PIC和EIC的垂直集成。這些焊料帽將被原生氧化層覆蓋,必須去除以確保形成良好的電和機械互連[51]。電封裝中使用的傳統焊料通常不適用于光子封裝,因為它們會留下化學殘留物,污染光纖與PIC耦合的光學界面,這會導致插損增加,還會削弱光纖與PIC鍵合的機械強度。相反,在回流焊過程中應使用“免清洗”助焊劑。這種助焊劑不含揮發性有機化合物VOC,在焊料的熔點下活化并蒸發[52],因此不需要可能污染PIC的鍵合后溶劑沖洗[53,54]。

在倒裝芯片系統中對準EIC和PIC,并應用“免清洗”助焊劑焊接回流周期(通常為250°C,30s)后,可以在頂部和底部銅柱凸點之間實現出色的鍵合。可以使用多種診斷方法——電阻測量、破壞性剝離測試和X射線顯微鏡——來評估銅柱凸點互連的質量。可以實現優于±1μm的對準,并幾乎沒有“焊料擠出”(這可能導致相鄰互連之間的電短路),見圖13。

4. PIC的熱管理

光子元件,如半導體光放大器(SOAs)和微環諧振器,具有強烈的溫度依賴性。20°C的溫度變化通常足以使PIC偏離其工作范圍[55,56]。光子器件中PIC的全局熱穩定(通常使用TEC)對于需要在現場測試的樣機至關重要,因為現場的季節性溫度波動通常為±10°C。TEC提供的額外全局穩定性有助于更高效且更可重復地對PIC上的單個光子元件(如微環諧振器、熱光移相器等)進行局部溫度調諧。提高這些模塊中TEC的性能系數(CoP)是降低已部署光子學運營成本的重要考慮因素。

圖14展示了帶有PIC和EIC的模塊的典型熱力圖。電功率輸送到EIC,通過焦耳加熱轉化為熱功率(H=dQ/dt),然后通過焊球凸點或銅柱凸點互連層流入PIC。從那里,熱量傳導到散熱板,并繼續傳導到TEC的“冷端”,再傳導導模塊的底板,最后通過被動對流/傳導或“機架式”強制對流冷卻將熱量散發到周圍環境中。

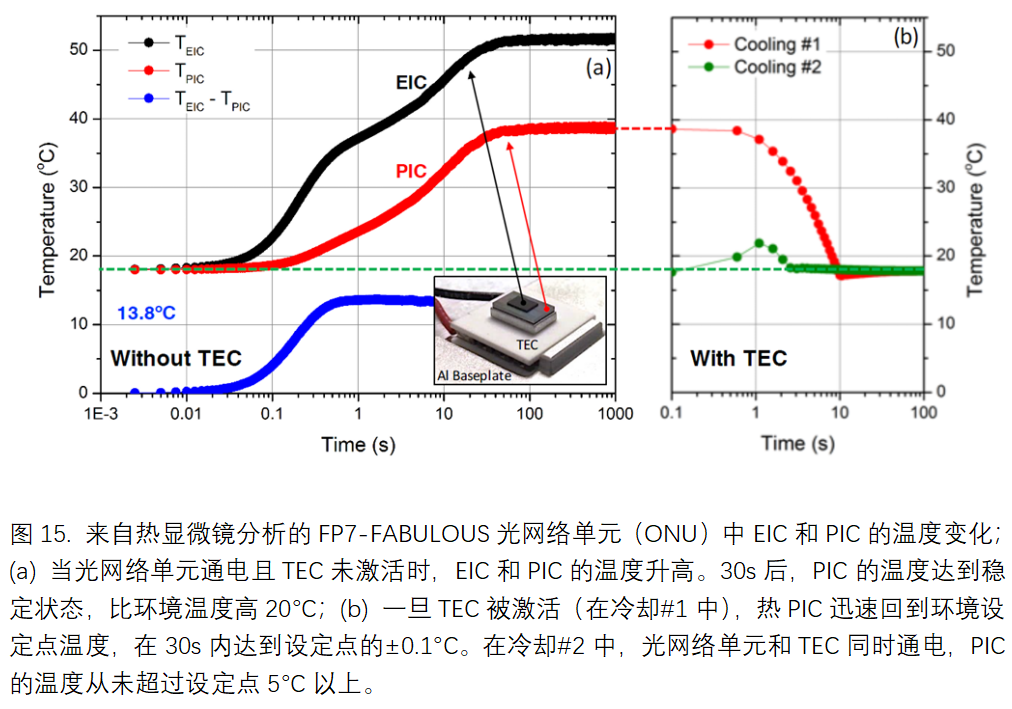

未受控制的焦耳熱的影響可以通過在TEC斷電時給EIC通電來說明,如圖15所示。在為歐盟FP7“FABULOUS”項目開發的硅光子光網絡單元(ONU)中,我們向EIC施加1.1W的功率,導致EIC和PIC的溫度分別升高34°C和20°C[57]。我們使用熱顯微鏡進行測量,該顯微鏡允許對PIC(100μm尺度)和整個光子模塊(10cm尺度)進行精確的非接觸溫度測量。這些動態溫度測量提供了關于熱堆疊的熱傳導和熱容量的定量信息。大致而言,這些動態測量中的“拐點”對應于熱量“填充”堆疊中不同材料塊所需的時間。EIC和PIC之間的穩態溫差(ΔT=13.8°C)還可以對銅柱凸點互連層熱阻(R?)進行直接測量,即R?=ΔT/H。整個銅柱凸點層的熱阻為12.5K/W=13.2°C/1.1W,而互連層由484個銅柱凸點組成,進而得到每個互連的電阻為6.1×103K/W。通過熱顯微鏡測量的動態和穩態信息可用于驗證當前的熱模型,并優化未來的設計。

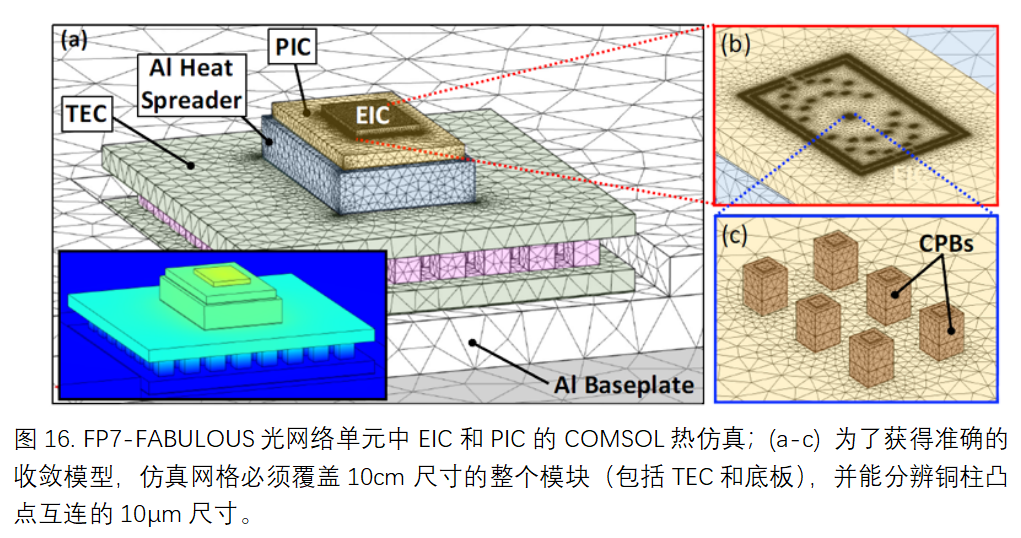

一旦TEC開啟,PIC迅速穩定到外部PID控制器設置的溫度(T??)。在靠近PIC的熱源附近放置一個微珠或SMT熱敏電阻,以向PID控制器提供熱監控反饋。對于來自“FABULOUS”項目的光網絡單元,PIC在30s內穩定到T??±0.1°C,在60s內穩定到T??±0.01°C。在這種穩態下,當向EIC施加1.1W的電功率時,TEC需要消耗0.5W才能使PIC恢復到18°C的室溫設定點,性能系數為2.2=1.1W/0.5W,并表明熱管理占模塊運行功率預算的30%= 0.5W/(0.5+1.1W)。通過改善模塊內熱量的分布和消散來提高PIC熱電冷卻的性能系數是一個活躍的研究課題。COMSOL中的有限元模擬可用于測試和優化新的堆疊設計,然后使用來自熱顯微鏡的動態溫度測量進行實驗驗證,見圖16。

5. 光子封裝的新興技術

除了前幾節描述的成熟技術外,已出現很多新興技術,可能在將來會對光子封裝技術產生重要的影響。

倏逝耦合的相同聚合物波導技術可以與電FR4(阻燃4級)PCB結合,創建一個能夠將電信號和光信號從外部連接器路由到單個或多個硅PIC的平臺[36]。與玻璃中介層相比,其主要優勢是聚合物波導的成本優勢和加工靈活性(即直接激光寫入或光刻),特別是對于大面積情況,這些“光PCB”的預期傳播距離在幾十厘米范圍內,因此需要克服的主要挑戰是將波導傳播損耗降低到0.1dB/cm以下。

卡爾斯魯厄理工學院開發的光子引線鍵合(PWBs)為PIC與PIC[58]和多芯光纖與PIC[59]的光學連接提供了一種新的解決方案。這些PWB通過密集的聚焦的飛秒激光脈沖沿著連接兩個光學界面(例如硅PIC上的倒錐與單模光纖的內芯)的自由3D路徑曝光光刻膠。光子線鍵合的形狀可以輕松調整,因此不需要在連接的PIC和光纖之間進行高精度機械對準,這對于未來的規模化是一個優勢。目前,寫入PWB還是串行方式,未來能否在晶圓級低成本的實施(每個晶圓需要數千或數萬個光子線鍵合)還有待觀察。

在光柵耦合器設計方面也有許多創新,包括用亞波長光刻特征取代單線溝槽,這可以采用高水平的折射率工程。在某些情況下,這些亞波長特征被設計為切趾結構,幾乎完美地匹配入射光纖模式的輪廓[60],具有非常低(<1dB)的插損。另一種策略是使用亞波長光刻特征在SOI(絕緣體上硅)層中創建具有高度非線性圖案的區域,形成一塊超材料[61]。當這種超材料中的圖案經過適當優化后,它可以將光從自由空間耦合到SOI波導中,甚至可以耦合不同偏振的光,類似二維光柵耦合器。這些超材料耦合器的效率至少與更標準的光柵耦合器相當,并且可以提供更寬的帶寬,因為多個導模負責耦合,這使得超材料耦合器對波長偏移不太敏感。這兩種亞波長耦合器方案的主要缺點是,它們通常只能通過電子束光刻制造,因為它們需要約100nm量級的特征尺寸,而硅光子晶圓廠通常使用的193nm深紫外光刻難以加工這些尺寸。在這些亞波長耦合器能夠使用到可擴展的紫外光刻工藝之前,它們很難成為商用光子器件的標準化構件。

除了光纖與PIC的耦合外,光柵耦合器還可用于光學接近耦合或層間耦合[62-64],這允許高效的垂直芯片與芯片甚至板與芯片連接(結合上述光學PCB)。結合用于水平分布的低損耗波導,這種垂直芯片與芯片的光學連接使光能夠在光學母板上進行3D集成路由到多個硅PIC。盡管光纖與PIC光柵耦合器的帶寬通常相當窄(通常1dB帶寬為30-40nm),但在光接近中,因為光柵之間的近場相互作用,同樣的光柵將提供寬帶耦合。同樣的原因,兩個相鄰光柵耦合器之間的插損不僅僅是兩個等效光纖與PIC界面的總和,它可以低得多,與單個光纖與PIC的量級相同。這些光學接近耦合器有望對晶圓級封裝產生重大影響,因為它們允許不同光子系統的倒裝芯片對準和/或晶圓鍵合,以用于先進的混合光子器件。

6. 光子封裝趨勢討論

光子封裝的高成本和低速度是開發具有競爭力的光子器件最顯著的瓶頸。隨著衍生公司努力將器件推向市場,以及大型跨國公司進入硅光子學領域,開發自動化封裝工藝以實現更高產量的生產需求日益增長。明顯的趨勢是更緊湊的光子設計,更低的插入損耗、更高的集成度(電學和MEMS)、可擴展到多個25Gbps通道,以及高效(理想情況下被動)的熱穩定性。為應對這一挑戰,光子封裝研究人員正從傳統的個性化定制樣機轉向開發標準化和可擴展的解決方案。雖然光纖與PIC無源對準、更精確的倒裝芯片垂直集成和更好的熱堆疊設計等技術創新都發揮著重要作用,但“軟”發展(如封裝標準的發布和采用,以及材料和組件供應鏈的增長和整合)同樣重要。

在硅光子學界,為光子封裝創建標準化設計規則和標準的需求正逐漸得到認可。這種轉變的驅動力是減輕研究人員/工程師的特定應用設計負擔,并簡化從設計到器件的流程。光子封裝小組現在正與行業合作伙伴合作,建立封裝設計套件(PDKs)和規則(PDRs),以支持非專業用戶開發與最佳實踐光子封裝兼容的硅PIC。這有助于新用戶避免問題,并避免昂貴且耗時的PIC重新設計。新用戶經常忽視的重要封裝設計規則包括:(i) 硅PIC上光柵耦合器陣列的間距(應與光纖通道的尺寸匹配,即127μm或250μm);(ii) 電鍵合焊盤的最小間距對于直流連接應>100μm(以最大化引線鍵合的良率),對于射頻連接應>300μm(以消除對昂貴的陶瓷縮距中介層的需求);以及(iii) 光柵耦合器陣列周圍需要一個“禁區”,其中不放置任何電連接或相位敏感組件,以防環氧樹脂溢出。盡管目前處于發展的早期階段,但預計這些封裝設計規則將隨著時間的推移得到擴展和正式化,并納入硅晶圓廠的設計規則檢查(DRC)中。簡單的光子封裝設計套件已經在PhoeniX BV(OptoDesigner)和Luceda(IPKISS)的PIC設計工具中在軟件層面實現[65,66]。

7. 結論

光子封裝是實現用于小規模樣機制作和商業量產的高集成度硅光子器件的關鍵步驟。光子器件的封裝通常是整個模塊制造中最昂貴的部分,并且可能需要在PIC設計階段關注。同時滿足PIC的光學、電學和熱學設計考慮因素需要一種“綜合”方法,遠遠超出最廣為人知的光纖與PIC耦合問題。封裝研究人員越來越多地使用先進的設計工具和不斷發展的封裝設備來應對這些挑戰。隨著光子器件和技術走出實驗室并進入市場,光子封裝也在不斷成熟以跟上步伐,其重點正從測試和樣機制作轉向標準化和可擴展的商業實施。

參考文獻

1. Streshinsky, M.; Ding, R.; Liu, Y.; Novack, A.; Galland, C.; Lim, A.; Guo-Qiang, P.L.; Baehr-Jones, T.;Hochberg, M. The road to affordable, large-scale silicon photonics. Opt. Photon. News 2013, 24, 32–39.

2. Soref, R. The past, present, and future of silicon photonics. IEEE J. Sel. Top. Quantum Electron. 2006, 12,1678–1687.

3. Arakawa, Y.; Nakamura, T.; Urino, Y.; Fujita, T. Silicon photonics for next generation system integration platform. IEEE Commun. Mag. 2013, 51, 72–77.

4. Tsybeskov, L.; Lockwood, D.J.; Ichikawa, M. Silicon photonics: CMOS going optical [Scanning the Issue]. Proc. IEEE 2009, 97, 1161–1165.

5. Sun, C.; Wade, M.T.; Lee, Y.; Orcutt, J.S.; Alloatti, L.; Georgas, M.S.; Waterman, A.S.; Shainline, J.M.; Avizienis, R.R.; Lin, S.; et al. Single-chip microprocessor that communicates directly using light. Nature 2015, 528, 534–538. [PubMed]

6. Integrated Silicon Photonics ICs with MPW Service. Available online: http://www2.imec.be/be_en/services-and-solutions/silicon-photonics.html (accessed on 15 October 2016).

7. CEA-LETI Full Platform in MPW. Available online: http://www-leti.cea.fr/en/How-to-collaborate/Focuson-Technologies/Integrated-silicon-photonics (accessed on 15 October 2016).

8. Silicon Photonics Multiple-ProjectsWafer. Available online: http://www.a-star.edu.sg/ime/SERVICES/silicon_photonics_multi-projects-wafer.aspx (accessed on 1 December 2016).

9. Zimmermann, L.; Preve, G.B.; Tekin, T.; Rosin, T.; Landles, K. Packaging and assembly for integrated photonics—Review of the ePIXpack photonics packaging platform. IEEE J. Sel. Top. Quantum Electron. 2011,17, 645–651.

10. Kopp, C.; Bernabé, S.; Bakir, B.B.; Fedeli, J.-M.; Orobtchouk, R.; Schrank, F.; Porte, H.; Zimmermann, L.;Tekin, T. Silicon photonic circuits: On-CMOS integration, fiber optical coupling, and packaging. IEEE J. Sel.Top. Quantum Electron. 2011, 17, 498–509.

11. O’Brien, P.; Carroll, L.; Eason, C.; Lee, J.-S. Packaging of Silicon Photonic Devices. In Silicon Photonics III; Pavesi, L., Lockwood, D.J., Eds.; Springer: Berlin/Heidelberg, Germany, 2016; Volume 122, pp. 217–236.

12. Lee, J.-S.; Carroll, L.; Scarcella, C.; Pavarelli, N.; Menezo, S.; Bernabe, S.; Temporiti, E.; O’Brien, P. Meeting the electrical, optical, and thermal design challenges of photonic-packaging. IEEE J. Sel. Top. Quantum Electron.2016, 22.

13. Taillaert, D.; Van Laere, F.; Ayre, M.; Bogaerts, W.; Van Thourhout, D.; Bienstman, P.; Baets, R. Grating couplers for coupling between optical fibers and nanophotonic wave-guides. Jpn. J. Appl. Phys. 2006, 45, 6071–6077.

14. Taillaert, D.; Chong, H.; Borel, P.I.; Frandsen, L.H.; De La Rue, R.M.; Baets, R. A compact two-dimensional grating coupler used as a polarization splitter. IEEE Photonics Technol. Lett. 2003, 15, 1249–1251.

15. Fukuda, H.; Yamada, K.; Tsuchizawa, T.; Watanabe, T.; Shinojima, H.; Itabashi, S. Silicon photonic circuit with polarization diversity. Opt. Express 2008, 16, 4872–4880. [PubMed]

16. Song, J.; Fernando, H.; Roycroft, B.; Corbett, B.; Peters, F. Practical Design of Lensed Fibers for Semiconductor Laser Packaging Using Laser Welding Technique. J. Lightwave Technol. 2009, 27, 1533–1539.

17. McNab, S.; Moll, N.; Vlasov, Y. Ultra-low loss photonic integrated circuit with membrane-type photonic crystal waveguides. Opt. Express 2003, 11, 2927–2939. [PubMed]

18. Shoji, T.; Tsuchizawa, T.;Watanabe, T.; Yamada, K.; Morita, H. Low loss mode size converter from 0.3 _m square Si wire waveguides to singlemode fibers. Electron. Lett. 2002, 38, 1669–1670.

19. Pu, M.; Liu, L.; Ou, H.; Yvind, K.; Hvam, J.M. Ultra-low-loss inverted taper coupler for silicon-on-insulator ridge waveguide. Opt. Commun. 2010, 283, 3678–3682.

20. Galán, J.; Sanchis, P.; Sánchez, G.; Martí, J. Polarization insensitive low-loss coupling technique between SOI waveguides and high mode field diameter single-mode fibers. Opt. Express 2007, 15, 7058–7065. [PubMed]

21. Romero-Garc?a, S.; Marzban, B.; Merget, F.; Shen, B.; Witzens, J. Edge couplers with relaxed alignment tolerance for pick-and-place hybrid integration of III–V lasers with SOI waveguides. IEEE J. Sel. Top. Quantum Electron. 2014, 20. Appl. Sci. 2016, 6, 426 19 of 21

22. Papes, M.; Cheben, P.; Ye, W.N.; Schmid, J.H.; Xu, D.X.; Janz, S.; Benedikovic, D.; Ramos, C.A.; Halir, R.; Ortega-Mo?ux, A.; et al. Fiber-chip edge coupler with large mode size for silicon photonic wire waveguides. In Proceedings of the SPIE (9516), Integrated Optics: Physics and Simulations II (95160K), Prague, Czech Republic, 1 May 2015.

23. Solutions for Si-Photonics Connection. Available online: http://www.teemphotonics.com/ioc/offer-andproducts/solutions-for-si-photonics-connection.html (accessed on 15 October 2016).

24. Van Laere, F.; Claes, T.; Schrauwen, J.; Scheerlinck, S.; Bogaerts, W.; Taillaert, D.; O’Faolain, L.; Van Thourhout, D.; Baets, R. Compact focusing grating couplers for silicon-on-insulator integrated circuits. IEEE Photonics Technol. Lett. 2007, 19, 1919–1921.

25. Roelkens, G.; Vermeulen, D.; Selvaraja, S.; Halir, R.; Bogaerts,W.; Van Thourhout, D. Grating-based optical fiber interfaces for silicon-on-insulator photonic integrated circuits. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 571–580.

26. Snyder, B.; O’Brien, P. Planar fiber packaging method for silicon photonic integrated circuits. In Proceedings of the Optical Fiber Communication Conference, Optical Society of America (OM2E.5), Los Angeles, CA, USA, 4–8 March 2012.

27. Li, C.; Chee, K.; Tao, J.; Zhang, H.; Yu, M.; Lo, G. Silicon photonics packaging with lateral fiber coupling to apodized grating coupler embedded circuit. Opt. Express 2014, 22, 24235–24240. [PubMed]

28. Vermeulen, D.; Selvaraja, S.; Verheyen, P.; Lepage, G.; Bogaerts, W.; Absil, P.; Van Thourhout, D.; Roelkens, G. High-efficiency fiber-to-chip grating couplers realized using an advanced CMOS-compatible Silicon-On-Insulator platform. Opt. Express 2010, 18, 18278–18283. [PubMed]

29. Xia, C.; Chao Li, L.; Fung, C.K.Y.; Lo, S.M.G.; Tsang, H.K. Apodized waveguide grating couplers for efficient coupling to optical fibers. IEEE Photonics Technol. Lett. 2010, 22, 1156–1158.

30. Zaoui, W.S.; Kunze, A.; Vogel, W.; Berroth, M.; Butschke, J.; Letzkus, F.; Burghartz, J. Bridging the gap between optical fibers and silicon photonic integrated circuits. Opt. Express 2014, 22, 1277–1286. [PubMed]

31. Pathak, S.; Vanslembrouck, M.; Dumon, P.; Van Thourhout, D.; Bogaerts,W. Compact SOI-based polarization diversity wavelength de-multiplexer circuit using two symmetric AWGs. Opt. Express 2012, 20, B493–B500. [PubMed]

32. Carroll, L.; Gerace, D.; Cristiani, I.; Menezo, S.; Andreani, L. Broad parameter optimization of polarization-diversity 2D grating couplers for silicon photonics. Opt. Express 2013, 21, 21556–21568. [PubMed]

33. Carroll, L.; Gerace, D.; Cristiani, I.; Andreani, L. Optimizing polarization-diversity couplers for Si-photonics: reaching the ??1 dB coupling efficiency threshold. Opt. Express 2014, 22, 14769–14781. [PubMed]

34. Snyder, B.; O’Brien, P. Packaging process for grating-coupled silicon photonic wave-guides using angle-polished fibers. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 954–959.

35. Pavarelli, N.; Lee, J.-S.; Rensing, M.; Scarcella, C.; Zhou, S.; Ossieur, P.; O’Brien, P. Optical and Electronic Packaging Processes for Silicon Photonic Systems. J. Lightwave Technol. 2015, 33, 991–997.

36. Dangel, R.; Hofrichter, J.; Horst, F.; Jubin, D.; La Porta, A.; Meier, N.; Soganci, I.; Weiss, J.; Offrein, B. Polymer waveguides for electro-optical integration in data centers and high-performance computers. Opt. Express 2015, 23, 4736–4750. [PubMed]

37. Van Campenhout, J.; Rojo Romeo, P.; Regreny, P.; Seassal, C.; Van Thourhout, D.; Verstuyft, S.; Di Cioccio, L.; Fedeli, J.; Lagahe, C.; Baets, R. Electrically pumped in P-based microdisk lasers integrated with a nanophotonic silicon-on-insulator waveguide circuit. Opt. Express 2007, 15, 6744–6749. [PubMed]

38. Keyvaninia, S.; Roelkens, G.; Van Thourhout, D.; Jany, C.; Lamponi, M.; Le Liepvre, A.; Lelarge, F.; Make, D.; Duan, G.; Bordel, D.; et al. Demonstration of a heterogeneously integrated III-V/SOI single wavelength tunable laser. Opt. Express 2013, 21, 3784–3792. [PubMed]

39. Park, H.; Fang, A.W.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. A Hybrid Al-Gainas-Silicon evanescent amplifier. IEEE Photonics Technol. Lett. 2007, 19, 230–232.

40. Mack, M.; Peterson, M.; Gloeckner, S.; Narasimha, A.; Koumans, R.; De Dobbelaere, P. Method and System for a Light Source Assembly Supporting Direct Coupling to an Integrated Circuit. US Patent 8,168,939 B2, 1 May 2012. Appl. Sci. 2016, 6, 426 20 of 21

41. Snyder, B.; Corbett, B.; O’Brien, P. Hybrid integration of the wavelength-tunable laser with a silicon photonic integrated circuit. J. Lightwave Technol. 2013, 31, 3934–3942.

42. O’Carroll, J.; Phelan, R.; Kelly, B.; Byrne, D.; Barry, L.; O’Gorman, J.Wide temperature range 0 < T < 85 _C narrow linewidth discrete mode laser diodes for coherent communications applications. Opt. Express 2011,19, B90–B95. [PubMed]

43. Kaur, K.S.; Subramanian, A.Z.; Cardile, P.; Verplancke, R.; Van Kerrebrouck, J.; Spiga, S.; Meyer, R.; Bauwelinck, J.; Baets, R.; Van Steenberge, G. Flip-chip assembly of VCSELs to silicon grating couplers via laser fabricated SU8 prisms. Opt. Express 2015, 23, 28264–28270. [PubMed]

44. Ferrara, J.; Yang,W.; Zhu, L.; Qiao, P.; Chang-Hasnain, C.J. Heterogeneously integrated long-wavelength VCSEL using silicon high contrast grating on an SOI substrate. Opt. Express 2015, 23, 2512–2523. [PubMed]

45. Lu, H.; Lee, J.-S.; Zhao, Y.; Scarcella, C.; Cardile, P.; Daly, A.; Ortsiefer, M.; Carroll, L.; O’Brien, P. Flip-chip integration of tilted VCSELs onto a silicon photonic integrated circuit. Opt. Express 2016, 24, 16258–16266. [PubMed]

46. Worhoff, K.; Heideman, R.G.; Gilde, M.J.; Blidegn, K.; Heschel, M.; Van den Vlekkert, H. Flip-chip assembly for photonic circuits. In Proceedings of the SPIE 5454, Micro-Optics: Fabrication, Packaging, and Integration Strasbourg, France, 8 September 2004.

47. Zhang, X.R.; Zhu,W.H.; Liew, B.P.; Gaurav, M.; Yeo, A.; Chan, K.C. Copper pillar bump structure optimization for flip chip packaging with Cu/Low-K stack. In Proceedings of the 11th International Conference on Thermal, Mechanical & Multi-Physics Simulation, and Experiments in Microelectronics and Microsystems (EuroSimE), Bordeaux, France, 26–28 April 2010.

48. Chen, K.M.; Lin, T.S. Copper pillar bump design optimization for lead free flip-chip packaging. J. Mater. Sci. Mater. Electron. 2010, 21, 278–284.

49. Garrou, P.; Bower, C.; Ramm, P. Chapter1: Introduction to 3D Integration in Handbook of 3D Integration Volume 1—Technology and Applications of 3D Integrated Circuits; Wiley-VCH: Weinheim, Germany, 2008.

50. Fedeli, J.M.; Di Cioccio, L.; Marris-Morini, D.; Vivien, L.; Orobtchouk, R.; Rojo-Romeo, P.; Seassal, C.; Mandorlo, F. Development of silicon photonics devices using microelec-tronic tools for the integration on top of a CMOS wafer. Adv. Opt. Technol. 2008.

51. Wang, Y.-H.; Howlader, M.R.; Nishida, K.; Kimura, T.; Suga, T. Study on Sn-Ag Oxidation and Feasibility of Room Temperature Bonding of Sn-Ag-Cu Solder. Mater. Trans. 2005, 46, 2431–2436.

52. Multicore MF210 VOC-free No Clean Flux. Available online: http://www.henkel-adhesives.com (accessed on 15 October 2016).

53. Horibe, A.; Lee, K.-W.; Okamoto, K.; Mori, H.; Orii, Y. No Clean Flux Technology for Large Die Flip Chip Packages. In Proceedings of the IEEE Electronic Components & Technology Conference, Las Vegas, NV, USA, 28–31 May 2013.

54. Choon-Mei, S.L.; Marbella, C.; Min, T.A. No-clean Polymer Flux Evaluations and its Impact on BGA Solder Joint Quality and Board Level Reliability. In Proceedings of the 34th International Electronic Manufacturing Technology Conference, Melaka, Malaysia, 30 November–2 December 2010.

55. Baehr-Jones, T.; Pinguet, T.; Guo-Qiang, P.L.; Danziger, S.; Prather, D.; Hochberg, M. Myths and rumours of silicon photonics. Nat. Photonics 2012, 6, 206–208.

56. Kaspar, P.; Brenot, R.; Le liepvre, A.; Accard, A.; Make, D.; Levaufre, G.; Girard, N.; Lelarge, F.; Dan, G.-H.; Pavarelli, N.; et al. Packaged hybrid III-V/silicon SOA. In Proceedings of the European Conference on Optical Communication (ECOC), Cannes, France, 21–25 September 2014; pp. 1–3.

57. FDMA Access by Using Low-Cost Optical Network Units in Silicon Photonics. Available online: http://www.fabulous-project.eu (accessed on 15 October 2016).

58. Lindenmann, N.; Balthasar, G.; Hillerkuss, D.; Schmogrow, R.; Jordan, M.; Leuthold, J.; Freude,W.; Koos, C. Photonic wire bonding: A novel concept for chip-scale interconnections. Opt. Express 2012, 20, 17667–17677. [PubMed]

59. Lindenmann, N.; Dottermusch, S.; Goedecke, M.L.; Hoose, T.; Billah, M.R.; Onanuga, T.; Hofmann, A.; Freude, W.; Koos, C. Connecting silicon photonic circuits to multi-core fibers by photonic wire bonding. J. Lightwave Technol. 2015, 33, 755–760. Appl. Sci. 2016, 6, 426 21 of 21

60. Benedikovic, D.; Cheben, P.; Schmid, J.H.; Xu, D.-X.; Lamontagne, B.; Wang, S.; Lapointe, J.; Halir, R.; Ortega-Monux, A.; Janz, S.; et al. Subwavelength index engineered surface grating coupler with sub-decibel efficiency for 220-nm silicon-on-insulator waveguides. Opt. Express 2015, 23, 22628–22635. [PubMed]

61. Shen, B.; Wang, P.; Polson, R.; Menon, R. Integrated metamaterials for efficient and compact free-spaceto-waveguide coupling. Opt. Express 2014, 22, 27175–27182. [PubMed]

62. Yao, J.; Zheng, X.; Li, G.; Shubin, I.; Luo, Y.; Thacker, H.; Mekis, A.; Pinguet, T.; Sahni, S.; Raj, K.; et al. Grating-coupler-based optical proximity coupling for scalable computing systems. SPIE Proc. 2011.

63. Sodagar, M.; Pourabolghasem, R.; Eftekhar, A.A.; Adibi, A. High-efficiency and wideband interlayer grating couplers in multilayer Si/SiO2/SiN platform for 3D integration of optical functionalities. Opt. Express 2014, 22, 16767–16777. [PubMed]

64. Bernabé, S.; Kopp, C.; Volpert, M.; Harduin, J.; Fédéli, J.-M.; Ribot, H. Chip-to-chip optical interconnections between stacked self-aligned SOI photonic chips. Opt. Express 2012, 20, 7886–7894. [PubMed]

65. PhoeniX Software—Solutions for Micro and Nano Technologies. Available online: http://www.phoenixbv.com (accessed on 15 October 2016).

66. Luceda Photonics—Software and Services for Integrated Photonic Designers. Available online: http://www.lucedaphotonics.com/en (accessed on 15 October 2016).

審核編輯 黃宇

-

封裝

+關注

關注

128文章

9306瀏覽量

148947 -

PIC

+關注

關注

8文章

512瀏覽量

91163

發布評論請先 登錄

奇芯光電攜全系列光子集成解決方案精彩亮相OFC 2026

頻率可調諧光子集成外腔激光器

【封裝技術】幾種常用硅光芯片光纖耦合方案

PCBA加工零件封裝技術解析:從傳統到前沿的全面指南

光子封裝中膠水及其使用教程

從材料到集成:光子芯片技術創新,突破算力瓶頸

從成本、量產、質量體系等多維度看瑞沃微CSP封裝的劣勢對比

關鍵技術突破!國內首個光子芯片中試線成功下線首片晶圓

AMD收購硅光子初創企業Enosemi AMD意在CPO技術

「封裝技術」PIC光子集成封裝-從樣機到量產

「封裝技術」PIC光子集成封裝-從樣機到量產

評論