新品采用高爬電距離TO-247-4引腳封裝的CoolSiC1400VMOSFETG2CoolSiC1400VMOSFETG2器件采用TO-247-4引腳封裝,兼具前沿的SiC技術與高爬電距離的堅固

2026-01-04 17:06:49 679

679

怎么封裝函數庫,只留一些回調函數和引腳定義,完整程序不讓人看

2025-12-22 13:49:13

電子發燒友網綜合報道 TOLL(TO-LeadLess,薄型無引腳)封裝得益于其高密度、小型化的特性,在近年受到了功率半導體廠商的關注,在SiC、GaN等寬禁帶半導體中得到越來越多的應用。 ? 近期

2025-12-20 07:40:00 9993

9993 本產品是一款小型液壓紐扣電池封裝機產品。標準配置可用于封裝CR2016、CR2032紐扣電池。也可更換部分模具配件后封裝CR2450、CR2012等紐扣電池.具有體積小,操作方便,成型精確等優點。主要應用于電池材料研發的樣本制作。

2025-12-02 15:42:37 316

316

TPS650061RUKR進行電源設計。電源輸出1.2v,1.8v,3.3v均正常。

由于板子未掛載SDRAM或DDR,將程序的下載地址改為L2RAM(0x11800000)位置也沒辦法正確load,并通過JTAG調試

2025-11-19 19:53:00

無論是4引腳還是6引腳封裝,有源晶振的核心都是一個集成了振蕩電路與石英晶體的完整振蕩器。 其核心功能一致:只需施加額定電源電壓(通常為3.3V或5V),即可在輸出引腳產生穩定、精確的方波時鐘信號,無需任何外部元件。供電是其唯一必要的工作條件。

2025-11-08 15:25:39 2097

2097

下面是HummingBird EV Kit給的版圖,其中DDR3_D0對應的應該是板子上的FPGA的C2引腳:?

不過我在配置MIG的時候,通過讀入ucf文件的方式配置DDR3 SDRAM的引腳

2025-11-06 07:57:09

電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4 1、概 述

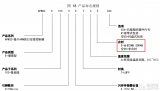

型號:FZH1631

廠商:深圳市方中禾科技有限公司(Premier Chip Limited)

FZH1631是一款標準I2C接口通訊LCD控制/驅動芯片。該芯片提供1/4占空比和1

2025-11-04 09:22:32

在有些情況下,我們想要把代碼放到SDRAM運行。下面介紹在APM32的MCU中,如何把代碼重定位到SDRAM運行。對于不同APM32系列的MCU,方法都是一樣的。

2025-11-04 09:14:18 4981

4981

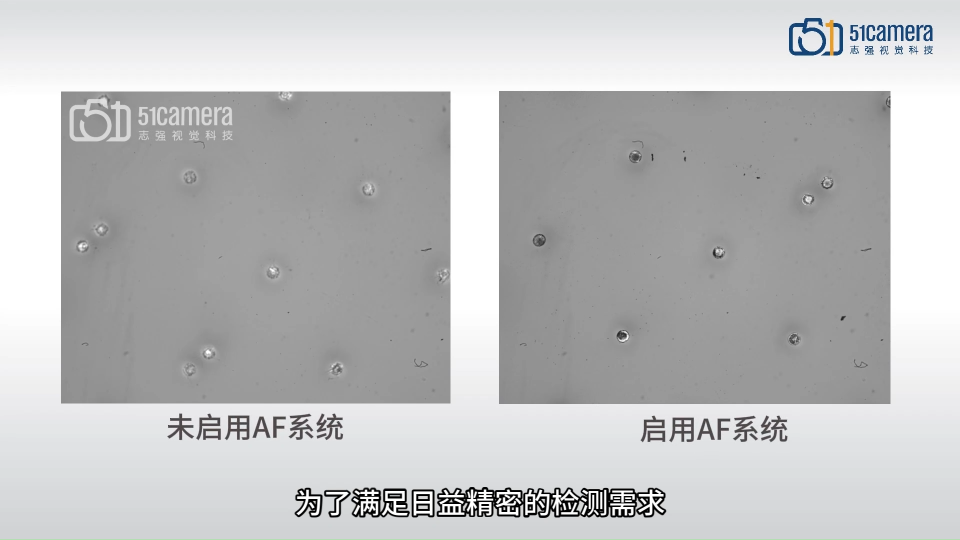

,對企業優化制程、提升產品良率至關重要。

一、核心功能定位:從“形態塑造”到“缺陷修正”

引腳成型:實現引腳的“標準成形”

引腳成型設備的核心功能,是在芯片封裝制程中完成引腳的初次塑形。它將原始的直線狀引腳

2025-10-30 10:03:58

近期,科準測控小編收到了不少來自半導體行業客戶的咨詢,大家最關心的問題之一便是:“IC管腳推力測試,我們該用什么設備?” 這確實是一個核心問題。 在集成電路(IC)封裝領域,芯片與引線框架或基板之間

2025-10-27 10:42:44 339

339

2 級標準)的引腳圖、接線圖、封裝手冊、中文資料、英文資料,0.1 至 8.5 GHz SPDT 開關(符合 AEC-Q100 2 級標準)真值表,0.1 至 8.5 GHz SPDT 開關(符合 AEC-Q100 2 級標準)管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-10-21 18:32:18

而研制的。總體說來,它大概有三次重大的革新:第一次是在上世紀 80 年代從引腳插入式封裝到表面貼片封裝,極大地提高了印刷電路板上的組裝密度;第二次是在上世紀 90 年代球型矩正封裝的出現,它不但滿足了市場高引腳的需求,而且大大地改善了半導體器件的性能;晶片級

2025-10-21 16:56:30 862

862

與封裝企業的標配,其價值在于為大規模生產提供標準化的合格半成品,從源頭提升直通率。

整形設備則更多服務于電子組裝廠、測試實驗室及維修中心。它能顯著降低因引腳變形導致的物料報廢和焊接不良,是提升整體組裝效率

2025-10-21 09:40:14

波峰焊引腳的爬錫高度有標準么?另外引腳高度與焊盤的面積要如何搭配才比較合適?

2025-10-13 10:28:35

keil+Env怎么把很大的數組定義到SDRAM中?

RTT自帶的SDRAM程序運行正常,能夠申請里面的空間。

但是沒有辦法把很大的數組——ltdc_lcd_framebuf[1280][800]

定義到SDRAM中,一運行就出錯,請問各位大佬怎么解決啊?

2025-10-11 16:10:01

問題:首先使用RT-Thread Studio創建了一個rtthread的標準工程,接著直接將正點原子例程LCD驅動的LCD文件夾和SDRAM文件夾移植到rtthread的標準工程,并做對應的適配

2025-09-25 08:16:11

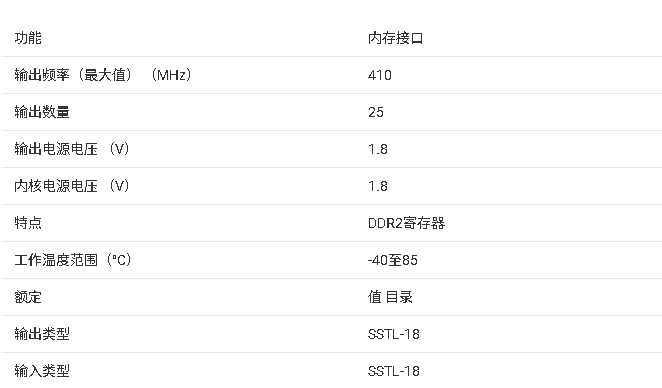

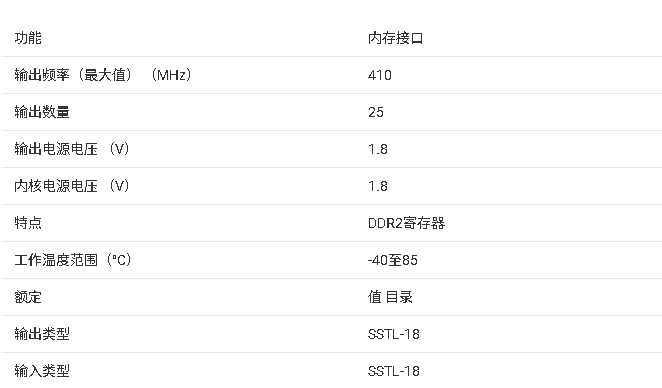

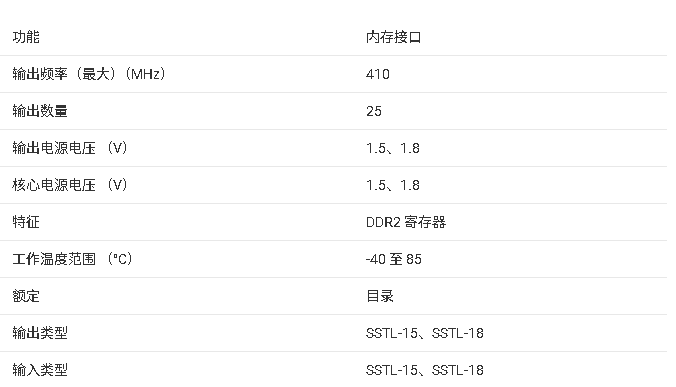

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.7V 至 1.9V VCC 工作。在 1:1引腳配置,每個DIMM只需要一個器件即可驅動9個SDRAM負載。在 1:2 引腳排列中 配置中,每個 DIMM 需要兩個設備來驅動 18 個 SDRAM 負載。

2025-09-18 16:52:01 801

801

裸機以及RTT初始化是可以正常讀寫的,但在線程中,用了rt_thread_mdelay,SDRAM內的數據會被清理,數據丟失,也無法讀寫了,調試發現是rt_schedule導致的,請問這個該問題如何解決?

2025-09-18 07:53:44

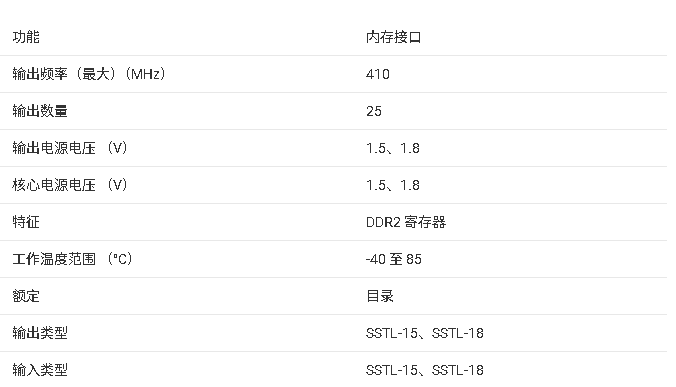

這款 25 位 1:1 或 14 位 1:2 可配置寄存器緩沖器設計用于 1.425V 至 1.9V VCC 工作。在 1:1 引腳配置中,每個 DIMM 只需要一個器件即可驅動 9 個 SDRAM 負載。在 1:2 引腳配置中,每個 DIMM 需要兩個器件來驅動 18 個 SDRAM 負載。

2025-09-17 14:19:28 577

577

掛載sramfs文件系統到外掛sdram ,掛載時返回錯誤碼為-1。求大神指點。謝謝各位大佬。

2025-09-16 06:41:18

新品CoolSiCMOSFET1200V分立器件TO247-4引腳IMZA封裝第二代CoolSiCMOSFETG21200V/53mΩ,TO247-4引腳IMZA封裝,確保安裝兼容性并可輕松替換現有

2025-09-08 17:06:34 931

931

AEC-Q100 標準)的引腳圖、接線圖、封裝手冊、中文資料、英文資料,20 MHz 至 3.0 GHz SPDT 開關(符合 AEC-Q100 標準)真值表,20 MHz 至 3.0 GHz SPDT 開關(符合 AEC-Q100 標準)管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-08-18 18:31:01

兩個總線能不能同時使用,用了華邦的SDRAM發現SDRAM數據高概率讀寫錯誤,但是用ISSI的沒問題。如果不對外部SRAM讀寫就正常。

2025-08-12 06:56:57

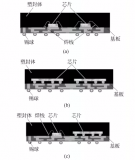

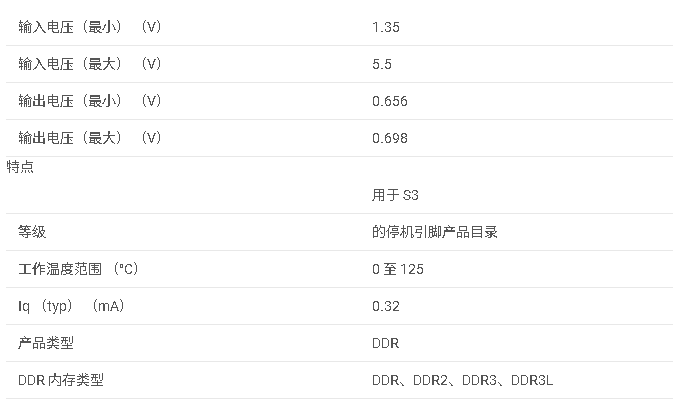

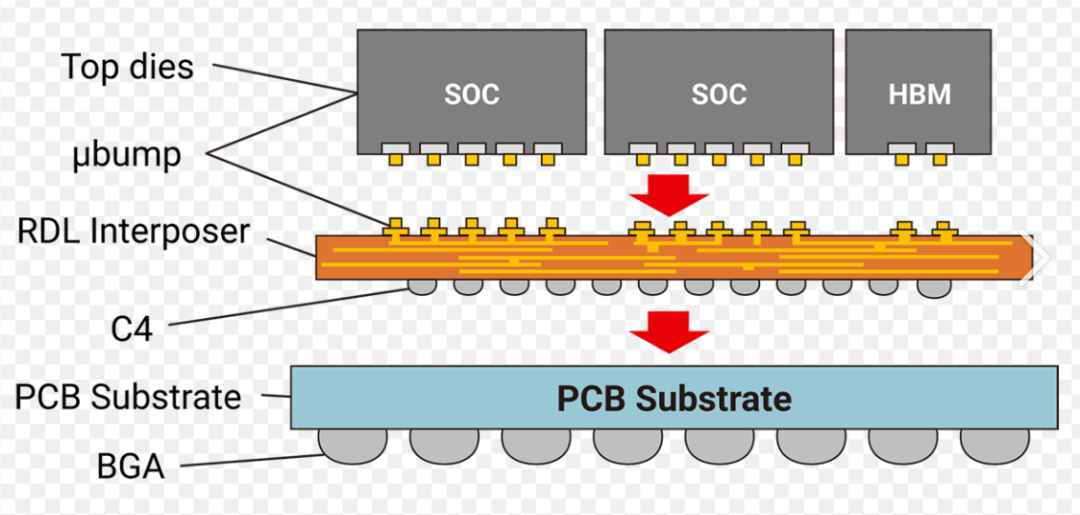

本文主要講述什么是系統級封裝技術。 從封裝內部的互連方式來看,主要包含引線鍵合、倒裝、硅通孔(TSV)、引線框架外引腳堆疊互連、封裝基板與上層封裝的凸點互連,以及扇出型封裝和埋入式封裝中的重布線等

2025-08-05 15:09:04 2135

2135

單片機封裝是將芯片內部電路與外部引腳連接并包裹保護的結構,不僅影響單片機的安裝方式、適用場景,還與電路設計的緊湊性、散熱性能密切相關。不同封裝類型各有特點,適配從簡單電路到復雜系統的多樣化需求

2025-08-01 13:47:34 1042

1042 。這場技術矛盾推動JEDEC、EIAJ等標準組織重構封裝規范,催生出倒裝芯片、BGA、WLP等創新封裝范式。

2025-07-26 09:21:31 1667

1667

對引腳進行精細的調整。例如,上海桐爾科技推出的芯片引腳整形機,采用先進的機械設計和精密的控制技術,能夠對多種封裝形式的芯片引腳進行精確整形。設備配備了高精度的模具和定位系統,確保引腳在整形過程中能夠

2025-07-19 11:07:49

一般我們開發MCU自帶的SRAM,對一般應用來說,已經夠用了,但是對于內存需求較高的場合,比如跑GUI或者算法等,自帶的內存會就不夠用,這個時候就要外擴SRAM或SDRAM。

2025-07-15 09:33:09 1781

1781

端口與外圍設備域相關聯

這個端口的引腳數量取決于所使用的封裝。對于 QFN-48 封裝,有 15 個引腳:P1.00-P1.14。

P1 上信號的最大速度為 8 MHz。

僅支持標準和高速驅動。

P1

2025-06-28 11:44:24

PCB標準封裝庫文件

2025-05-22 17:43:15 9

9 PMG1-S3 48 引腳封裝的 IBIS 文件,其 D+/D- 為空。 IFX 能否修復 IBIS 文件?

2025-05-22 06:26:05

。4. 材料選擇:封裝材料的熱導率對散熱性能至關重要。高熱導率的材料可以更有效地傳導熱量,從而降低模塊內部溫度。5. 封裝結構:封裝的結構設計,如引腳布局、散熱孔等,也會影響散熱性能。合理的結構設計可以

2025-05-19 10:02:47

微電子封裝技術每15年左右更新迭代一次。1955年起,晶體管外形(TO)封裝成為主流,主要用于封裝晶體管和小規模集成電路,引腳數3 - 12個。1965年,雙列直插式封裝興起,引腳數增至6 - 64

2025-05-13 10:10:44 2670

2670

業界普遍認為,倒裝封裝是傳統封裝和先進封裝的分界點。

2025-05-13 10:01:59 1667

1667

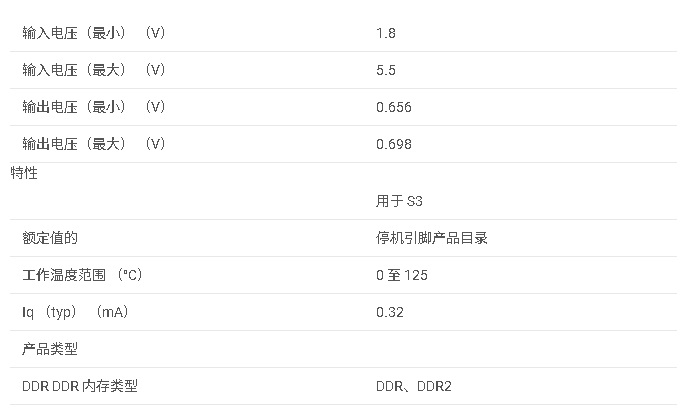

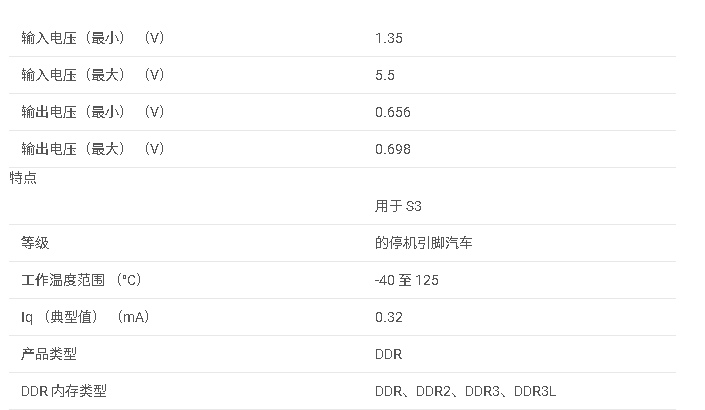

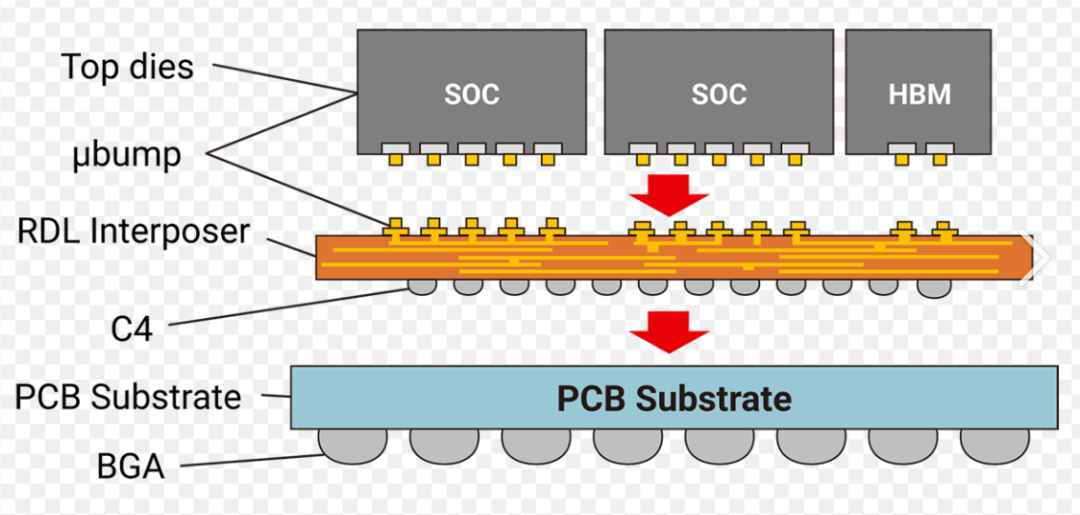

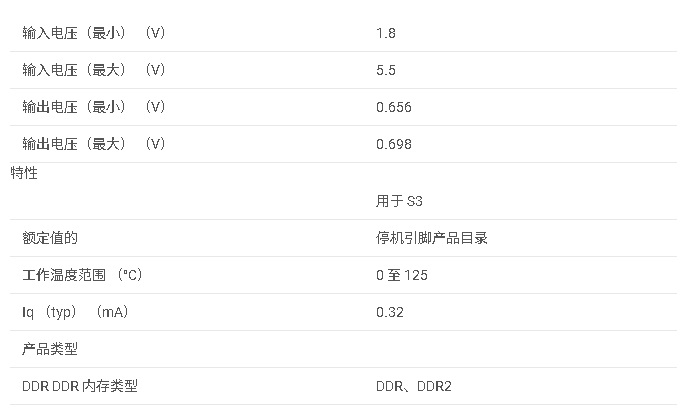

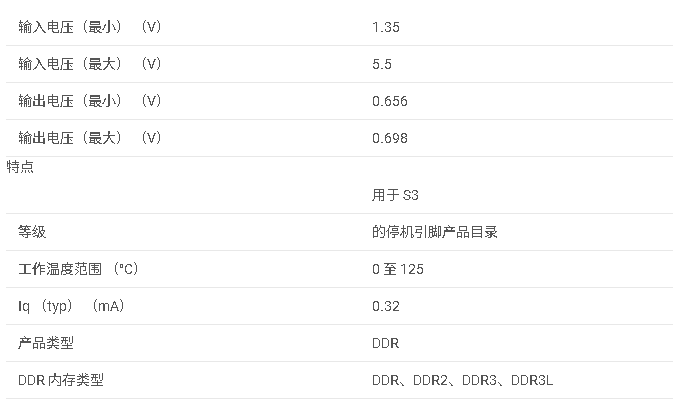

LP2996-N 和 LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 標準 DDR-SDRAM 終止規范。該器件還支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3L

2025-04-29 18:11:05 834

834

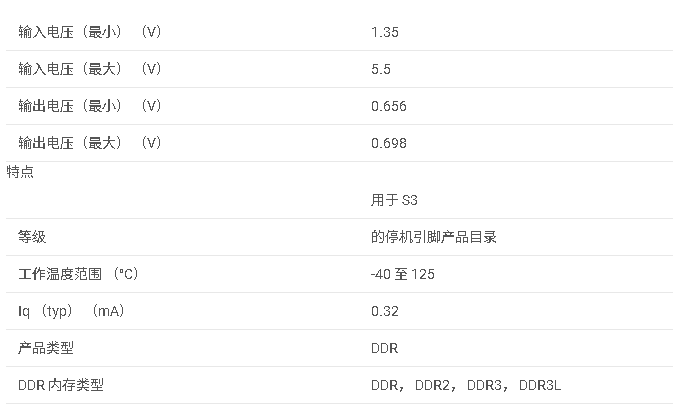

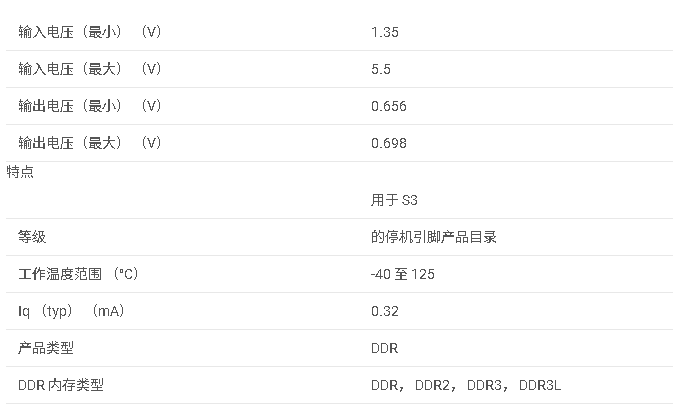

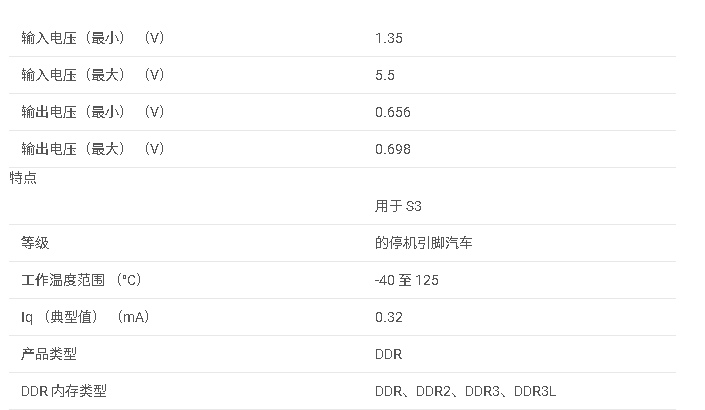

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

。 該器件包含一個高速運算放大器,可提供出色的負載響應 瞬 變。輸出級可防止擊穿,同時提供 1.5A 連續電流和 根據 DDR-SDRAM 端接的要求,應用中的瞬態峰值高達 3A。LP2996A 包含 V~意義~引腳提供出色的負載調節和 V~裁判~輸出作為芯片組和 DIMM 的參考。

2025-04-26 15:02:50 746

746

?:防止芯片受機械損傷、濕氣、灰塵等外界環境影響?; 電氣連接?:通過引腳或焊料凸點實現芯片與外部電路的穩定信號傳輸?; 散熱管理?:優化封裝材料與結構設計,提升芯片散熱效率?; 機械支撐?:增強芯片結構強度以應

2025-04-16 14:33:34 2232

2232 The issue was i need to run data from external SDRAM memory instead of using internal RAM(DTCM). I

2025-04-14 12:21:59

Hi,大家好,我最近要設計hpm6e80 ivm1帶sdram的電路,我參考了官方的評估板,發現hpm6e80 sdram引腳編號與外掛SDRAM芯片沒有對應上(DQ引腳沒有對應上),PPI子模

2025-04-12 18:37:09

源晶振的引腳朝下,以正視的角度,按照逆時針方向依次為2腳、3腳和4腳。 基于封裝外形的引腳識別 : 正方的DIP-8封裝 :打點的是1腳,各引腳功能通常為:1腳一般為NC(空腳,不連接任何功能,在某些設計中也可能有特殊用途,但常規

2025-04-10 17:20:54 1413

1413

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

這個PCB庫是嘉立創的標準集成庫,使包含了一些常用元件和封裝,使用本集成庫進行設計的pcb在嘉立創進行投板時不用進行元件方向和位置的確認,節約成本和時間。

2025-04-09 13:59:06

使用的sdram型號是IS42S16160 32mb的是正常的但是更改到IS4216400 8mb的sdram后不能使用,請問1052支持嗎?需要修改哪些配置,請大神講解一下

2025-04-08 19:40:06

LPC553x MCU 具有硬件 I3C 外設。“PUR” 上拉電阻控制引腳是否僅提供 100 引腳封裝?

如果是,是否有替代解決方案可用于 64 和 48 引腳封裝來處理 SDA 線路上的外部引體向上?

2025-04-07 06:52:37

RT1176 與 DDR SDRAM 兼容嗎?

2025-04-04 06:09:26

在封裝設計中,原點是一個重要的參考點,通常根據封裝類型被設置在關鍵位置,如幾何中心或1腳焊盤等。例如,芯片封裝的原點可能位于幾何中心,而連接器封裝的原點可能在引腳起始位置。Fanyskill 腳本為器件提供了靈活設置原點的功能,能夠快速切換原點位置,以滿足不同設計需求。

2025-03-31 09:37:09 1253

1253

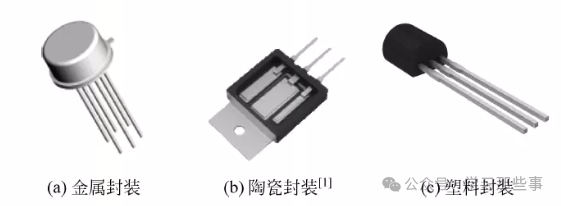

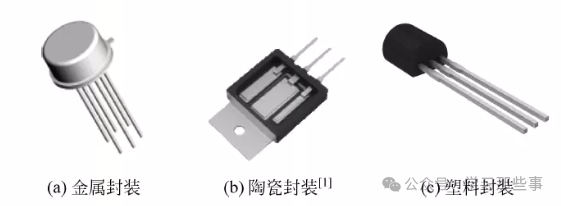

在集成電路(IC)產業中,封裝是不可或缺的一環。它不僅保護著脆弱的芯片,還提供了與外部電路的連接接口。隨著電子技術的不斷發展,IC封裝技術也在不斷創新和進步。本文將詳細探討IC封裝產線的分類,重點介紹金屬封裝、陶瓷封裝以及先進封裝等幾種主要類型。

2025-03-26 12:59:58 2169

2169

STM32H750XBH6TR主芯片,當SDRAM頻率設置為100MHz的時候,FMC_SDCLK和FMC_SDNWE延遲不符合標準,延遲偏大,造成100MHz SDRAM異常,這個延遲有辦法調整

2025-03-14 15:15:19

SDRAM和NAND都使能了,都能正常工作,但是讀取Nand數據然后存放到SDRAM中,發現SDRAM中的數據是錯誤的。但是將數據存到內部的IRAM中數據是正確的。請問NAND跟SDRAM不能同時訪問么?該問題同時存在于STM32F767跟STM32H743中。請幫忙解答,謝謝!

2025-03-11 08:13:19

ma把懷疑是芯片引腳順序問題,剪掉與帶后綴smps后綴封裝引腳有交叉的引腳重新焊會原來的板子電流變正常一點幾ma,使用stlink可以讀到芯片。

請問這是怎么回事哪里出錯了,直接使用的立創的封裝選型是stm32u575vit6

2025-03-11 06:29:17

封裝中的RDL(Redistribution Layer,重分布層)是集成電路封裝設計中的一個重要層次,主要用于實現芯片內電氣連接的重新分配,并且在封裝中起到連接芯片和外部引腳之間的橋梁作用。RDL的設計和實現直接影響到封裝的電氣性能、可靠性和制造成本。

2025-03-04 17:08:35 4658

4658

由于現時高密度封裝,如系統封裝、倒裝晶片、封裝疊加等應用越來越多,而這些封裝元件尺寸甚小。以倒裝晶片為例,其焊球直徑僅有0.05毫米, 焊球間距只有0.1毫米,對貼裝設備的精度要求比標準元件更高。

2025-03-04 16:33:38 865

865

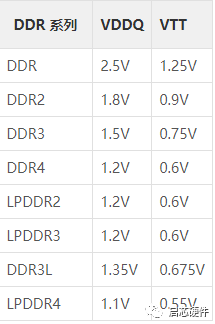

GPIO的控制等等。只有熟悉了這一個個的模塊,才能讓系統正常的轉起來。 研究SDRAM也是一樣,首先看看電源系統部分。 ? ? ? ? ? ?? DDR的電源 ? 主電源VDD和VDDQ,主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給但是一般

2025-03-04 14:44:46 1115

1115

前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MHMF012L1U1-MINAS A6 系列 標準規格書真值表,MHMF012L1U1-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-02-27 19:21:33

為了加深讀者對 FPGA 端控制架構的印象,在數據讀取的控制部分,首先我們可以將SDRAM 想作是一個自來水廠,清水得先送至用戶樓上的水塔中存放,在家里轉開水龍頭要用水時,才能及時供應,相同

2025-02-26 15:27:09 1813

1813

command.v文件對應圖中SDRAM指令執行模塊,它會從SDRAM接口控制模塊接收指令,然后產生控制信號直接輸出到SDRAM器件來完成所接收指令的動作。

2025-02-25 10:32:12 1034

1034

標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MHMF012L1S2-MINAS A6 系列 標準規格書真值表,MHMF012L1S2-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-02-24 19:24:04

標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MHMF012L1D3-MINAS A6 系列 標準規格書真值表,MHMF012L1D3-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-02-20 19:09:28

電子發燒友網站提供《SOD972-S1塑料、超小型和無引腳全密封封裝.pdf》資料免費下載

2025-02-20 14:08:03 0

0 標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MGMF182L1D5-MINAS A6 系列 標準規格書真值表,MGMF182L1D5-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-02-18 19:04:39

誰有CS1262的封裝庫或者 DEMO 開發板的資料

2025-02-14 14:59:00

電子發燒友網站提供《SOD882L-1無引腳超小型塑料封裝.pdf》資料免費下載

2025-02-13 14:15:09 0

0 標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MGMF182L1C5-MINAS A6 系列 標準規格書真值表,MGMF182L1C5-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-02-12 19:14:48

的封裝形式有晶體管式的圓管殼封裝、扁平封裝、雙列直插式封裝及軟封裝等幾種。 1、圓形結構集成電路 圓形結構集成電路形似晶體管,體積較大,外殼用金屬封裝,引腳有3、5、8、10多種。識別時將管底對準自己,從管鍵開始順時針方

2025-02-11 14:21:22 1903

1903 按鍵KEY1觸發寫,將計數器產生的0到255的數據寫到FIFO寫模塊里面,繼而寫到SDRAM 器件里面。

2025-02-07 09:33:41 1192

1192

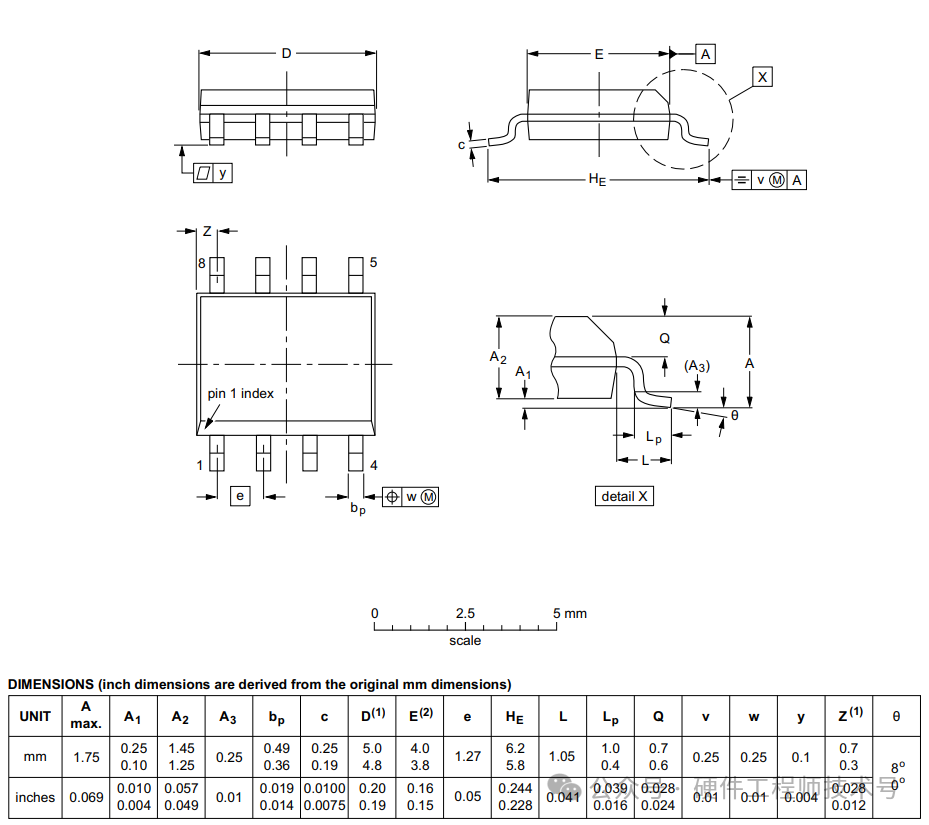

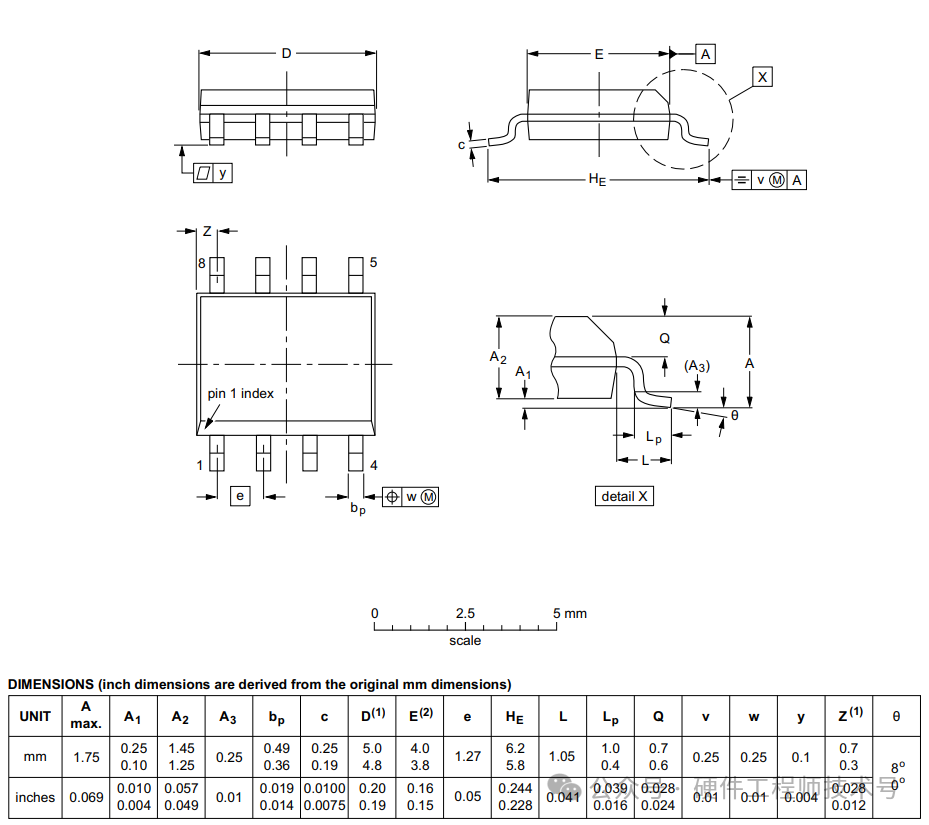

設計 SO-8(Small Outline-8)芯片的 PCB 封裝需要遵循一定的規范和步驟。SO-8 是一種常見的表面貼裝封裝,具有 8 個引腳,引腳間距通常為 1.27mm(50 mil)。以下是設計 SO-8 封裝的詳細步驟和注意事項:

2025-02-06 15:24:26 5112

5112

射頻電路中常見的元器件封裝類型有以下幾種: 表面貼裝技術(SMT)封裝 方型扁平式封裝(QFP/PFP):引腳間距小、管腳細,適用于大規模或超大型集成電路,可降低寄生參數,適合高頻應用,外形尺寸

2025-02-04 15:22:00 1351

1351 標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MDMF304A1DAM-MINAS A6 系列 標準規格書真值表,MDMF304A1DAM-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-01-17 19:07:21

標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MHMF092L1D3-MINAS A6 系列 標準規格書真值表,MHMF092L1D3-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-01-14 18:56:29

電子發燒友網站提供《EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器.pdf》資料免費下載

2025-01-14 15:00:14 0

0 描述這款小型低輸入電流高增益光電耦合器為采用 5 引腳微型化尺寸的單通道器件,采用JEDEC 注冊 SO-5 封裝 (MO-155) 的表面貼裝器件占用空間只有標準 DIP 封裝的 1/4 ,引腳

2025-01-09 10:30:15

你好,我從TI官網上將ADC12D1800的bxl封裝文件下載并傳到ALTIUM 軟件里了,但顯示的原理圖的引腳明顯不夠,在library框下還分為PART A,B,C三個部分,但只能看到一個原理圖,不知道是什么原因(ps 芯片的pcb圖是對的,引腳也夠)

2025-01-09 08:13:45

標準規格書的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MHMF092L1C3-MINAS A6 系列 標準規格書真值表,MHMF092L1C3-MINAS A6 系列 標準規格書管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-01-08 19:02:29

電子發燒友網站提供《EE-326: Blackfin處理器與SDRAM技術.pdf》資料免費下載

2025-01-07 14:38:14 0

0 電子發燒友網站提供《EE-286:SDRAM存儲器與SHARC處理器的接口.pdf》資料免費下載

2025-01-06 15:47:01 0

0 電子發燒友網站提供《EE-127:ADSP-21065L片內SDRAM控制器.pdf》資料免費下載

2025-01-06 15:45:00 0

0 描述這款小尺寸、低輸入電流、高增益光耦合器是一款單通道器件,采用五引腳微型封裝。其SO-5 JEDEC注冊(MO-155)封裝外形不要求PCB上有“通孔”。這種封裝約占標準雙列直插式封裝面積

2025-01-06 15:06:57

電子發燒友App

電子發燒友App

評論