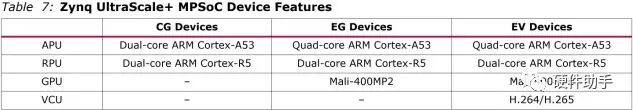

ZU+系列MPSoC的外圍接口詳細分析

本篇主要介紹ZU+系列MPSoC的外圍接口,針對每個接口進行概述性介紹,后續會針對個別接口進行詳細介紹原理圖設計和PCB設計。 ZU+系列MPSoC的外圍接口主要包括兩部分:PL部分和PS部分。PL內部資...

ARM+FPGA開發:基于AXI總線的GPIO IP創建

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門開發基于總線的系統。 使用...

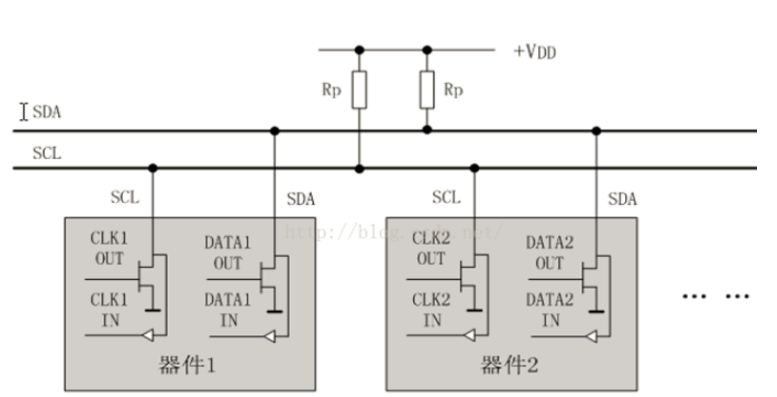

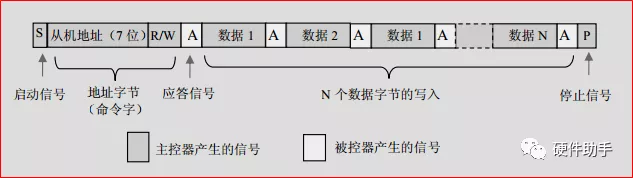

IIC總線通信時序及通信流程解析

IIC協議是一種總線協議,是串行的,是同步的,是半雙工的。它通信速率最高就只有幾百 KB/s 。...

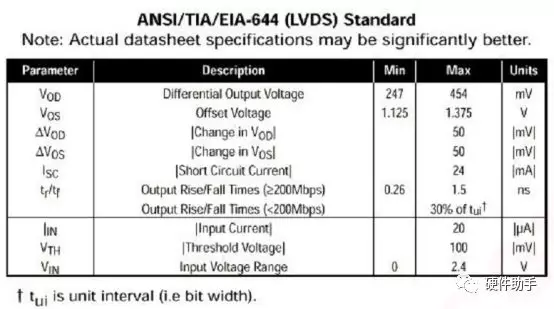

常見差分邏輯電平和相關輸入輸出原理

本篇主要介紹常用的差分邏輯電平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。 1、LVDS電平 LVDS器件是近年來National Semiconductor公司發展的一種高速傳輸芯片,它的傳輸機制是把TTL邏輯電平轉換成低電...

2020-12-23 標簽:CMOSlvdsPCIe差分信號CMOSlvdsPCIeschmitt觸發器差分信號 17713

基于AXI總線的加法器模塊解決方案

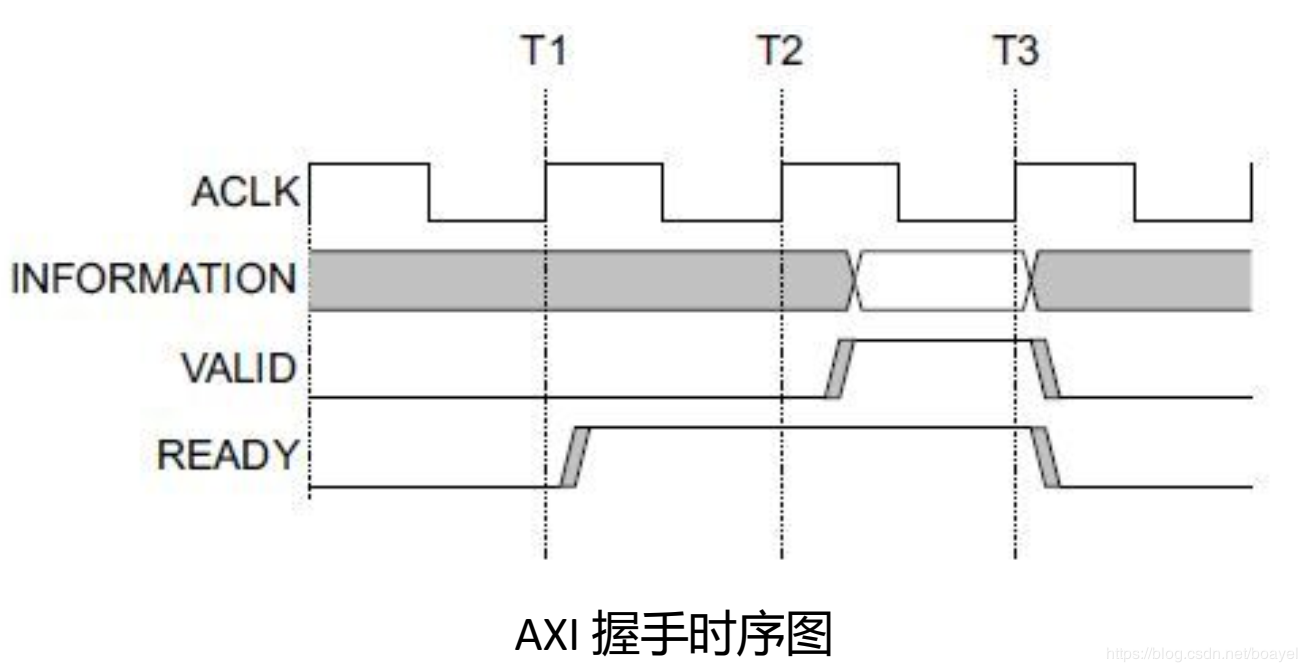

前面一節我們學會了創建基于AXI總線的IP,但是對于AXI協議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯合調試觀察AXI總線的信號。由于我們創建的接口是基于AXI_Lite協議的,所以我...

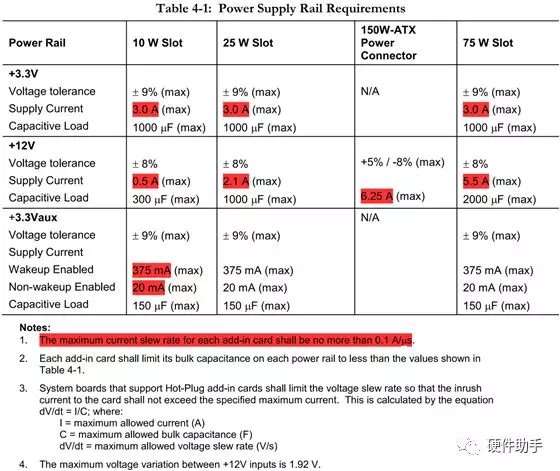

PCIe總線的電源管理之去耦電容

本片主要介紹PCIe總線的電源管理,主要包括不同板卡的功耗、板卡的能耗等級等。 1、功耗等級 根據《PCIx系列之“PCIe總線信號介紹”》,PCIe接口的電源包括+12V、+3.3V、+3.3Vaux三種。根據功耗的...

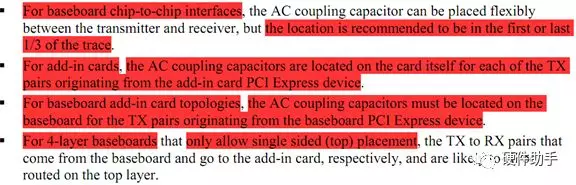

PCIe總線AC耦合及高速信號調整技術

本篇主要介紹PCIe總線的AC耦合電容、總線的去加重等高速信號調整技術。 AC耦合電容可以參考之前的文章《邏輯電平之差分互連AC耦合電容(7)》,本文主要針對PCIe接口介紹AC耦合電容的實際使...

新的IEEE標準10BASE-T1S在汽車和計算機應用中正受到關注

以太網的面向服務的體系結構通過封包功能和數據管理來幫助完成復雜性工作。許多系統可重復使用統一通信機制輕松地相互通信,并允許將服務輕松移動到網絡中的適當位置。...

Xilinx zynq AXI總線全面解讀

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI4 版本。 AXI總線 ZYNQ有三種AXI總線: (A)AXI4:(For high-performanc...

車載USB Type-C設計應考慮的因素分析

傳統USB Type-A接口已經廣泛應用于汽車OEM廠商的各種車型,其供電能力最高為7.5W(5V電壓,最高1.5A電流)。...

2020-12-03 標簽:usb信息娛樂系統PD控制器USB Type-C 3860

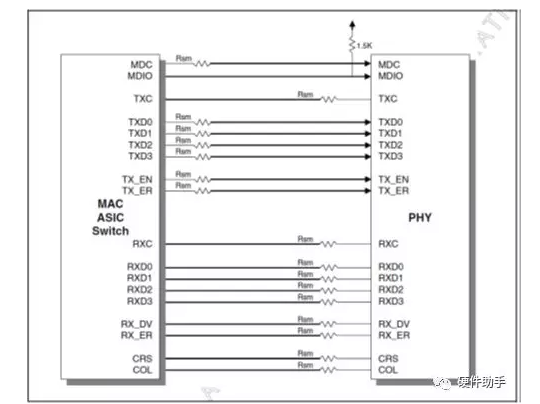

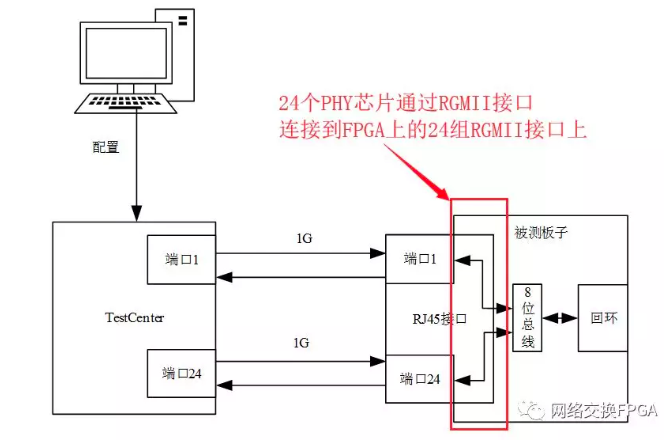

如何使用VIO去讀取PHY里面對應寄存器測試RGMII接口

實驗室回來一批板子,上面有RGMII接口、SGMII接口等各種接口,怎么測試這些網口是否正常呢?的確需要一些經驗。比如RGMII接口,最重要的是看在哪里去做的時鐘和數據偏移。這時,常常需要使...

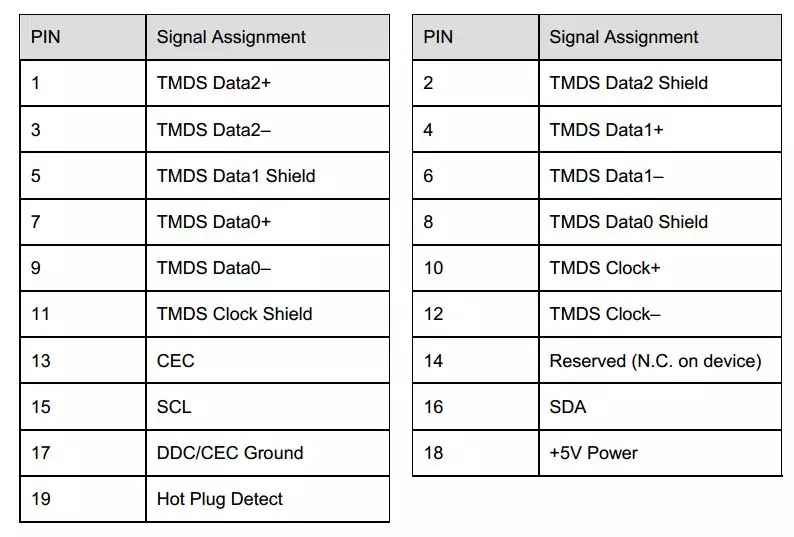

HDMI的協議以及驅動編碼實現案例

HDMI包含物理層和鏈路層結構,物理層定義了信號的物理接口,以及物理層物理層編碼方式。鏈路層定義了幀格式,包含了圖像,聲音,和控制信息。...

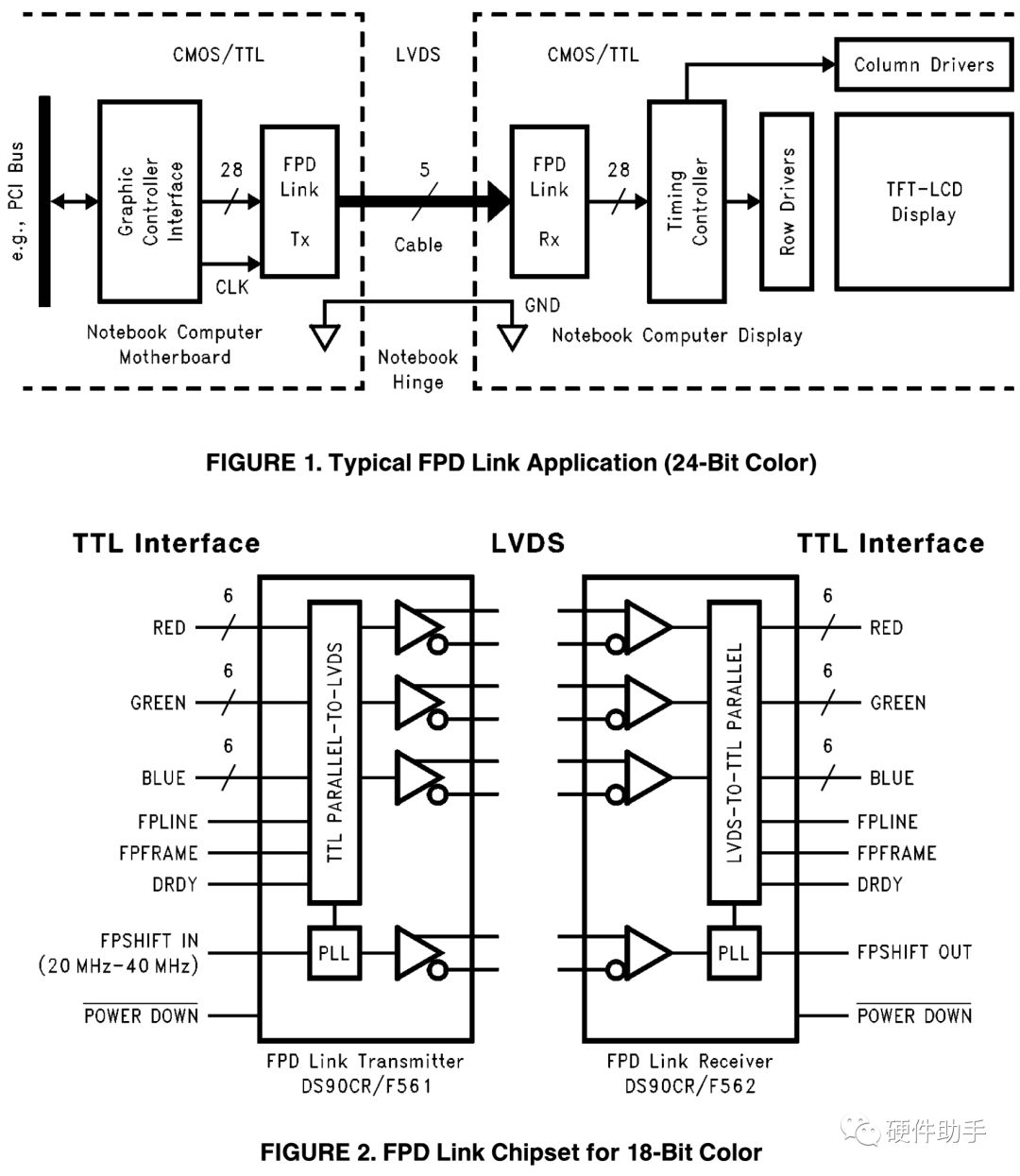

LVDS數傳接口:GMSL和FPD Link

本文介紹兩種LVDS數傳接口:GMSL和FPD Link,這兩種接口在汽車視頻傳輸方面的應用是比較廣泛的,尤其是Camera和處理器之間的鏈路,通過STP或者同軸電纜能使整個鏈路達到15m。 1、FPD Link Flat Pan...

I2C總線相關的基本概念和通信流程解析

I2C總線是PHILIPS公司推出的一種串行總線,是具備多主機系統所需的包括總線仲裁和高低速器件同步功能的高性能串行總線。...

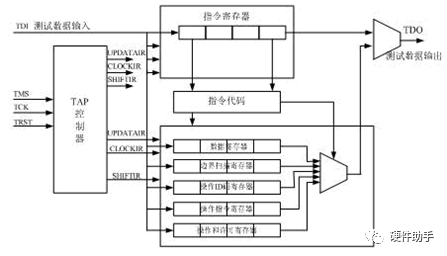

硬件接口協議技術:JTAG內部狀態機——TAP控制器

本文主要介紹JTAG總線的引腳定義、接口標準、邊界掃描和TAP控制器。 JTAG(Joint Test Action Group;聯合測試行動小組)是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的...

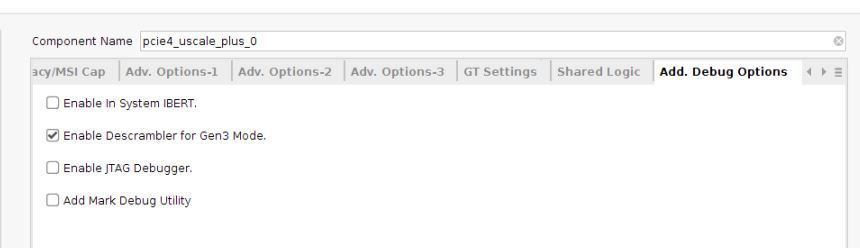

淺談PCIe包分析解擾器模塊的輸出數據

PIPE 接口上的數據在 Gen3 的速度下被加密。當調試 PCIe 問題時,能在 PCIe 鏈接上查看各個包會很有幫助。 若要實現此目的,用戶需擁有協議鏈接分析器。由于其成本較高,能接觸到此等設備的用...

一文解析PCIx系列M-PCIe

M-PCIe即Mobile PCIe,主要應用對象是智能手機等嵌入式設備。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于標準的PCIe總線,M-PCIe ECN主要的改動在物理層,通過引入M-PHY,旨在獲得更低的...

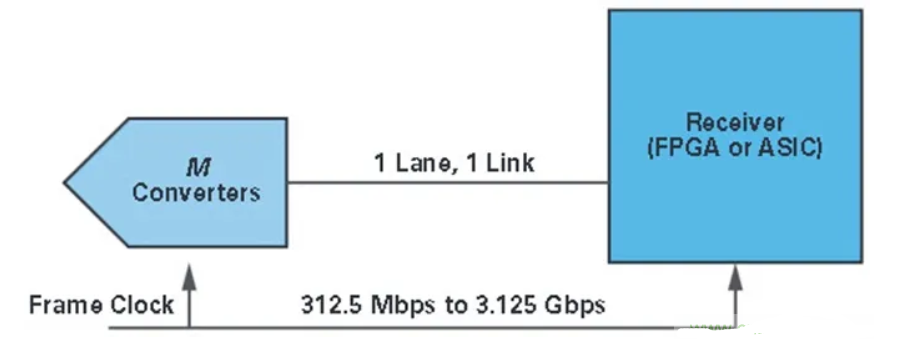

數字接口至轉換器的業界標準——JESD204

隨著轉換器分辨率和速度的提高,對于效率更高的接口的需求也隨之增長。JESD204接口可提供這種高效率,較之其前代互補金屬氧化物半導體(CMOS)和低壓差分信號(LVDS)產品在速度、尺寸和成本方...

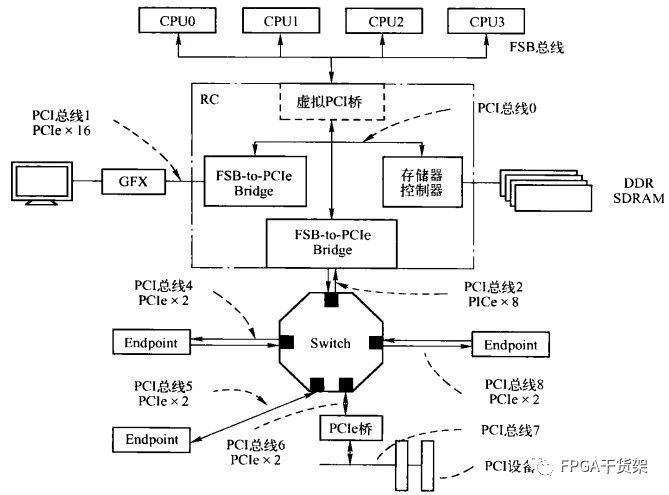

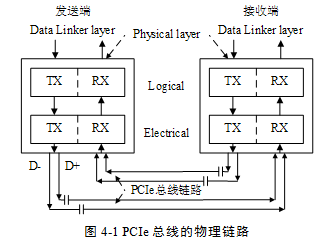

PCI Express總線架構和總線層次結構淺析

作者:romme 1、PCI Express總線架構 如果將計算機比作人的話,CPU就是人的大腦,而PCIe就是人的神經中樞,負責內部數據信息的傳輸。下圖是PCIe總線結構。 處理器系統首先使用一個虛擬的PCI橋分...

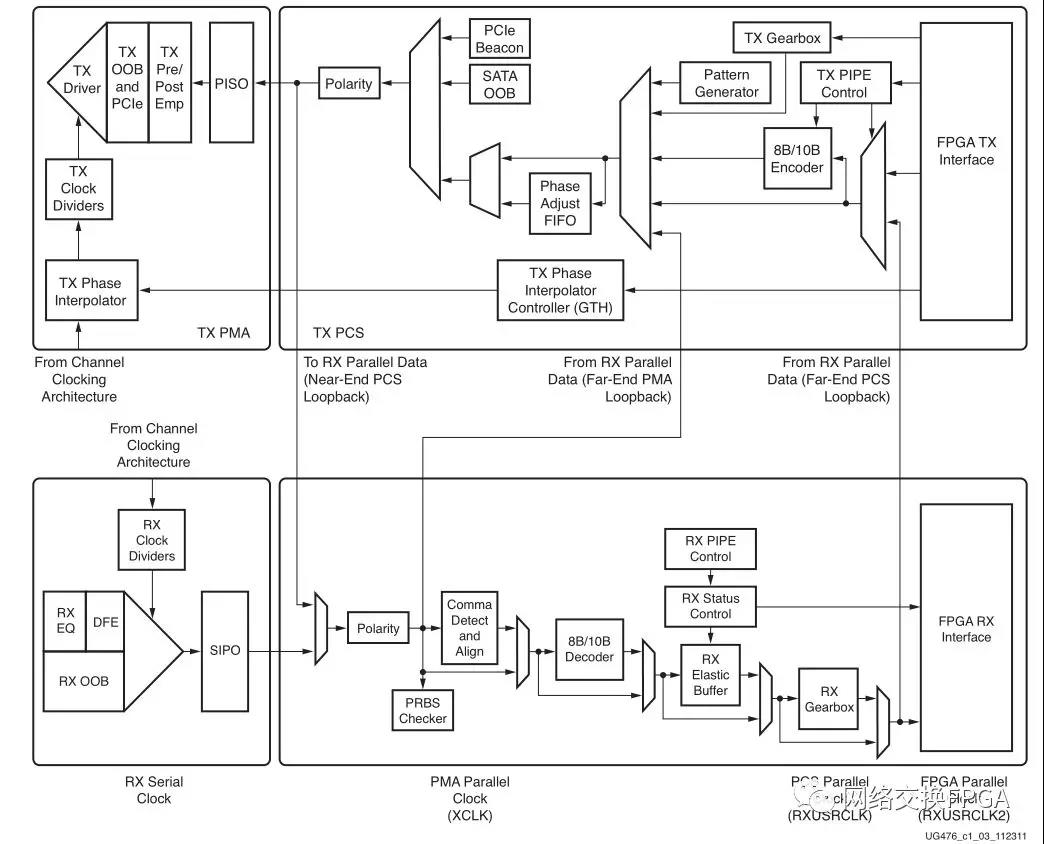

通過光纖實現高速數據片外回環實驗案例

10G以太網光口與高速串行接口的使用越來越普遍,本文擬通過一個簡單的回環實驗,來說明在常見的接口調試中需要注意的事項。各種Xilinx FPGA接口學習的秘訣:Example Design。歡迎探討。 一、實...

Zynq中AXI4-Lite和AXI-Stream功能介紹

Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少。AXI4-Lite接口的特性如...

不同類型的USB Type-C對擴展塢功能有何影響

今天咱們再來聊聊USB Type-C的潛力。相對于USB-A,USB Type-C型接口其實才是擴展塢的最佳搭檔。只是,USB Type-C接口自身也有高低之別,不同檔次的USB Type-C會影響它所支持的擴展塢功能和體驗。 數...

如何設計高效PL和PS數據交互通路的AXI接口

AXI 協議主要描述了主設備和從設備之間的數據傳輸方式,主設備和從設備之間通過握手信號建立連接。當從設備準備好接收數據時,會發出 READY 信號。...

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |