本片主要介紹PCIe總線的電源管理,主要包括不同板卡的功耗、板卡的能耗等級等。

1、功耗等級

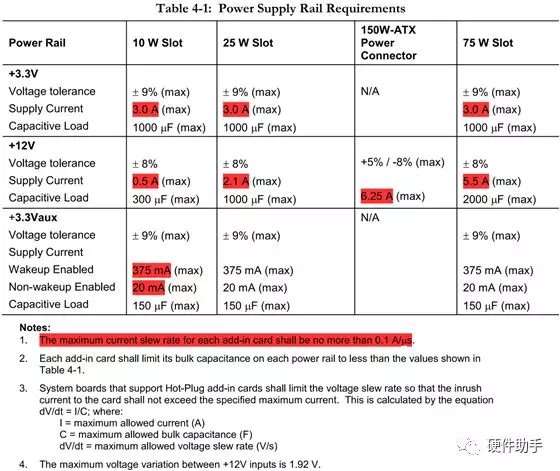

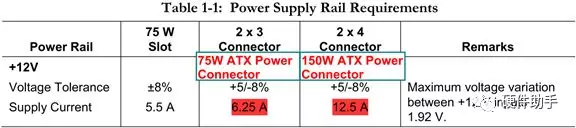

根據《PCIx系列之“PCIe總線信號介紹”》,PCIe接口的電源包括+12V、+3.3V、+3.3Vaux三種。根據功耗的不同,三種電壓的供電能力不同,PCIe卡可以分為以下幾種:

- 10W,直接通過金手指提供;

- 25W,直接通過金手指提供;

- 75W,直接通過金手指提供;

- 150W,需同時通過金手指和2×3Connector提供;

- 225W,需同時通過金手指和2×4Connector提供;

- 300W,需同時通過金手指和2×3Connector和2×4 Connector提供;

3、電源管理

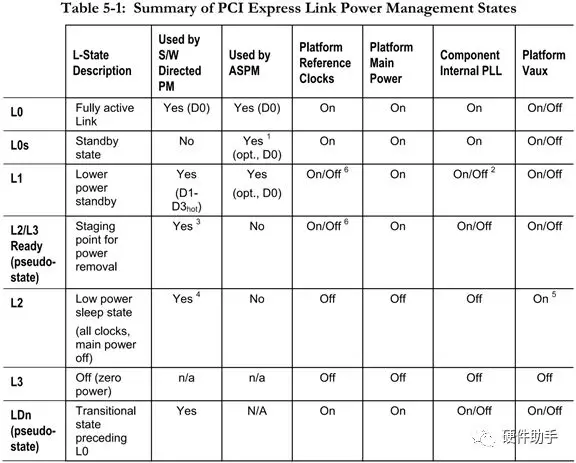

PCIe卡和RC建立連接后,Link power management states有如下幾種:

- L0 – Active state. 是工作狀態,所有的PCIe操作都可以進行。

- L0s – A low resume latency, energy saving “standby” state. 是節能的待機狀態,但是能很快恢復到工作狀態。

- L1 – Higher latency, lower power “standby” state. 是低能耗的待機狀態,需要比L0s更多的時間恢復到工作狀態。

- L2/L3 Ready – Staging point for L2 or L3.

- L2 – Auxiliary-powered Link, deep-energy-saving state. 使用輔助供電,深度節能狀態,實現上面屬于可選的狀態。

- L3 – Link Off state. 是完全關閉的狀態。

- LDn – A transitional Link Down pseudo-state prior to L0.

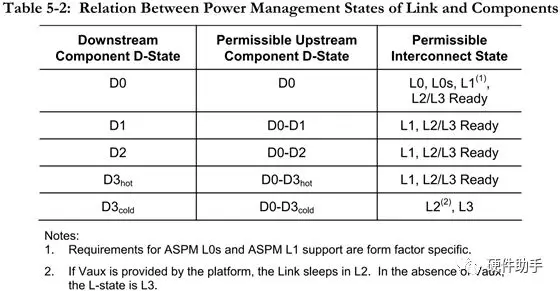

Device Power Management States有如下幾種:

- D0 State

D0 uninitialized state

D0 active state

- D1 State

- D2 State

- D3 State

D3 hot state

D3 cold state

每一種尺寸的卡,在上電時其默認最大功耗是有限制的,可以通過軟件配置更高的功率。每種尺寸的卡的默認功率為:

- A x1 standard height, half-length card is limited to a 10 W maximum power dissipation.

- A x1 low profile card is limited to a 10 W maximum power dissipation.

- A x1 standard height, full-length card is limited to a 10 W maximum power dissipation at initial power up. When the card is configured for high power, by default, it must not exceed a 25 W maximum power dissipation oroptionally it must not exceed a 75 W maximum power dissipation.

- A x4/x8 or a x16 standard height or low profile card is limited to a25 W maximum power dissipation at initial power up. When a card is configured for high power, it must not exceed a 75 W maximum power dissipation.

編輯:hfy

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

PCIE總線

+關注

關注

0文章

58瀏覽量

14036 -

PCIe卡

+關注

關注

0文章

12瀏覽量

7714

發布評論請先 登錄

相關推薦

熱點推薦

小尺寸車規貼片電容 車載 ADAS 模塊電源去耦

尺寸車規貼片電容在車載ADAS模塊電源去耦中的應用,以下從核心參數、選型要點、典型應用場景及推薦方案四個方面展開分析: 一、核心參數:小尺寸與車規級性能的平衡 封裝尺寸與

【「高速數字設計(基礎篇)」閱讀體驗】第六章 去耦電容的容量需求分析

不同設計場景

倍乘系數法:適合負載電容明確的簡單電路,快速出結果;

功耗電容法:解決復雜IC負載電容難測的問題,通過功耗反推更具實操性;

電壓波動約束法:從電源噪聲指標倒推,精準度高。

發表于 11-19 20:48

【「高速數字設計(基礎篇)」閱讀體驗】第五章 去耦電容

最近在啃《高速數字設計》,第五章“去耦電容:遠交近攻”把高速電路里電源噪聲的問題講透了,對于做硬件設計的同學來說,這章簡直是“電源完整性”的

發表于 11-19 20:35

【「高速數字設計(基礎篇)」閱讀體驗】+第五章去耦電容閱讀體驗

去耦電容是PCB設計中用于穩定電源電壓、濾除高頻噪聲的關鍵元件,其作用與布局要求直接影響電路性能。以下是核心要點總結:

一、去

發表于 11-06 17:01

NVMe高速傳輸之擺脫XDMA設計之12:PCIe請求模塊設計(上)

?請求模塊的具體任務是將系統的請求轉換成為axis接口形式的TLP或配置管理接口信號。這些請求主要包含初始化配置請求和門鈴寫請求,初始化配置請求由初始化模塊發起,當配置請求的總線號為0時,請求通過

發表于 08-03 22:00

PCB設計如何用電源去耦電容改善高速信號質量

,高速先生則默默的看向本文的標題:如何用電源去耦電容改善高速信號質量?

沒錯,高速先生做過類似的案例。

如前所述,我們的Layout攻城獅經驗豐富,在他的努力下,找到了另外一個對比模型

發表于 05-19 14:28

nvme IP開發之PCIe下

配置空間 管理PCIe總線。PCI配置空間頭分為Type0和Type1兩種類型,Type0類型配置空間 頭在PCIe總線中用于EP,Type

發表于 05-18 00:48

nvme IP開發之PCIe上

體系架構

RC是PCIe體系樹形結構中的根節點。RC主要負責配置PCIe總線上的所有設備,分配資源、處理傳輸請求,并管理數據流動。在處理器系統中,RC是負責連接CPU與

發表于 05-17 14:54

面試常考:為什么芯片電源引腳的去耦電容一般選100nF?

Part 01 前言

相信搞硬件的兄弟一般都見過芯片電源引腳一般會放一個電容,而且這個電容一般是100nF,而且芯片電源引腳旁的電容內一般還

發表于 04-22 11:38

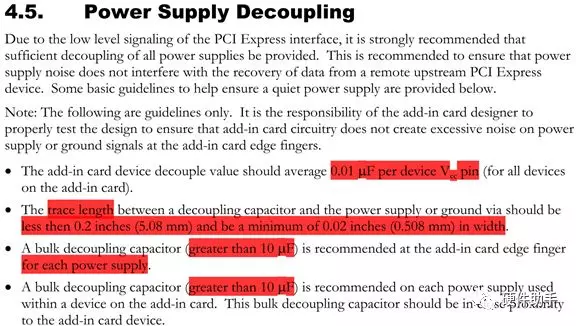

PCIe總線的電源管理之去耦電容

PCIe總線的電源管理之去耦電容

評論