本文主要介紹JTAG總線的引腳定義、接口標準、邊界掃描和TAP控制器。

JTAG(Joint Test Action Group;聯合測試行動小組)是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG協議,如ARM、DSP、FPGA等。標準的JTAG接口是4線:TMS、TCK、TDI、TDO,分別為模式選擇、時鐘、數據輸入和數據輸出線。

JTAG最初是用來對芯片進行測試的,JTAG的基本原理是在器件內部定義一個TAP(TestAccess Port;測試訪問)通過專用的JTAG測試工具對進行內部節點進行測試。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現對各個器件分別測試。現在,JTAG接口還常用于實現ISP(In-System Programmable;在線編程),對Flash等器件進行編程。

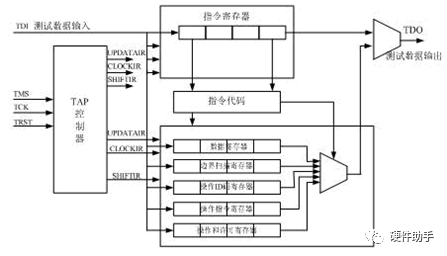

JTAG內部有一個狀態機,稱為TAP控制器。TAP控制器的狀態機通過TCK和TMS進行狀態的改變,實現數據和指令的輸入。

1、引腳定義

含有JTAG口的芯片種類較多,如CPU、DSP、CPLD等。都有如下JTAG引腳定義(信號方向都是針對CPU來說的):

TCK——測試時鐘輸入。TMS和TDI的數據在TCK的上升沿被采樣。數據在時鐘的下降沿輸出到TDO。建議下拉。

TDI——測試數據輸入。輸入到指令寄存器(IR)或數據寄存器(DR)的數據出現在TDI輸入端,在TCK的上升沿被采樣。建議上拉,上拉電阻阻值不能小于1K。

TDO——測試數據輸出。來自指令寄存器或數據寄存器的數據在時鐘的下降沿被移出到TDO。不用上下拉,懸空時,盡量引出測試點,同時應避免將TDO作為I/O使用。

TMS——測試模式選擇。TMS用來設置JTAG口處于某種特定的測試模式,用于控制TAP狀態機。必須上拉。

VTref——目標板參考電壓,接電源。用來確定CPU的JTAG接口使用的邏輯電平。

可選引腳TRST——測試復位,輸入引腳,低電平有效。TRST可以用來對TAP Controller進行復位(初始化)。因為通過TMS也可以對TAPController進行復位(初始化)。所以有四線JTAG與五線JTAG之分。

可選引腳RTCK——測試時鐘返回信號。RTCK由目標端反饋給仿真器的時鐘信號,用來同步TCK信號的產生,不使用時直接接地。

可選引腳nSRST——目標系統復位信號。與目標板上的系統復位信號相連,可以直接對目標系統復位。同時可以檢測目標系統的復位情況,為了防止誤觸發應在目標端加上適當的上拉電阻。

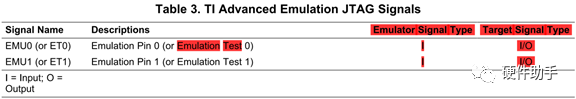

另外還有一些控制器會有如下一些額外信號:

TDIS

PD或TVD——(Presence Detect, Target Voltage Detect),和VTref的功能一樣。

EMU[0:n]或ET[0:n]——(EMUlation, Emulation Test)

EMU pins are bi-directional multifunctional pinsthat provide support for the following features:

Boot Modes

Cross Triggers

Core Trace

System Trace

HS-RTDX (high speed RTDX,deprecated functionality)

In the case of Boot Modes, the EMU0/1 pin state is driven by the XDS. HS-RTDX provides bi-directional data transport. Both Core and System Trace transport event history and timing data from the target to the XDS. Crosstriggers are bi-directional triggers that allow an event in one device to causea debug action in other devices.

2、JTAG接口標準

目前JTAG接口的連接有三種標準,即10針、14針接口和20針接口,其定義分別如下所示。

★由于JTAG經常使用排線連接,為了增強抗干擾能力,在每條信號線間加上地線,偶數針腳都是地信號。

3、邊界掃描(Boundary-Scan)

邊界掃描技術的基本思想是在靠近芯片的輸入輸出管腳上增加一個移位寄存器單元。因為這些移位寄存器單元都分布在芯片的邊界上(周圍),所以被稱為邊界掃描寄存器(Boundary-Scan Register Cell)。

當芯片處于調試狀態的時候,這些邊界掃描寄存器可以將芯片和外圍的輸入輸出隔離開來。通過這些邊界掃描寄存器單元,可以實現對芯片輸入輸出信號的觀察和控制。對于芯片的輸入管腳,可以通過與之相連的邊界掃描寄存器單元把信號(數據)加載到該管腳中去;對于芯片的輸出管腳,也可以通過與之相連的邊界掃描寄存器“捕獲”該管腳上的輸出信號。在正常的運行狀態下,這些邊界掃描寄存器對芯片來說是透明的,所以正常的運行不會受到任何影響。這樣,邊界掃描寄存器提供了一個便捷的方式用以觀測和控制所需要調試的芯片。另外,芯片輸入輸出管腳上的邊界掃描(移位)寄存器單元可以相互連接起來,在芯片的周圍形成一個邊界掃描鏈(Boundary-Scan Chain)。一般的芯片都會提供幾條獨立的邊界掃描鏈,用來實現完整的測試功能。邊界掃描鏈可以串行的輸入和輸出,通過相應的時鐘信號和控制信號,就可以方便的觀察和控制處在調試狀態下的芯片。

4、TAP(TEST ACCESS PORT)

TAP是一個通用的端口,通過TAP可以訪問芯片提供的所有數據寄存器(DR)和指令寄存器(IR)。對整個TAP的控制是通過TAP Controller來完成的。TAP總共包括5個信號接口TCK、TMS、TDI、TDO和TRST:其中4個是輸入信號接口和另外1個是輸出信號接口。一般,我們見到的開發板上都有一個JTAG接口,該JTAG接口的主要信號接口就是這5個。

通過保持TMS為高電平(邏輯1)并在TCK端輸入至少5個選通脈沖(變高后再變低)后TAP邏輯被復位。這使TAP狀態機的狀態從任何其它狀態轉到測試邏輯復位狀態對,JTAG口和測試邏輯復位,該狀態不復位CPU和外設。

通過TAP接口,對數據寄存器(DR)進行訪問的一般過程是:

通過指令寄存器(IR),選定一個需要訪問的數據寄存器。

把選定的數據寄存器連接到TDI和TDO之間。

由TCK驅動,通過TDI,把需要的數據輸入到選定的數據寄存器當中去;同時把選定的數據寄存器中的數據通過TDO讀出來。

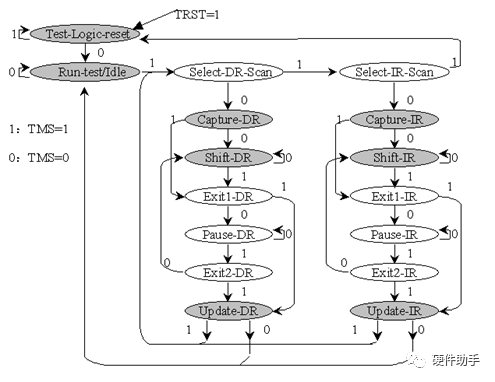

下圖是TAP控制器的16-states有限狀態機圖示:

TAP控制器的狀態在TCK的上升沿變化。

在上電時進入邏輯復位狀態(Test-Logic Reset),在該狀態下,測試部分的邏輯電路全部被禁用,以保證芯片核心邏輯電路的正常工作。通過TRST信號也可以對測試邏輯電路進行復位,使得TAP Controller進入Test-Logic Reset狀態。前面我們說過TRST是可選的一個信號接口,這是因為在TMS上連續加5個TCK脈沖寬度的“1”信號也可以對測試邏輯電路進行復位,使得TAP Controller進入Test-Logic Reset狀態。所以,在不提供TRST信號的情況下,也不會產生影響。

Shift-DR state掃描DR,TDO輸出有效。

Shift-IR state掃描IR,TDO輸出有效。

其他狀態下TDO輸出無效。

如果需要捕獲芯片某個管腳上的輸出,首先需要把該管腳上的輸出裝載到邊界掃描鏈的寄存器單元里去,然后通過TDO輸出,這樣我們就可以從TDO上得到相應管腳上的輸出信號。如果要在芯片的某個管腳上加載一個特定的信號,則首先需要通過TDI把期望的信號移位到與相應管腳相連的邊界掃描鏈的寄存器單元里去,然后把該寄存器單元的值加載到相應的芯片管腳。

指令寄存器的訪問過程:系統上電,TAP Controller進入Test-Logic Reset狀態,然后依次進入:Run-Test/Idle→Select-DR-Scan→Select-IR-Scan→Capture-IR→Shift-IR→Exit1-IR→Update-IR,最后回到Run-Test/Idle狀態。在Capture-IR狀態中,一個特定的邏輯序列被加載到指令寄存器當中;然后進入到Shift-IR狀態。在Shift-IR狀態下,通過TCK的驅動,可以將一條特定的指令送到指令寄存器當中去。每條指令都將確定一條相關的數據寄存器。然后從Shift-IR→Exit1-IR→Update-IR。在Update-IR狀態,剛才輸入到指令寄存器中的指令將用來更新指令寄存器。最后,進入到Run-Test/Idle狀態,指令生效,完成對指令寄存器的訪問。

數據寄存器的訪問:當前可以訪問的數據寄存器由指令寄存器中的當前指令決定。要訪問由剛才的指令選定的數據寄存器,需要以Run-Test/Idle為起點,依次進入Select-DR-Scan→Capture-DR→Shift-DR→Exit1-DR→Update-DR,最后回到Run-Test/Idle狀態。在這個過程當中,被當前指令選定的數據寄存器會被連接在TDI和TDO之間。通過TDI和TDO,就可以將新的數據加載到數據寄存器當中去,同時,也可以捕獲數據寄存器中的數據。具體過程如下。在Capture-DR狀態中,由TCK的驅動,芯片管腳上的輸出信號會被“捕獲”到相應的邊界掃描寄存器單元中去。這樣,當前的數據寄存器當中就記錄了芯片相應管腳上的輸出信號。接下來從Capture-DR進入到Shift-DR狀態中去。在Shift-DR狀態中,由TCK驅動,在每一個時鐘周期內,一位新的數據可以通過TDI串行輸入到數據寄存器當中去,同時,數據寄存器可以通過TDO串行輸出一位先前捕獲的數據。在經過與數據寄存器長度相同的時鐘周期后,就可以完成新信號的輸入和捕獲數據的輸出。接下來通過Exit1-DR狀態進入到Update-DR狀態。在Update-DR狀態中,數據寄存器中的新數據被加載到與數據寄存器的每個寄存器單元相連的芯片管腳上去。最后,回到Run-Test/Idle狀態,完成對數據寄存器的訪問。

以上就是針對JTAG的相關介紹,詳細可參見標準《IEEE Std 1149.1 Test Access Port and Boundary-Scan Architecture》。

編輯:hfy

-

控制器

+關注

關注

114文章

17850瀏覽量

194796 -

cpu

+關注

關注

68文章

11314瀏覽量

225697 -

JTAG

+關注

關注

6文章

415瀏覽量

75249

發布評論請先 登錄

JTAG各類接口針腳定義、含義及SWD接線方式

EtherCAT?轉 Modbus RTU?協議轉換網關實現臺達 EtherCAT?控制器與堆垛機限位開關通訊互聯

睿遠研究院丨IO-Link規范解讀(十一):ISDU狀態機與EVENT事件

使用蜂鳥調試器,無法用cjtag協議調試CM32M433R芯片怎么解決?

當控制器遇上“協議外交官”:CC\\-Link IE轉Modbus RTU的能源數據握手

有可能在 FX3 GPIF2 中創建兩個獨立的狀態機嗎?

求助,關于srammaster.cydsn中狀態機的問題求解

NVMe控制器IP設計之接口轉換

NVME控制器之隊列管理模塊

NVME控制器設計之指令控制

硬件接口協議技術:JTAG內部狀態機——TAP控制器

硬件接口協議技術:JTAG內部狀態機——TAP控制器

評論