本篇主要介紹ZU+系列MPSoC的外圍接口,針對每個接口進行概述性介紹,后續會針對個別接口進行詳細介紹原理圖設計和PCB設計。

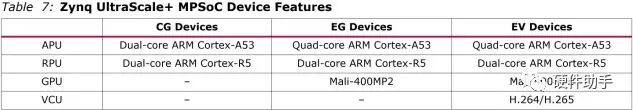

ZU+系列MPSoC的外圍接口主要包括兩部分:PL部分和PS部分。PL內部資源視具體型號而定,PS部分集成兩個或四個ARM Cortex-A53 MPCore with CoreSight(具體數量和性能和具體型號有關),以及兩個ARM Cortex-R5 with CoreSight。

對外接口主要有以下幾種:

- PL CONFIG&SYSMON;

- PL HP I/O banks;

- PL HD I/O banks;

- PL GTH/GTY Quads;

- PS DDRx;

- PS GTR(包括PCIe V2.0, USB3.0, DP1.2a, GbE, SATA V3.1);

- PS Config;

- PS I/O(MIO)(PCIe, PMU, CAN 2.0B, I2C, SPI, QSPI, NAND, USB 2.0 ULPI, GEM Ethernet RGMII, SDIO, UART, GPIO, MDIO, SWDT, TTC, TPIU, PJTAG)。

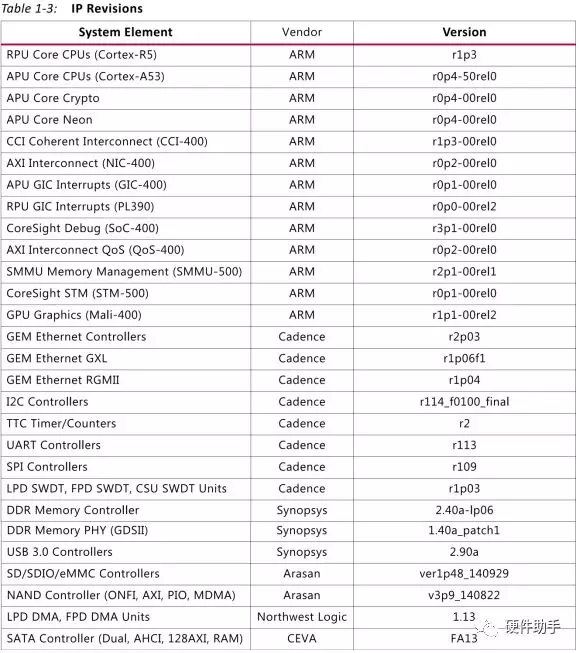

內部硬核都是使用第三方的,具體如下:

1、PL端外圍接口

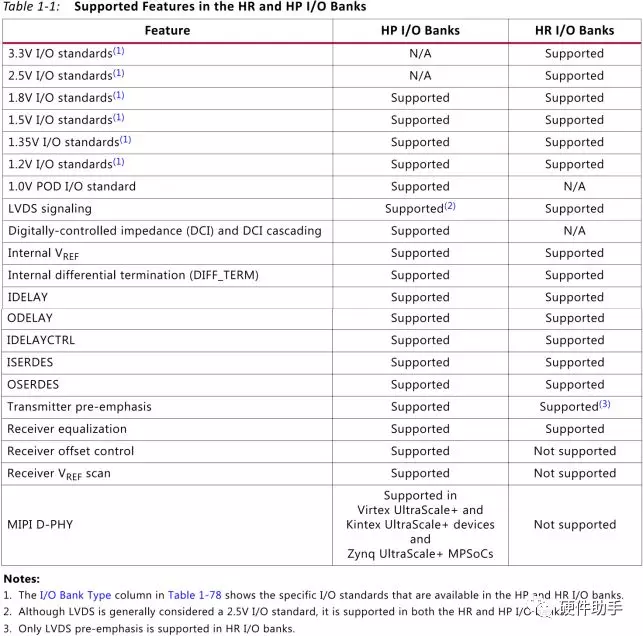

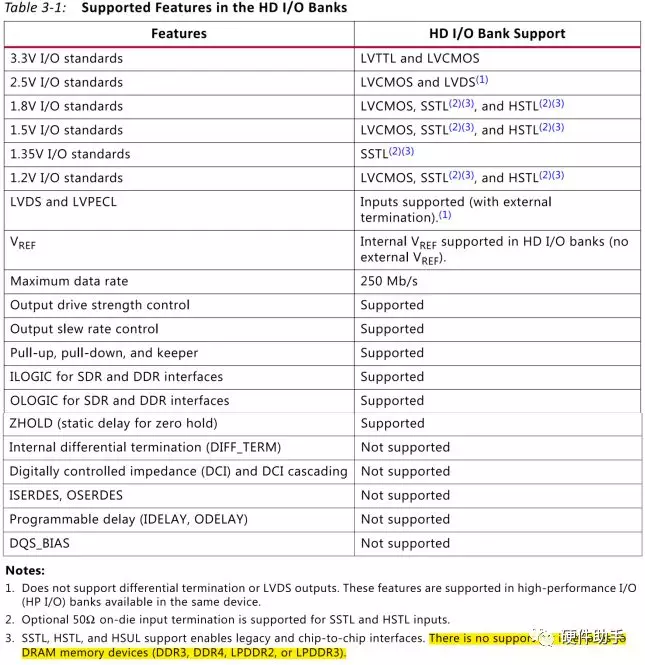

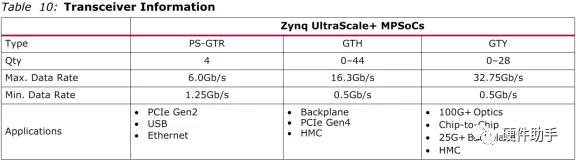

PL端外圍接口包括邏輯部分和GTx部分。邏輯部分包括HP和HD兩種接口,接口數量根據具體型號和封裝不一樣;GTx部分包括GTH和GTY兩種。

HP和HD的接口特性如下:

GTH和GTY接口的特性如下:

2、PS端外圍接口

PS側的引腳主要分為以下幾類:

- Power

- Clock, reset, and configuration

- JTAG interfaces(參考IEEE Std 1149.1)

- Multiplexed I/O (MIO)

- PS GTR serial channels

- DDR I/O

其對外接口主要包括GTR、DDR和MIO接口。除了GTR信號外,所有其他的PS外設均可通過EMIO布線到PL端。

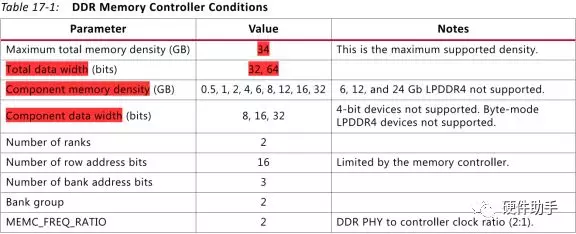

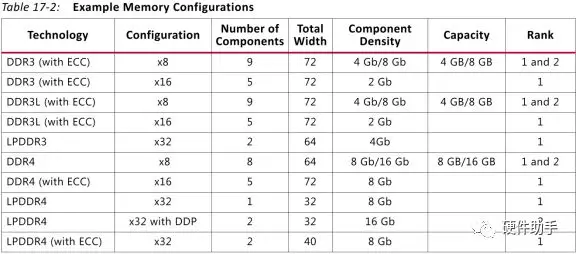

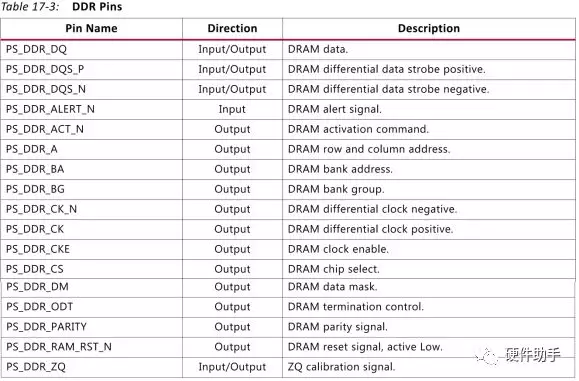

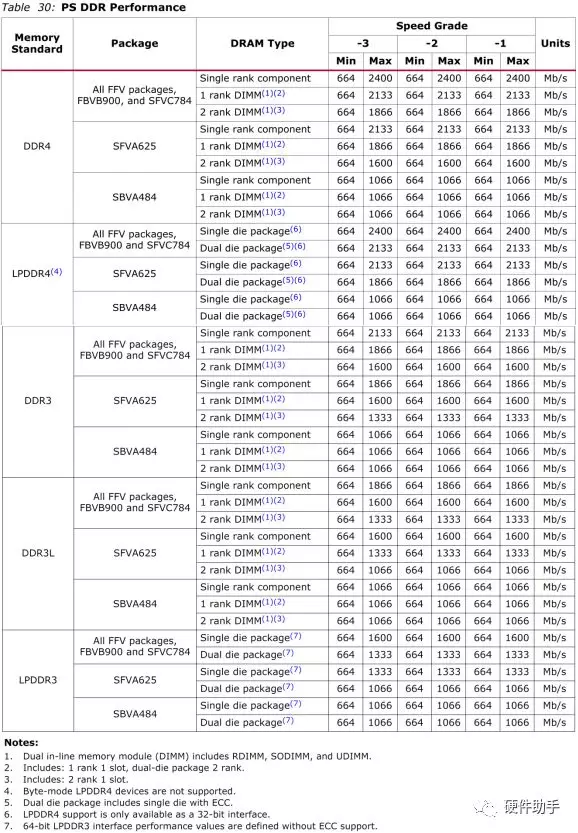

2.1、PS端DDR接口

PS端的DDR接口支持DDR3、DDR3L、LPDDR3、DDR4、and LPDDR4。詳細的參數和性能參考ZU+的TRM,詳細的硬件設計將在后續的文章中詳細講解。

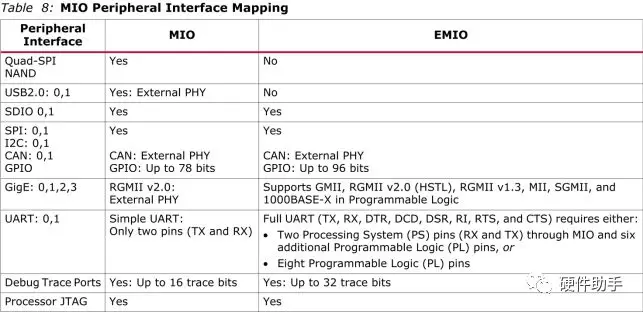

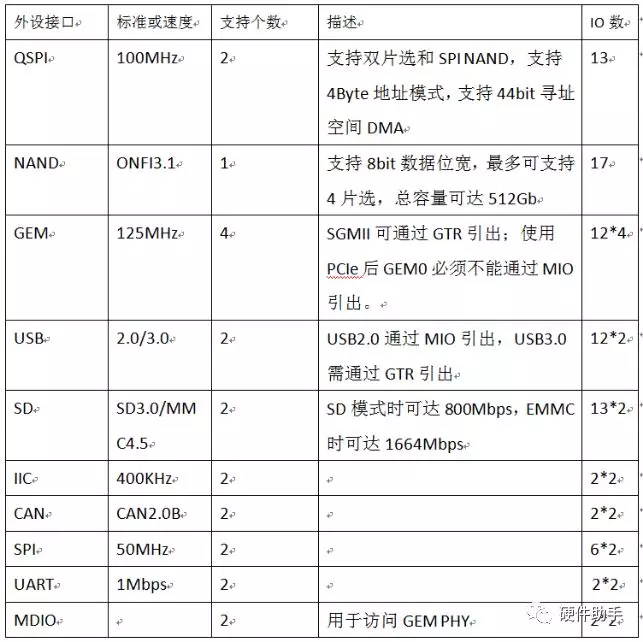

2.2、PS端MIO接口

Zynq UltraScale+具有78個可配置復用的MIO,這些MIO可用作將PS內的相關外設控制器引出,同時這些控制器均可通過EMIO引出。

由于MIO都是復用IO,在進行硬件設計時需要特別注意他們之間的互相限制關系。特別注意:當使用PCIe時,其EndPoint Mode Reset必須接入到MIO29~31, 33~37之間的任意一個引腳上,不能連接到之外的其他引腳。

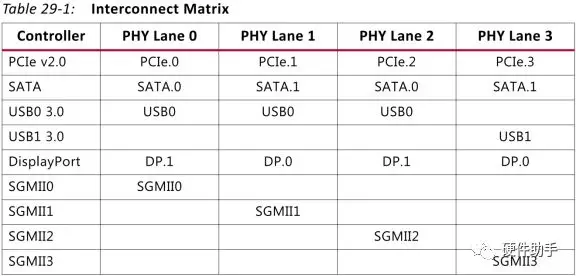

2.3、PS端GTR接口

The PS-GTR transceivers provide the only I/O path for the PCIe v2.0, USB3.0, DisplayPort (transmitter only), SGMII, and SATA controllers.

The PCS provides 8B/10B encoding and decoding, elastic buffer, and buffer management logic such as comma detection and byte and word alignment.

The PMA provides one PLL per lane with the ability to share reference clocks, transmitter de-emphasis, receiver continuous time linear equalizer, SSC support, out-of-band signaling, and LFPS/Beacon signaling for USB3.0/PCIe v2.0 designs.

GTR支持以下幾種協議:

PCIe v2.0 PHY Protocol

- Gen 1 and Gen 2.

- Lane-to-lane deskew for multi-lane PCIe design.

- Beacon signaling.

USB3.0 PHY Protocol

- Integrated RX termination resisters.

- LFPS signaling.

DisplayPort 1.2a PHY Protocol (Transmitter only)

- Reduced bit rate (RBR), 1.62 Gb/s.

- High bit rate (HBR), 2.7 Gb/s.

- HBR2, 5.4 Gb/s.

Gigabit Ethernet SGMII PHY Protocol

PS GEM controller.

SATA v3.1 PHY Protocol

- Generation 1, 1.5 Gb/s.

- Generation 2, 3.0 Gb/s.

- Generation 3, 6.0 Gb/s.

- Out-of-band (OOB) signaling.

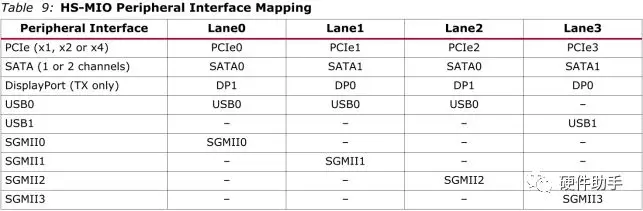

2.4、PS端HS-MIO接口

HS-MIO的功能就是復用高速PS-GTR外圍接口,最大支持4個通道。

以上就是針對ZU+系列MPSoC的外圍接口介紹。

編輯:hfy

-

接口

+關注

關注

33文章

9519瀏覽量

157019 -

MPSoC

+關注

關注

0文章

203瀏覽量

25173

發布評論請先 登錄

RDMA設計27:隊列管理模塊設計之完成模塊詳細分析

渾圓天成!Profinet轉EtherCAT網關模塊配置的詳細分析

詳細分析低煙無鹵阻燃線載流量

這么地道的ADC資料被我找到了?400頁原創pdf原理到應用全覆蓋!

影響電解電容壽命的主要因素及其詳細分析

無刷直線直流電機非換相期間推力分析

無刷直流電機負載能耗制動的分析與實現

Virtuallab Fusion應用:光柵的偏振分析

ZU+系列MPSoC的外圍接口詳細分析

ZU+系列MPSoC的外圍接口詳細分析

評論