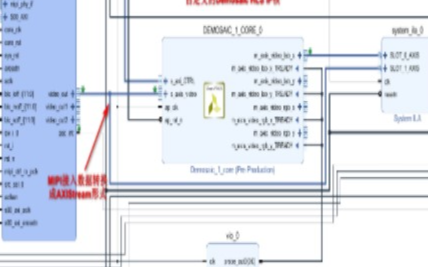

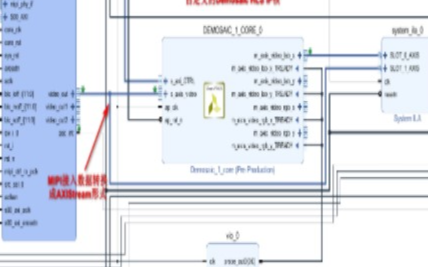

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3470

3470

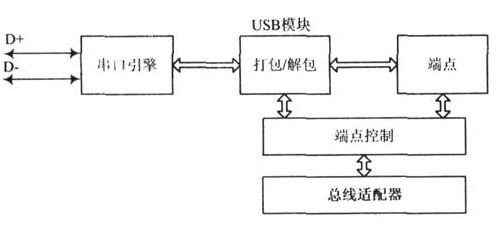

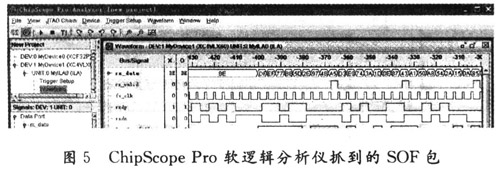

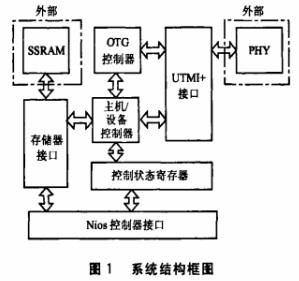

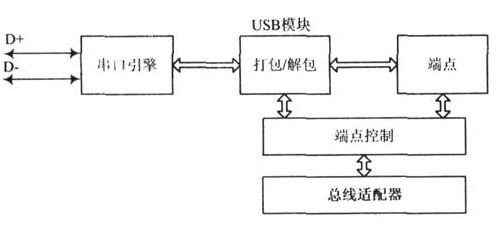

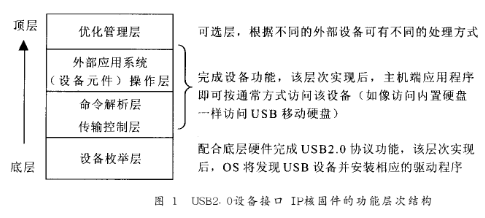

介紹了一款可配置的USB IP核設計,重點描述USB IP核的結構劃分,詳細闡述了各模塊的設計思想。為了提高USB lP的可重用性,本USB IP核設計了總線適配器,經

2010-07-17 10:39:51 3124

3124

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 3688

3688

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

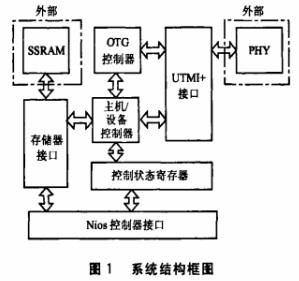

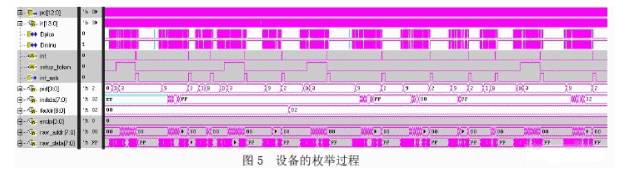

USB OTG的工作原理是什么?IP設計原理是什么?如何進行IP模塊設計?USB OTG IP核有什么特性?如何對USB OTG IP核進行FPGA驗證?

2021-04-27 06:44:33

這兩種數據傳輸方式。相應的測試結果為:USB 2. 0 接口電路功能正確,在高速,全速和掛起狀態下的功耗(包括收發器以及其他的輔助模塊EPP , SDRAM 等) 分別為:584 ,254 ,102 mw

2019-04-12 07:00:12

管理,具有高帶寬、高性能特性,適合于嵌入式處理器與高性能外圍設備、片內存儲器及接口功能單元的連接。 根據兩種總線的特點和廣泛支持,為了給嵌入式SoC系統提供USB接口,需要設計USB和AHB間的橋接IP核

2019-05-13 07:00:04

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

仿真,需要經過綜合以及布局布線才能使用。

IP軟核的優點在于其靈活性高、可移植性強,允許用戶自配置。然而,其缺點在于對模塊的預測性較低,在后續設計中存在發生錯誤的可能性,有一定的設計風險。

選擇合適

2024-05-27 16:13:24

劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進行描述,用FPGA實現并通過了仿真驗證。該IP核具有良好的移植性,可驅動不同規模的LCD電路。 關鍵詞:LCD;驅動電路;IP 引言

2012-08-12 12:28:42

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

本文介紹一款USB OTG IP核的設計與實現,該設備控制器可作為IP核用于SoC系統中,完成與主機控制器的通信,并能與普通的USB從設備進行通信。

2021-04-29 06:47:00

ddr2_controller模塊例化的接口。這里可以分為三大類,第一類為系統類接口,主要是一些系統或PLL的復位、時鐘等接口;第二類為帶“local_*”的接口,是DDR2 IP核與用戶邏輯間的接口;第三類為帶

2016-10-27 16:36:58

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

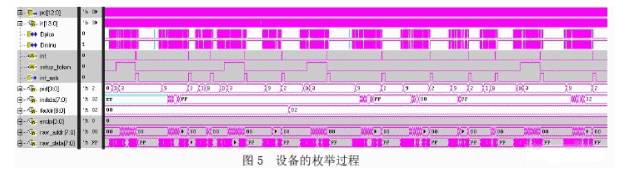

本文的應用背景為某一工業測控系統,該系統采用FPGA實現測量數據的采集和控制信號的輸出,通過定制PCI接口IP實現一個32位目標設備的PCI總線接口轉換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口

2019-06-11 05:00:07

和TECHNOLOGY VIEW兩種原理圖,有利于關鍵路徑的尋找和分析,它還提供了許多功能強大的屬性參數,但同時也增加了軟件使用的復雜性。 VHDL語言中例化的FPGA IP模塊(PCI核,雙端口RAM等

2019-04-17 07:00:06

基于 的XC3S1OOE FPGA的USB接口IP核模塊設計和驗證

2020-12-25 06:48:04

。由于USB的廣泛應用,國內外眾多科研機構和集成電路設計公司都把目光投向USB這項具有廣闊市場前景的技術。USB內核(USB Core)是USB接口控制芯片的關鍵模塊,設計一個穩定、高速的USB內核更是

2018-11-21 11:30:06

基于FPGA的FFT和IFFT IP核應用實例AT7_Xilinx開發板(USB3.0+LVDS)資料共享騰訊鏈接:https://share.weiyun.com/5GQyKKc百度網盤鏈接

2019-08-10 14:30:03

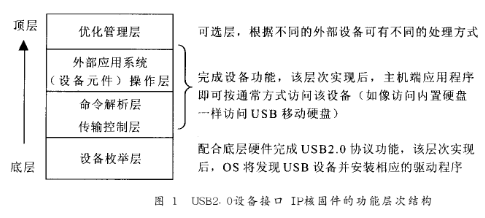

2.0協議外,還負責解釋設備子類協議,并實現對具體外部應用系統(設備元件)的操作。 從硬件結構分析,基于增強型8051MCU核的 USB2.0設備接口芯片(IP核)應包括以下幾個模塊: (1)USB

2018-12-03 15:24:04

作為我項目的一部分,我需要將ADC與7系列FPGA接口,我有一個SelectIO?接口向導的IP核。但是,我的整個項目都在VHDL中,IPi得到的是Verilog。請指出我如何在我的VHDL頂級模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

HiI致力于研究在FPGA / Spartan 3E上連接打印機的研究項目。我可以獲得打印機接口IP核,或者沒有這樣的核心。如果可能,請幫助我。感激地以上來自于谷歌翻譯以下為原文HiI work

2019-07-04 06:32:58

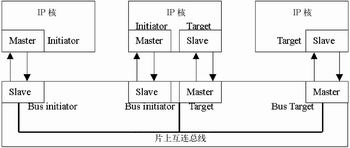

設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從

2018-12-11 11:07:21

最近需要做一個調研,求問各位論壇的大神,各種接口IP:PCIE、USB3.0、serdes等等的價格區間是多少啊,硬核軟核都可以,感謝不吝賜教

2020-01-20 17:59:06

經常看到各大招聘公司都會貼出有高速接口設計經驗者優先,我想知道用了ddr、以太網的ip核,算是有高速接口設計經驗了嗎?

2017-07-16 16:47:18

如何實現基于IP模塊的PCI接口設計?

2021-04-20 06:28:50

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

VIEW兩種原理圖,有利于關鍵路徑的尋找和分析,它還提供了許多功能強大的屬性參數,但同時也增加了軟件使用的復雜性。VHDL語言中例化的FPGA IP模塊(PCI核,雙端口RAM等)應該不參與邏輯綜合,可以在

2019-05-08 07:00:46

一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用來輸出3路相位分別相差2π/3的正弦波

2019-06-03 05:00:05

開放核協議—IP核在SoC設計中的接口技術

2019-05-27 09:52:01

控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個發展趨勢。許多公司推薦使用現成的或經過

2019-04-12 07:00:09

基于USB接口的數據采集模塊的設計與實現Design and Implementation of USB-Based Data Acquisition Module路 永 伸(天津科技大學電子信息與自動化學院,天津300222)摘要文中給出基于USB

2008-10-18 15:24:42 38

38 本文介紹了Tiger560B 處理器和w681511 音頻編碼器。并給出了USB 接口的IP 電話硬件設計與實現方法。關鍵詞:USB;端點;編解碼器Abstract:Tiger560B processor and w681511 codec is presented

2009-06-13 13:24:21 35

35 基于SOC(system on chip)技術,利用VHDL 語言設計開發具有奇偶校驗功能、數據位和波特率可調的通用異步串行通信接口IP 核。該IP 核內置異步接收

2009-09-04 08:49:28 8

8 本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-04 11:39:53 14

14 本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-14 10:48:11 21

21 USB設備接口IP核的設計:討論了用Verilog硬件描述語言來實現USB設備接口IP核的方法,并進行了FPGA的驗證。簡要介紹USB系統的體系結構,重點描述USB設備接口IP核的結構劃分和各模塊的

2010-01-08 18:15:38 22

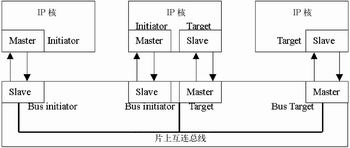

22 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 用硬件描述語言verilog HDL 設計實現了一種MCU&USB 設備控制器IP 核。論文首先簡要介紹了設計的背景,重點對自主研發的將MCU&USB 控制器集成于一個芯片的設計和研究分析。最后

2010-01-20 11:44:09 22

22 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設計,給出了該IP核的系統結構以及各個子模塊的詳細設計方法,并對該IP核進行了功能仿真、FPGA原型驗證,可測性設計以

2010-07-17 16:20:22 21

21 研究基于Avalon-ST接口幀讀取的IP核設計應用,通過Avalon-ST接口將外部存儲中不同格式的幀數據轉化為視頻流進行輸出。根據Avalon總線協議及Avalon-ST視頻協議研究設計方案,使用Verilog H

2010-08-12 15:58:32 0

0 摘 要:本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。 引言隨著半導體技術的發展,深亞微米工

2006-03-24 13:31:58 945

945

摘 要:本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。

關鍵詞:SoC;IP核;

2006-06-07 11:11:53 2412

2412 I2C器件接口IP核的CPLD設計

根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立

2009-03-28 16:21:35 1351

1351

USB2.0設備控制器IP核的AHB接口技術

介紹了USB2.0設備控制器IP核的AHB接口的設計。解決了雙時鐘域問題;實現了多事務DMA控制,減少了塊傳輸的中斷次數;

2009-03-29 15:14:15 1990

1990

USB2.0接口IP核的開發與設計

隨著PC機和外圍設備的發展,傳統的并行接口和串行接口RS-232在易用性(即插即用) 和端口擴展等方面存在著一定的缺陷,這就使之越來越成為通信的

2009-04-22 16:34:43 1602

1602 基于PCI IP核的碼流接收卡的設計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

MCU/USB設備控制器IP核的設計

1 引言

在傳統的計算機系統上常采用串口(如RS232)和并口連接外圍設備,但串口和并口都存在著通信速度 慢

2009-12-08 11:11:08 928

928

介紹了FreeARM7 IP核的基本概況及其接口特點,以LPC2101為原型對該IP核進行了擴展。結合USB 1.1設備控制器IP核和自定制硬件邏輯,構建了一種微控制器功能驗證回路。

2011-04-06 11:41:13 2369

2369

本文介紹的基于Wishbone總線的UART IP核的設計方法,通過驗證表明了各項功能達到預期要求,為IP核接口的標準化設計提供了依據。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 4199

4199

本內容提供了基于 USB接口 的指紋檢測模塊設計

2011-06-29 16:26:07 31

31 文章采用TOP-DOWN 的方法設計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結構模塊均實現了RTL級建模

2011-07-25 18:10:52 93

93 USB2.0規范的推出極大地刺激了包括各類計算機外設在內的多種電子消費產品的開發設計, USB已成為微機和眾多電子設備的重要標準接口。目前國外一些大公司已陸續推出了符合USB2.0規范

2011-09-08 17:55:52 59

59 USB2.0規范的推出極大地刺激了包括各類計算機外設在內的多種電子消費產品的開發設計, USB已成為微機和眾多電子設備的重要標準接口。目前國外一些大公司已陸續推出了符合USB2.0規范

2011-09-21 11:43:03 24

24 設計了一種基于FPGA和USB接口的多通道數據采集系統。該系統采用在FPGA芯片中構建多個數字邏輯模塊的方法,實現對AD芯片模數轉換過程的控制,并利用IP核在FPGA中構建存儲器,對采樣得

2011-12-28 10:34:06 91

91 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源碼:USB2.0 IP核源代碼

2016-06-07 14:13:43 35

35 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。 使用Verilog調用IP核 這里簡單舉一個乘法器的IP核使用實例,使用Verilog調用。首先新建工程,新建demo.v頂層模塊。 添加

2017-02-08 13:08:11 3085

3085

Wifi模塊:USB接口對于wifi模塊有什么作用?

在wifi模塊中,USB充當什么角色呢?實質上wifi模塊上的數據傳輸有兩端:一端是wifi芯片與wifi芯片之間,通過無線射頻(RF)進行數據傳輸;另一端則是wifi芯片與CPU之間,通過USB接口進行數據傳輸。

2017-10-17 15:42:13 29

29 引言 隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統

2017-11-06 11:30:08 0

0 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10749

10749 采用IP核的設計方法,將外設組件互連標準(PCI)總線接口與具體功能應用集成在一個FPGA上芯片, 提高了系統的集成度。在對PCI IP核進行概述的基礎上,介紹了IP核的設計方法,實現了PCI總線

2017-11-17 12:27:03 7056

7056

對DDR2控制器的IP核進行了模塊化的劃分,分析了每個模塊的功能。強調了用戶接口功能的完善,并介紹了IP核的操作流程,使每個用戶都能輕松的使用該IP核。

2017-11-22 07:20:50 5930

5930

本文包含兩部分內容:1)AXI接口簡介;2)AXI IP核的創建流程及讀寫邏輯分析。 1AXI簡介(本部分內容參考官網資料翻譯) 自定義IP核是Zynq學習與開發中的難點,AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

IP核 這里簡單舉一個乘法器的IP核使用實例,使用Verilog調用。首先新建工程,新建demo.v頂層模塊。

2018-05-28 11:42:14 38569

38569 對于IP核輸出數據的解析最好的工具就是其自帶的仿真文件,里面既將接收的數據進行了解析,又將發送給IP核的數據進行了封裝,這對于了解數據結構和協議是十分有幫助的,以太網如此,pcie、ram、fifo等其它IP也如此,我們只需將ip自帶的仿真文件改為我們自己的邏輯即可,接口連接并不變。

2018-07-09 14:07:00 4234

4234 繼USB協議公布后,USB憑借其占用系統資源少、廉價、通用、可熱插拔等優點,成為通用的串行接口總線。當前,絕大部分計算機外圍設備(如打印機、MP3、移動硬盤等)均采用USB接口。但隨著USB接口應用的普及,基于USBl.x和USB2.O規范的USB接口逐漸暴露其缺點。

2019-06-03 08:02:00 2510

2510

AD的IP核哪里有?

2018-10-06 15:37:29 469

469 、AP/Router 、UART WiFi模塊和BLE4.0/4.2/5.0藍牙模塊。本篇SKYLAB的小編將為廣大用戶分析USB接口WiFi模塊的選型參考方案。WiFi模塊USB接口WiFi模塊是高速

2018-11-22 16:39:31 2416

2416 信號層被編碼成NRZI位信息后傳送出去。數據傳輸層用來實現在USB主機端的客戶端驅動程序和設備端的功能接口之間傳輸有一定意義的信息,這些信息在協議層被打包成包格式。

2019-01-11 15:31:25 2978

2978

在WiFi模塊中,USB充當著一個重要的角色。WiFi模塊上的數據傳輸有兩端:一端是WiFi芯片與WiFi芯片之間,通過無線射頻進行數據傳輸;另一端則是WiFi芯片與CPU之間,通過USB接口進行

2020-03-27 10:09:56 3503

3503 自定義sobel濾波IP核 IP接口遵守AXI Stream協議

2019-08-06 06:04:00 4566

4566 國內對該領域的研究尚處于較初級的階段。本文對USB IP核設計方法,提出了一種USB2.0設備接口IP核固件的實現方案,該方案采用合理定義的層次模型并已被實現,實驗結果表明該方案具備良好穩定性和可擴展性的固件結構。

2020-04-04 10:48:00 3182

3182

IEEE802.11 USB接口雙頻WIFI模塊產品下載

2021-04-24 10:50:23 14

14 IP核目前的IP設計已成為目前FPGA設計的主流方法之一,應用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數據塊。IP核在SoC中的集成方式及應用場景,芯片設計中的IP核具有特定功能的可復用的標準性和可交易性,已經成為集成電路設計技術的核心與精華。

2021-10-01 09:08:00 3100

3100 前提:各個IP核的初始化和配置過程確認正確。

2022-02-16 16:21:32 4815

4815

ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 16

16 在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

目前wifi模塊的用途是相當廣泛了,USB接口WiFi模塊的功能被應用各類電子產品生產制造中;通常WiFi模塊系列電子元器件產品中,常用的通信接口就有USB接口WiFi模塊,其中USB接口WiFi模塊按照產品的功能特點多樣,依照具體的功能需求是否需要,設計產品時的WiFi模塊需求來確定。

2021-10-29 22:06:27 2941

2941

濾波器、SDRAM控制器、PCIE接口等),不可能每次使用都要用戶自行設計,所以可以將其設計成 參數可修改的模塊 ,其他用戶可以直接調用。具有復雜功能和商業價值的IP核一般具有知識產權。

2023-08-22 15:04:43 7796

7796

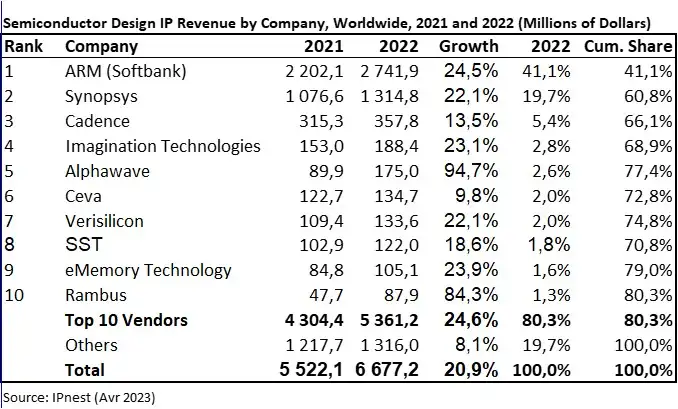

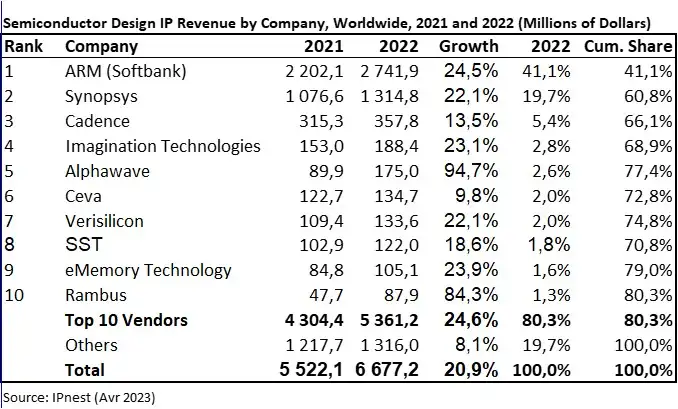

半導體IP通常也稱作IP核(IP core),此處IP也就是指知識產權(Intellectual Property)。IP核就是一些可重復利用的、具有特定功能的集成電路模塊,包含處理器IP、接口IP、物理IP、數字IP等。研究顯示,近5年,接口IP的增速高于處理器IP。‘

2023-09-15 15:59:13 1515

1515

電子發燒友網站提供《基于NiosII的USB接口模塊設計.doc》資料免費下載

2023-10-27 09:49:42 0

0 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

電子發燒友App

電子發燒友App

評論