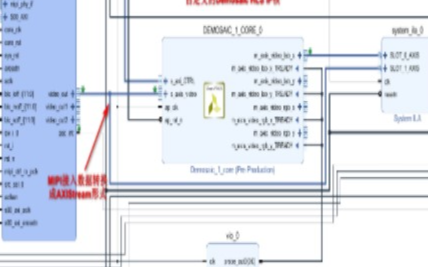

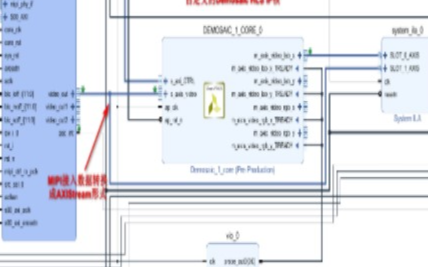

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3468

3468

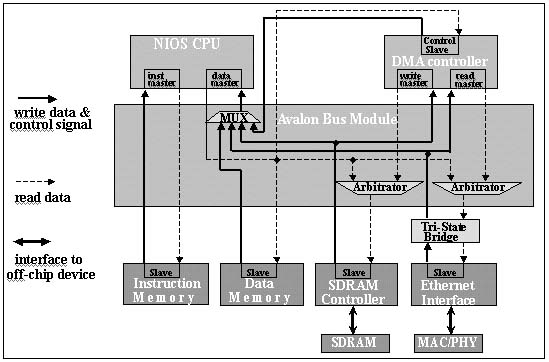

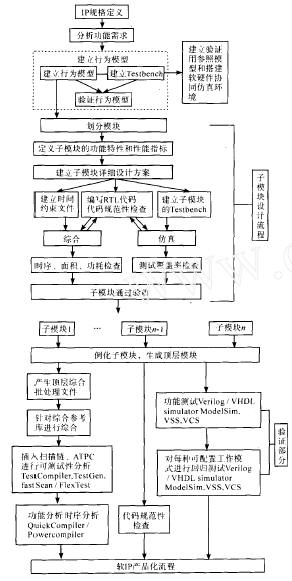

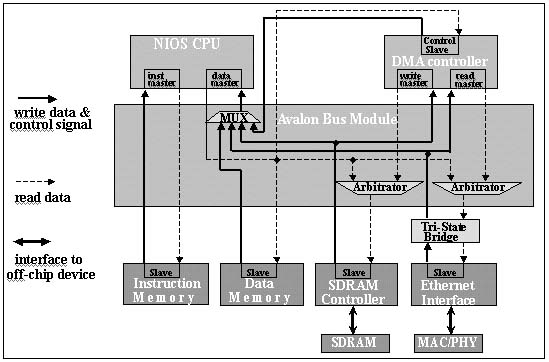

采用基于IP復用技術進行設計是減小這一差距惟一有效的途徑,IP復用技術包括兩個方面的內容:IP核生成和IP核復用。文中采用IP核復用方法和SOC技術基于AVR 8位微處理器AT90S1200IP Core設計專

2012-01-12 14:22:47 2516

2516

本帖最后由 eehome 于 2013-1-5 09:59 編輯

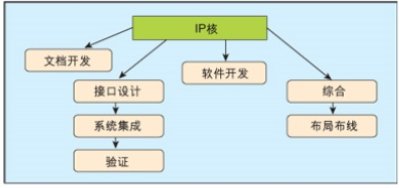

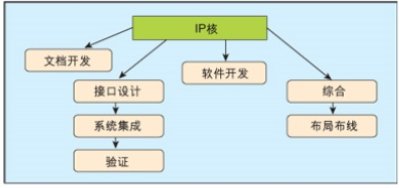

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級

2018-12-11 11:07:21

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

初始化時存入數據。那在IP核rom中存放大量數據對FPGA有什么影響,比如我想存65536個16位的數,然后在64M或者128M的時鐘下讀出來。會不會導致FPGA速度過慢?

2013-01-10 17:19:11

夠與所使用的FPGA平臺和開發工具無縫集成。

閱讀和理解IP軟核的文檔 :

在使用IP軟核之前,務必仔細閱讀和理解其提供的文檔,包括用戶手冊、技術參考手冊、示例代碼等。這將有助于您更好地理解IP軟核

2024-05-27 16:13:24

是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC 階段,IP 核設計已成為ASIC 電路設計公司和FPGA

2018-09-03 11:03:27

FSL總線IP核及其在MicroBlaze系統中的應用

2015-01-18 21:01:20

,國際上只有I-Shou大學的Yu-Jung Huang等人設計了可驅動不同規模LCD的驅動電路IP核,通過在系統中植入嵌入式微處理器來實現這一功能。但是,這種嵌入式微處理器使系統更復雜,而且成本更高

2012-08-12 12:28:42

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2019-06-03 09:09:51

S32G2 聚四氟乙烯

S32G2是ip核還是外設?

如果是ip核,是否可以集成到其他SoC中?

謝謝

2023-06-02 08:04:53

,支持MII、GMII、RGMII、SGMII和TBI接口。在PG051當中為我們進行了詳細的介紹。但光看這文檔效率太低,我們還是在應用種去理解吧。該模塊可以是對協議的具體解析了,需要我們了解TCP/IP協議棧。3.1 IP核的配置 對于該核的配置相對來說還是比較簡單的,如下...

2021-07-22 07:26:36

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

WCDMA無線接口技術第5章 WCDMA無線接口技術在WCDMA系統中,移動用戶終端UE通過無線接口上的無線信道與系統固定網絡相連,該無線接口稱為Uu接口,是WCDMA系統中

2009-09-18 16:48:46

請問哪位高手有ise軟件中的各個ip核的功能介紹

2013-10-08 16:41:25

2.5MHz 振幅0-5V 的正弦信號,請問 data 端口應該輸入怎樣的信號?如果有Altera IP核相關的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

在quartusII中,應用fft ip核時,variable streaming 模式下的bit-reverse(位翻轉)是什么意思?煩勞詳細幫助新手解釋一下,不甚感激

2017-01-09 10:55:59

,這就是IP核。

IP核一般原廠做一些資源開放,定制的IP核一般就要收費了。像做圖像、音視頻處理,AI等,開發可能會涉及到這一方面。IP核有優點也有缺點:IP核往往不能跨平臺使用;IP核不透明,看不到內部核心代碼等。

有關IP核有這方面資料可以分享探討交流學習。

2024-04-29 21:01:16

標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從接口標準的角度討論在SoC設計中提高IP核的復用度,從而簡化系統設計和驗證的方法,主要討論OCP(開放核協議

2019-06-11 05:00:07

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

實現的RTL級設計,與具體實現工藝無關,相比于固核和硬核具有較大的靈活性,在FPGA中定制PCI接口軟核實現PCI接口控制具有明顯的優勢:可以在單片FPGA中同時完成PCI接口和用戶邏輯的設計,縮減成

2018-12-04 10:35:21

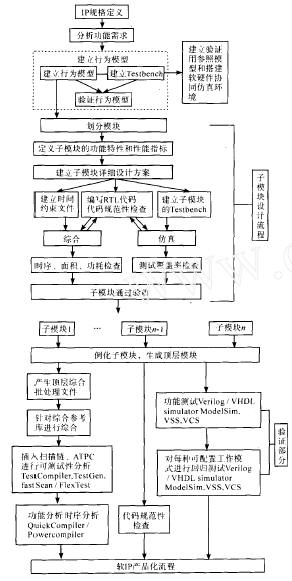

模型;然后合理劃分各摸塊功能規范,制定各模塊之間的接口協議與標準;再設計出一系列通用的IP核;最后把所需的通用IP核搭建整合在一起構成完整的智能傳感器系統。 智能傳感器IP核設計與SOC構建 &

2008-08-26 09:38:34

基于DSP核控制的SoC系統是由哪些部分組成的?基于DSP核控制的SoC系統該如何去設計?

2021-06-18 09:42:47

穩定性和可擴展性的固件結構。 2 USB2.0設備接口IP核的設計USB2.0設備接口芯片IP核分為硬件和固件兩大部分。其中硬件部分主要完成USB2.0協議中的鏈路層功能;而固件除協助硬件完成USB2.0

2018-12-03 15:24:04

告沒被運行的“邊際”(cornercase)。IP提供商必須提供一個進行接口完全驗證所需的邊角情況表。在開發過程中,協議制表器將幫助SoC團隊決定哪些“邊際”情況需要繼續驗證。一旦開發結束,它同時確保通知

2021-07-03 08:30:00

HiI致力于研究在FPGA / Spartan 3E上連接打印機的研究項目。我可以獲得打印機接口IP核,或者沒有這樣的核心。如果可能,請幫助我。感激地以上來自于谷歌翻譯以下為原文HiI work

2019-07-04 06:32:58

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

工欲善其事,必先利其器。在電子技術飛速發展的今天,熟練使用相關工具軟件是學習SoC的必經之路。但是,由于SoC是一個完整的系統,既包含處理器核、總線、外設等硬件,也包含處理器需要執行的指令,所以

2022-07-13 15:04:56

有人知道為什么MIG IP核中的AXI協議。為什么沒有AXI_WID這個信號呢。

2018-04-13 09:22:30

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c1概述Vivado標準IP核的移植可謂簡單至極。簡單3步,拷貝IP文件夾到當前工程目錄下;在Vivado的IP Sources中

2019-09-04 10:06:45

請教大神怎樣使用ARM DesignStart計劃開放的處理器核搭建SoC系統呢?

2022-07-29 15:01:05

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

開放核協議—IP核在SoC設計中的接口技術

2019-05-27 09:52:01

在介紹IEEE802.11MAC 協議結構的基礎上,給出協議開發的方法和步驟,提出IEEE802.11MAC 協議在32 位ARM7TDMI 微處理器S3C4510B 上的一種移植方案,開發出了嵌入式IEEE802.11MAC 協議的IP核。同時

2009-05-16 14:23:46 10

10 以 IP(Intellectual Property )核復用為基礎的SoC(System on a Chip,簡稱SoC)設計是以軟硬件協同設計為主要設計方法的芯片設計技術。本文從IP 核復用技術、軟硬件協同設計技術兩個方面

2009-08-10 08:32:17 18

18 基于SOC(system on chip)技術,利用VHDL 語言設計開發具有奇偶校驗功能、數據位和波特率可調的通用異步串行通信接口IP 核。該IP 核內置異步接收

2009-09-04 08:49:28 8

8 近幾年基于預定制模塊IP(Intellectual Property)核的SoC(片上系統)技術得到快速發展,各種功能的IP 核可以集成在一塊芯片上,從而使得SoC 的測試、IP 核的

2009-09-09 08:33:41 24

24 IC設計技術中的IP核互連:隨著IC 設計復雜度的不斷提高,在SoC 中集成的IP 核越來越多,基于片上總線的SOC 設計技術解決了大規模集成電路的設計難點,但是片上總線的應用帶來了

2009-10-14 12:50:23 8

8 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 20

20 隨著集成電路設計復雜度的提高和產品上市時間壓力的增大,基于IP 核復用的SoC 設計已成為一種重要的設計方法。在SoC 中集成的IP 核越來越多時,IP 核的互連策略和方法就成

2009-11-28 14:40:46 8

8 本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-04 11:39:53 14

14 本文討論了以IP(Intellectual Property)內核為中心的開放式IP 核接口協議(OCP Open CoreProtocol),包括協議特性以及基于OCP 協議的SoC(System on Chip)中設計與驗證等,并在此基礎上提出了基于OC

2009-12-14 10:48:11 21

21 USB設備接口IP核的設計:討論了用Verilog硬件描述語言來實現USB設備接口IP核的方法,并進行了FPGA的驗證。簡要介紹USB系統的體系結構,重點描述USB設備接口IP核的結構劃分和各模塊的

2010-01-08 18:15:38 22

22 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 介紹了系統芯片SOC的概念和M8051 IP軟核的原理,給出了視頻字符疊加器VAD_SOC中M8051 IP軟核的作用,詳細介紹了I2C主控制器模塊的設計,給出了功能仿真波形,最后對M8051IP軟核在視頻

2010-07-05 14:31:33 47

47 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設計,給出了該IP核的系統結構以及各個子模塊的詳細設計方法,并對該IP核進行了功能仿真、FPGA原型驗證,可測性設計以

2010-07-17 16:20:22 21

21 研究基于Avalon-ST接口幀讀取的IP核設計應用,通過Avalon-ST接口將外部存儲中不同格式的幀數據轉化為視頻流進行輸出。根據Avalon總線協議及Avalon-ST視頻協議研究設計方案,使用Verilog H

2010-08-12 15:58:32 0

0 在SOC設計日趨復雜化的今天,其發展的兩大挑戰是IP復用技術和IP互聯技術,研究IP復用技術對于業界具有重要的現實意義。SPI接口技術是一種高速、全雙工、同步的通信總線,

2010-10-20 16:21:54 47

47 介紹了用于IP核測試的內建自測試方法(BIST)和面向測試的IP核設計方法,指出基于IP核的系統芯片(SOC) 的測試、驗證以及相關性測試具有較大難度,傳統的測試和驗證方法均難以滿足

2010-12-13 17:09:11 10

10 摘 要:本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。

關鍵詞:SoC;IP核;

2006-06-07 11:11:53 2412

2412 基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 1195

1195

I2C器件接口IP核的CPLD設計

根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立

2009-03-28 16:21:35 1351

1351

USB2.0設備控制器IP核的AHB接口技術

介紹了USB2.0設備控制器IP核的AHB接口的設計。解決了雙時鐘域問題;實現了多事務DMA控制,減少了塊傳輸的中斷次數;

2009-03-29 15:14:15 1990

1990

USB2.0接口IP核的開發與設計

隨著PC機和外圍設備的發展,傳統的并行接口和串行接口RS-232在易用性(即插即用) 和端口擴展等方面存在著一定的缺陷,這就使之越來越成為通信的

2009-04-22 16:34:43 1602

1602 隨著超深亞微米工藝的發展, IC設計能力與工藝能力極大提高,采用SoC(System on Chip)將微處理器、IP核、存儲器及各種接口集成在單一芯片上,已成為目前IC設計及嵌入

2009-06-20 10:36:20 990

990

基于PCI IP核的碼流接收卡的設計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

摘要:門控時鐘技術一直以來是降低芯片動態功耗的有效方法,文章結合片上系統(SOC)的結構特性和設計特點,分析已有的各種門控時鐘技術的優缺點,指出這些缺點是SOC設計中嚴重障礙,隨后抽象出IP核工作模型,提出了僅用非常簡單的邏輯就可以方便應用于IP核

2011-02-23 13:53:11 36

36 本文介紹的基于Wishbone總線的UART IP核的設計方法,通過驗證表明了各項功能達到預期要求,為IP核接口的標準化設計提供了依據。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 4199

4199

FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 FPGA的IP核設計技術的系列資料,大家可以收集看下,這些都是我看過過濾后留下的,感覺不錯,希望對大家有幫助

2015-11-30 17:49:01 6

6 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

的接口標準,因此,開發統一的IP核接口標準對提高IP核的復用意義重大。本文簡單介紹IP核概念,然后從接口標準的角度討論在SoC設計中提高IP核的復用度,從而簡化系統設計和驗證的方法,主要討論OCP(開放核協議)。 圖1 OCP工作原理示意圖 圖2 讀/寫操作

2017-11-06 11:30:08 0

0 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10746

10746 采用IP核的設計方法,將外設組件互連標準(PCI)總線接口與具體功能應用集成在一個FPGA上芯片, 提高了系統的集成度。在對PCI IP核進行概述的基礎上,介紹了IP核的設計方法,實現了PCI總線

2017-11-17 12:27:03 7056

7056

本文包含兩部分內容:1)AXI接口簡介;2)AXI IP核的創建流程及讀寫邏輯分析。 1AXI簡介(本部分內容參考官網資料翻譯) 自定義IP核是Zynq學習與開發中的難點,AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。 使用Verilog調用

2018-05-28 11:42:14 38569

38569 對于IP核輸出數據的解析最好的工具就是其自帶的仿真文件,里面既將接收的數據進行了解析,又將發送給IP核的數據進行了封裝,這對于了解數據結構和協議是十分有幫助的,以太網如此,pcie、ram、fifo等其它IP也如此,我們只需將ip自帶的仿真文件改為我們自己的邏輯即可,接口連接并不變。

2018-07-09 14:07:00 4234

4234 AD的IP核哪里有?

2018-10-06 15:37:29 469

469 自定義sobel濾波IP核 IP接口遵守AXI Stream協議

2019-08-06 06:04:00 4566

4566 IP核可以兩種形式提供給客戶:軟核和硬核。兩種方式都可使客戶獲得在功能上經過驗證的設計。軟核也被稱為可綜合內核,需要由客戶進行綜合并在其SoC上實現。而硬核已完全實現(完成了版圖設計),可直接用于

2021-01-07 07:32:00 3668

3668

用于便攜式IP核的WISHBONE1片上系統(SoC)互連結構是一種靈活的設計方法,可用于半導體IP核。其目的是通過緩解片上系統集成問題來促進設計重用。這是通過在IP核之間創建一個公共接口來實現的。這提高了系統的可移植性和可靠性,并縮短了最終用戶的上市時間。

2021-01-19 15:23:59 21

21 片上系統SoC( system on chip)是ASIC( application specific integrated circuits)設計方法學中的新技術,是指以嵌入式系統為核心,以IP核復用技術為基礎,集軟、硬件于一體,并追求產品系統最大包容的集成芯片。

2021-05-22 17:35:13 4248

4248

IP核目前的IP設計已成為目前FPGA設計的主流方法之一,應用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數據塊。IP核在SoC中的集成方式及應用場景,芯片設計中的IP核具有特定功能的可復用的標準性和可交易性,已經成為集成電路設計技術的核心與精華。

2021-10-01 09:08:00 3100

3100 基于ARM的IEEE802-11bMAC層協議IP核設計(通信電源技術206期)-文檔為基于ARM的IEEE802-11bMAC層協議IP核設計總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,

2021-09-17 15:11:32 4

4 面向物聯網(IoT)、移動和汽車SoC的領先半導體IP核提供商Arasan Chip Systems宣布立即供應MIPI Soundwire PHY I/O IP核。

2021-10-08 10:05:42 1762

1762 前提:各個IP核的初始化和配置過程確認正確。

2022-02-16 16:21:32 4815

4815

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7272

7272

電子發燒友網站提供《HDLC協議IP核的設計與實現.pdf》資料免費下載

2023-11-08 15:45:33 5

5 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

在創新加速的浪潮中,為更好地響應客戶群需求,芯驛電子 ALINX 推出全新 IP 核產品線,致力于為高性能數據傳輸和復雜計算需求提供高帶寬、低延遲的解決方案。發布的第一批 IP 核包括 10GBe

2024-10-30 11:53:16 1164

1164

在創新加速的浪潮中,為更好地響應客戶群需求, 芯驛電子 ALINX 推出全新 IP 核產品線 ,致力于為高性能數據傳輸和復雜計算需求提供 高帶寬、低延遲 的解決方案。發布的第一批 IP 核包括

2024-10-30 17:39:43 1459

1459

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5641

5641

3468

3468

2516

2516

10

10 18

18 8

8 24

24 8

8 20

20 8

8 14

14 21

21 22

22 13

13 47

47 21

21 0

0 47

47 10

10 2412

2412 1195

1195

1351

1351

1990

1990

1602

1602 990

990

912

912

36

36 4199

4199

3085

3085

0

0 10746

10746 7056

7056

17729

17729

38569

38569 4234

4234 3668

3668

21

21 4248

4248

3100

3100 4

4 1762

1762 2275

2275

1164

1164

1459

1459

5641

5641

電子發燒友App

電子發燒友App

評論