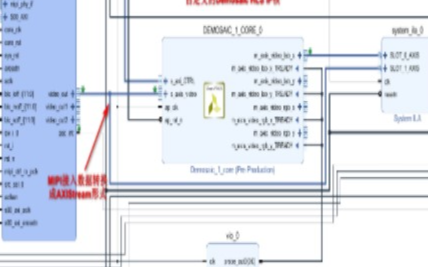

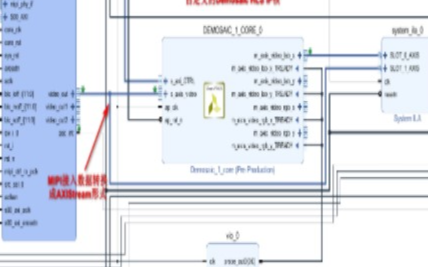

本章的實(shí)驗(yàn)任務(wù)是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進(jìn)行讀寫測試,讀寫的內(nèi)存大小是 4K 字節(jié)。

2025-11-24 09:19:42 3470

3470

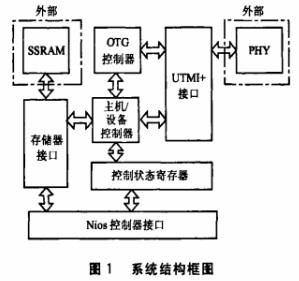

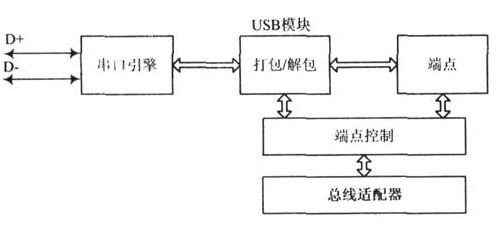

介紹了一款可配置的USB IP核設(shè)計,重點(diǎn)描述USB IP核的結(jié)構(gòu)劃分,詳細(xì)闡述了各模塊的設(shè)計思想。為了提高USB lP的可重用性,本USB IP核設(shè)計了總線適配器,經(jīng)

2010-07-17 10:39:51 3124

3124

本文介紹了LCD的通用驅(qū)動電路IP核設(shè)計,采用自頂向下的設(shè)計方法將其劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進(jìn)行描述,用FPGA實(shí)現(xiàn)并通過了仿真驗(yàn)證。該IP核具有良好的移植性,可驅(qū)動不同規(guī)模的LCD電路。

2014-05-13 10:09:35 3242

3242 本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數(shù)字電路中常用但比較復(fù)雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設(shè)計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數(shù)字電路中常用但比較復(fù)雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設(shè)計成可修改參數(shù)的模塊,讓其它用戶可以直接調(diào)用這些模塊,以避免重復(fù)勞動。隨著CPLD

2011-07-15 14:46:14

USB OTG的工作原理是什么?IP設(shè)計原理是什么?如何進(jìn)行IP模塊設(shè)計?USB OTG IP核有什么特性?如何對USB OTG IP核進(jìn)行FPGA驗(yàn)證?

2021-04-27 06:44:33

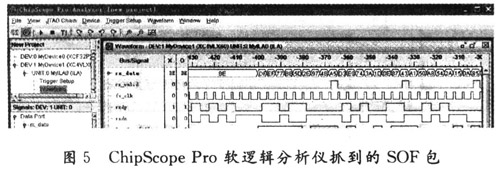

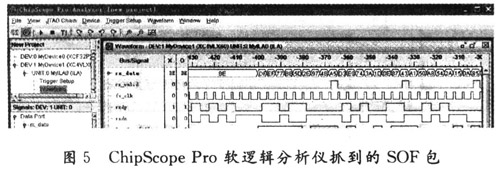

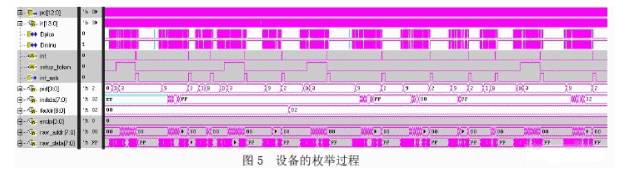

分不是硬件電路設(shè)計,所以就不再贅述了。 測試方案及測試結(jié)果測試電路設(shè)計了一個測試電路來驗(yàn)證USB 2. 0 接口電路功能的正確性,如圖5 所示。在原USB 2. 0 接口電路的基礎(chǔ)上,添加了MCU 接口

2019-04-12 07:00:12

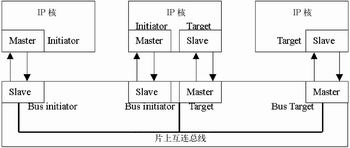

管理,具有高帶寬、高性能特性,適合于嵌入式處理器與高性能外圍設(shè)備、片內(nèi)存儲器及接口功能單元的連接。 根據(jù)兩種總線的特點(diǎn)和廣泛支持,為了給嵌入式SoC系統(tǒng)提供USB接口,需要設(shè)計USB和AHB間的橋接IP核

2019-05-13 07:00:04

USB_OTG_IP核中AMBA接口的設(shè)計與FPGA實(shí)現(xiàn)

2012-08-06 11:40:55

仿真,需要經(jīng)過綜合以及布局布線才能使用。

IP軟核的優(yōu)點(diǎn)在于其靈活性高、可移植性強(qiáng),允許用戶自配置。然而,其缺點(diǎn)在于對模塊的預(yù)測性較低,在后續(xù)設(shè)計中存在發(fā)生錯誤的可能性,有一定的設(shè)計風(fēng)險。

選擇合適

2024-05-27 16:13:24

劃分為幾個主要模塊,分別介紹各個模塊的功能,用VHDL語言對其進(jìn)行描述,用FPGA實(shí)現(xiàn)并通過了仿真驗(yàn)證。該IP核具有良好的移植性,可驅(qū)動不同規(guī)模的LCD電路。 關(guān)鍵詞:LCD;驅(qū)動電路;IP 引言

2012-08-12 12:28:42

本工程實(shí)現(xiàn)PCIE的8通道速率2.2GBps通信,并驗(yàn)證數(shù)據(jù)的正確性。本工程里已經(jīng)把PCIE部分做成一個封裝的模塊,對外提供的是fifo_wr(數(shù)據(jù)發(fā)送fifo)接口和fufi_rd(數(shù)據(jù)接收

2019-12-13 17:10:42

我用quartus II調(diào)用modelsim仿真fft ip核,仿真結(jié)束后我想驗(yàn)證下數(shù)據(jù)是否正確,結(jié)果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結(jié)果txt文件與用

2012-09-20 12:48:37

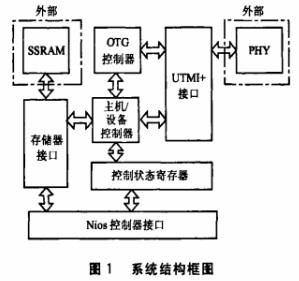

本文介紹一款USB OTG IP核的設(shè)計與實(shí)現(xiàn),該設(shè)備控制器可作為IP核用于SoC系統(tǒng)中,完成與主機(jī)控制器的通信,并能與普通的USB從設(shè)備進(jìn)行通信。

2021-04-29 06:47:00

隨著電路規(guī)模不斷擴(kuò)大,以及競爭帶來的上市時間的壓力,越來越多的電路設(shè)計者開始利用設(shè)計良好的、經(jīng)反復(fù)驗(yàn)證的電路功能模塊來加快設(shè)計進(jìn)程。這些電路功能模塊被稱為IP(Intellectual Property)核。

2019-11-04 07:40:53

對于深入學(xué)習(xí)使用FPGA的小伙伴們,特別是一些復(fù)雜的、大規(guī)模的設(shè)計應(yīng)用,適宜的IP核對開發(fā)能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調(diào)用這些模塊

2024-04-29 21:01:16

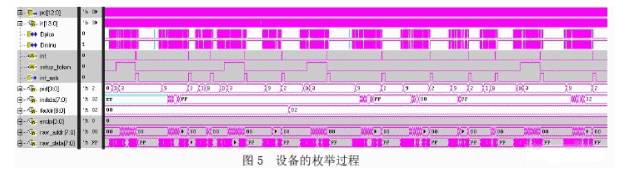

本文的應(yīng)用背景為某一工業(yè)測控系統(tǒng),該系統(tǒng)采用FPGA實(shí)現(xiàn)測量數(shù)據(jù)的采集和控制信號的輸出,通過定制PCI接口IP實(shí)現(xiàn)一個32位目標(biāo)設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

引言隨著半導(dǎo)體技術(shù)的發(fā)展,深亞微米工藝加工技術(shù)允許開發(fā)上百萬門級的單芯片,已能夠?qū)⑾到y(tǒng)級設(shè)計集成到單個芯片中即實(shí)現(xiàn)片上系統(tǒng)SoC。IP核的復(fù)用是SoC設(shè)計的關(guān)鍵,但困難在于缺乏IP核與系統(tǒng)的接口

2019-06-11 05:00:07

和TECHNOLOGY VIEW兩種原理圖,有利于關(guān)鍵路徑的尋找和分析,它還提供了許多功能強(qiáng)大的屬性參數(shù),但同時也增加了軟件使用的復(fù)雜性。 VHDL語言中例化的FPGA IP模塊(PCI核,雙端口RAM等

2019-04-17 07:00:06

基于 的XC3S1OOE FPGA的USB接口IP核模塊設(shè)計和驗(yàn)證

2020-12-25 06:48:04

。由于USB的廣泛應(yīng)用,國內(nèi)外眾多科研機(jī)構(gòu)和集成電路設(shè)計公司都把目光投向USB這項(xiàng)具有廣闊市場前景的技術(shù)。USB內(nèi)核(USB Core)是USB接口控制芯片的關(guān)鍵模塊,設(shè)計一個穩(wěn)定、高速的USB內(nèi)核更是

2018-11-21 11:30:06

開發(fā)板構(gòu)建視頻接口模塊等以利于調(diào)試和應(yīng)用。2 IP核的仿真與測試2.1 SoC的測試策略SoC芯片的測試比傳統(tǒng)的ASIC測試要復(fù)雜得多.全面的功能測試通常是不現(xiàn)實(shí)的? 目前常采用的策略是分別測試所有的電路

2021-09-01 19:32:45

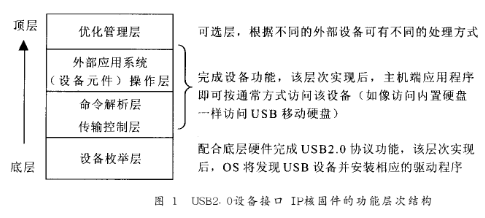

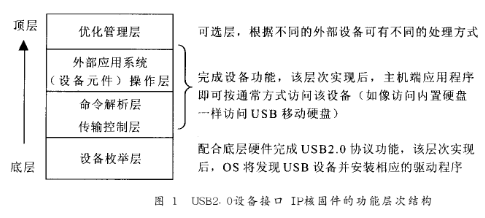

2.0協(xié)議外,還負(fù)責(zé)解釋設(shè)備子類協(xié)議,并實(shí)現(xiàn)對具體外部應(yīng)用系統(tǒng)(設(shè)備元件)的操作。 從硬件結(jié)構(gòu)分析,基于增強(qiáng)型8051MCU核的 USB2.0設(shè)備接口芯片(IP核)應(yīng)包括以下幾個模塊: (1)USB

2018-12-03 15:24:04

作為我項(xiàng)目的一部分,我需要將ADC與7系列FPGA接口,我有一個SelectIO?接口向?qū)У?b class="flag-6" style="color: red">IP核。但是,我的整個項(xiàng)目都在VHDL中,IPi得到的是Verilog。請指出我如何在我的VHDL頂級模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

HiI致力于研究在FPGA / Spartan 3E上連接打印機(jī)的研究項(xiàng)目。我可以獲得打印機(jī)接口IP核,或者沒有這樣的核心。如果可能,請幫助我。感激地以上來自于谷歌翻譯以下為原文HiI work

2019-07-04 06:32:58

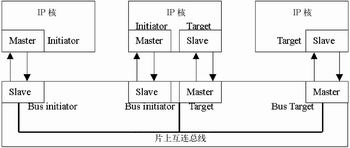

設(shè)計集成到單個芯片中即實(shí)現(xiàn)片上系統(tǒng)SoC。IP核的復(fù)用是SoC設(shè)計的關(guān)鍵,但困難在于缺乏IP核與系統(tǒng)的接口標(biāo)準(zhǔn),因此,開發(fā)統(tǒng)一的IP核接口標(biāo)準(zhǔn)對提高IP核的復(fù)用意義重大。本文簡單介紹IP核概念,然后從

2018-12-11 11:07:21

的定義是十分清晰的,讓各個獨(dú)立功能得到充分的驗(yàn)證,便于集成到SoC設(shè)計中。這些分系統(tǒng)的商品化IP產(chǎn)品已在進(jìn)行中。 模塊化IP結(jié)構(gòu)充分考慮了硬件/軟件設(shè)計、軟件應(yīng)用設(shè)計、以及快速原型的需要,因而便于

2012-12-19 10:13:14

最近需要做一個調(diào)研,求問各位論壇的大神,各種接口IP:PCIE、USB3.0、serdes等等的價格區(qū)間是多少啊,硬核軟核都可以,感謝不吝賜教

2020-01-20 17:59:06

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設(shè)計?

2021-04-28 06:10:23

VIEW兩種原理圖,有利于關(guān)鍵路徑的尋找和分析,它還提供了許多功能強(qiáng)大的屬性參數(shù),但同時也增加了軟件使用的復(fù)雜性。VHDL語言中例化的FPGA IP模塊(PCI核,雙端口RAM等)應(yīng)該不參與邏輯綜合,可以在

2019-05-08 07:00:46

(Intellectual Property)核。IP核由相應(yīng)領(lǐng)域的專業(yè)人員設(shè)計,并經(jīng)反復(fù)驗(yàn)證。IP核的擁有者可通過出售IP獲取利潤。利用IP核,設(shè)計者只需做很少設(shè)計就可實(shí)現(xiàn)所需系統(tǒng)。基于IP核的模塊化設(shè)計可縮短

2019-07-29 08:33:45

; PCI突發(fā)方式,133M字節(jié)/秒數(shù)據(jù)峰值傳送; 功能1,2 16C950高速串口IP核設(shè)計 完全VHDL源代碼設(shè)計,標(biāo)準(zhǔn)接口模塊化設(shè)計,可以移植到非PCI接口應(yīng)用; 軟件兼容16C550

2019-06-20 05:00:02

高速串口IP核設(shè)計完全VHDL源代碼設(shè)計,標(biāo)準(zhǔn)接口模塊化設(shè)計,可以移植到非PCI接口應(yīng)用;軟件兼容16C550串口,提供WINDOWS2000和XP驅(qū)動程序和測試程序;波特率范圍為300至115200

2019-06-12 05:00:07

開放核協(xié)議—IP核在SoC設(shè)計中的接口技術(shù)

2019-05-27 09:52:01

本文介紹了Tiger560B 處理器和w681511 音頻編碼器。并給出了USB 接口的IP 電話硬件設(shè)計與實(shí)現(xiàn)方法。關(guān)鍵詞:USB;端點(diǎn);編解碼器Abstract:Tiger560B processor and w681511 codec is presented

2009-06-13 13:24:21 35

35 探討了IP 核的驗(yàn)證與測試的方法及其和VHDL 語言在IC 設(shè)計中的應(yīng)用,并給出了其在RISC8 框架CPU 核中的下載實(shí)例。關(guān)鍵詞:IP 核;片上系統(tǒng);驗(yàn)證

2009-06-15 10:59:14 32

32 本文介紹一款USB 設(shè)備控制器IP CORE 的設(shè)計與實(shí)現(xiàn)。論文首先介紹了USB 設(shè)備控制器的設(shè)計原理,模塊劃分及每個模塊的功能。然后介紹了該IP CORE 在ModelsimSE 中的功能仿真及FPGA 驗(yàn)證結(jié)

2009-08-06 11:39:00 8

8 基于SOC(system on chip)技術(shù),利用VHDL 語言設(shè)計開發(fā)具有奇偶校驗(yàn)功能、數(shù)據(jù)位和波特率可調(diào)的通用異步串行通信接口IP 核。該IP 核內(nèi)置異步接收

2009-09-04 08:49:28 8

8 研究40Gb/s 交換IP 軟核的驗(yàn)證和測試方法。通過建立SDH 芯片驗(yàn)證平臺和SDH 芯片測試平臺, 實(shí)現(xiàn)IP 軟核的功能仿真、時序仿真和芯片性能測試。使得IP 軟核質(zhì)量優(yōu)良、性能穩(wěn)定, 適應(yīng)性

2009-11-27 14:30:16 6

6 本文討論了以IP(Intellectual Property)內(nèi)核為中心的開放式IP 核接口協(xié)議(OCP Open CoreProtocol),包括協(xié)議特性以及基于OCP 協(xié)議的SoC(System on Chip)中設(shè)計與驗(yàn)證等,并在此基礎(chǔ)上提出了基于OC

2009-12-04 11:39:53 14

14 本文討論了以IP(Intellectual Property)內(nèi)核為中心的開放式IP 核接口協(xié)議(OCP Open CoreProtocol),包括協(xié)議特性以及基于OCP 協(xié)議的SoC(System on Chip)中設(shè)計與驗(yàn)證等,并在此基礎(chǔ)上提出了基于OC

2009-12-14 10:48:11 21

21 USB設(shè)備接口IP核的設(shè)計:討論了用Verilog硬件描述語言來實(shí)現(xiàn)USB設(shè)備接口IP核的方法,并進(jìn)行了FPGA的驗(yàn)證。簡要介紹USB系統(tǒng)的體系結(jié)構(gòu),重點(diǎn)描述USB設(shè)備接口IP核的結(jié)構(gòu)劃分和各模塊的

2010-01-08 18:15:38 22

22 以 FPGA 技術(shù)為基礎(chǔ),以Verilog HDL 為載體,設(shè)計了遵守Wishbone 片上總線規(guī)范的IP 核接口,實(shí)現(xiàn)了片上系統(tǒng)的IP 核互聯(lián)。

2010-01-13 15:09:14 13

13 用硬件描述語言verilog HDL 設(shè)計實(shí)現(xiàn)了一種MCU&USB 設(shè)備控制器IP 核。論文首先簡要介紹了設(shè)計的背景,重點(diǎn)對自主研發(fā)的將MCU&USB 控制器集成于一個芯片的設(shè)計和研究分析。最后

2010-01-20 11:44:09 22

22 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設(shè)計,給出了該IP核的系統(tǒng)結(jié)構(gòu)以及各個子模塊的詳細(xì)設(shè)計方法,并對該IP核進(jìn)行了功能仿真、FPGA原型驗(yàn)證,可測性設(shè)計以

2010-07-17 16:20:22 21

21 介紹了用于IP核測試的內(nèi)建自測試方法(BIST)和面向測試的IP核設(shè)計方法,指出基于IP核的系統(tǒng)芯片(SOC) 的測試、驗(yàn)證以及相關(guān)性測試具有較大難度,傳統(tǒng)的測試和驗(yàn)證方法均難以滿足

2010-12-13 17:09:11 10

10 摘 要:本文介紹了IP核的概念及其在SoC設(shè)計中的應(yīng)用,討論了為提高IP核的復(fù)用能力而采用的IP核與系統(tǒng)的接口技術(shù)。 引言隨著半導(dǎo)體技術(shù)的發(fā)展,深亞微米工

2006-03-24 13:31:58 945

945

摘 要:本文介紹了IP核的概念及其在SoC設(shè)計中的應(yīng)用,討論了為提高IP核的復(fù)用能力而采用的IP核與系統(tǒng)的接口技術(shù)。

關(guān)鍵詞:SoC;IP核;

2006-06-07 11:11:53 2412

2412 I2C器件接口IP核的CPLD設(shè)計

根據(jù)單片機(jī)I2C串行擴(kuò)展的特點(diǎn),在EDA軟件MaxplusII的環(huán)境下,利用AHDL語言,建立IP核。此設(shè)計利用狀態(tài)機(jī)實(shí)現(xiàn),在給出設(shè)計的同時詳細(xì)說明IP核的建立

2009-03-28 16:21:35 1351

1351

USB2.0設(shè)備控制器IP核的AHB接口技術(shù)

介紹了USB2.0設(shè)備控制器IP核的AHB接口的設(shè)計。解決了雙時鐘域問題;實(shí)現(xiàn)了多事務(wù)DMA控制,減少了塊傳輸?shù)闹袛啻螖?shù);

2009-03-29 15:14:15 1990

1990

USB2.0接口IP核的開發(fā)與設(shè)計

隨著PC機(jī)和外圍設(shè)備的發(fā)展,傳統(tǒng)的并行接口和串行接口RS-232在易用性(即插即用) 和端口擴(kuò)展等方面存在著一定的缺陷,這就使之越來越成為通信的

2009-04-22 16:34:43 1602

1602 基于PCI IP核的碼流接收卡的設(shè)計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統(tǒng)的硬件設(shè)計方案及設(shè)計要點(diǎn)的分析。該設(shè)計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

MCU/USB設(shè)備控制器IP核的設(shè)計

1 引言

在傳統(tǒng)的計算機(jī)系統(tǒng)上常采用串口(如RS232)和并口連接外圍設(shè)備,但串口和并口都存在著通信速度 慢

2009-12-08 11:11:08 928

928

基于加密USB2.0接口芯片的設(shè)計及驗(yàn)證

0 引言

USB 總線因其具有高速度、即插即用、功耗低等特點(diǎn),深受廣大用戶的青睞。但USB 規(guī)范本身并未考慮數(shù)據(jù)傳輸時

2009-12-10 16:55:58 1125

1125 介紹了FreeARM7 IP核的基本概況及其接口特點(diǎn),以LPC2101為原型對該IP核進(jìn)行了擴(kuò)展。結(jié)合USB 1.1設(shè)備控制器IP核和自定制硬件邏輯,構(gòu)建了一種微控制器功能驗(yàn)證回路。

2011-04-06 11:41:13 2369

2369

本文介紹的基于Wishbone總線的UART IP核的設(shè)計方法,通過驗(yàn)證表明了各項(xiàng)功能達(dá)到預(yù)期要求,為IP核接口的標(biāo)準(zhǔn)化設(shè)計提供了依據(jù)。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 4199

4199

本內(nèi)容提供了基于 USB接口 的指紋檢測模塊設(shè)計

2011-06-29 16:26:07 31

31 文章采用TOP-DOWN 的方法設(shè)計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結(jié)構(gòu)模塊均實(shí)現(xiàn)了RTL級建模

2011-07-25 18:10:52 93

93 介紹了FreeARM7 IP核的基本概況及其接口特點(diǎn),以LPC2101為原型對該IP核進(jìn)行了擴(kuò)展。結(jié)合USB 1.1設(shè)備控制器IP核和自定制硬件邏輯,構(gòu)建了一種微控制器功能驗(yàn)證回路。在主機(jī)端開發(fā)了驗(yàn)證

2011-10-03 14:41:41 42

42 IP核驗(yàn)證平臺采用6層板PCB設(shè)計,使用獨(dú)立的外部時鐘同步芯片,可以為PCI及其它接口提供穩(wěn)定的零延遲時鐘系統(tǒng)電路,滿足PCI總線的時鐘要求,使驗(yàn)證平臺高速,穩(wěn)定,可靠的工作。

2012-01-17 14:02:19 2103

2103

介紹了SoPC(System on a Programmable Chip)系統(tǒng)的概念和特點(diǎn),給出了基于PLB總線的異步串行通信(UART)IP核的硬件設(shè)計和實(shí)現(xiàn)。通過將設(shè)計好的UART IP核集成到SoPC系統(tǒng)中加以驗(yàn)證,證明了所

2012-03-05 17:53:49 63

63 本文利用Altera公司的FPGA開發(fā)工具對皋于國產(chǎn)龍芯I號處理器IP核的SoC芯片進(jìn)行ASIC流片前的系統(tǒng)驗(yàn)證,全實(shí)時方式運(yùn)行協(xié)同設(shè)計所產(chǎn)生的硬件代碼和軟件代碼,構(gòu)建一個可獨(dú)立運(yùn)行、可現(xiàn)場

2012-04-21 15:22:01 8802

8802

無MCU的USB2.0設(shè)備控制器IP設(shè)計與驗(yàn)證

2013-09-23 17:18:17 40

40 Xilinx FPGA工程例子源碼:USB2.0 IP核源代碼

2016-06-07 14:13:43 35

35 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 基于IEEE1500標(biāo)準(zhǔn)的IP核測試殼的設(shè)計與驗(yàn)證_馮燕

2017-01-07 19:00:39 24

24 中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開發(fā)速度。 使用Verilog調(diào)用IP核 這里簡單舉一個乘法器的IP核使用實(shí)例,使用Verilog調(diào)用。首先新建工程,新建demo.v頂層模塊。 添加

2017-02-08 13:08:11 3085

3085

的接口標(biāo)準(zhǔn),因此,開發(fā)統(tǒng)一的IP核接口標(biāo)準(zhǔn)對提高IP核的復(fù)用意義重大。本文簡單介紹IP核概念,然后從接口標(biāo)準(zhǔn)的角度討論在SoC設(shè)計中提高IP核的復(fù)用度,從而簡化系統(tǒng)設(shè)計和驗(yàn)證的方法,主要討論OCP(開放核協(xié)議)。 圖1 OCP工作原理示意圖 圖2 讀/寫操作

2017-11-06 11:30:08 0

0 采用IP核的設(shè)計方法,將外設(shè)組件互連標(biāo)準(zhǔn)(PCI)總線接口與具體功能應(yīng)用集成在一個FPGA上芯片, 提高了系統(tǒng)的集成度。在對PCI IP核進(jìn)行概述的基礎(chǔ)上,介紹了IP核的設(shè)計方法,實(shí)現(xiàn)了PCI總線

2017-11-17 12:27:03 7056

7056

本文包含兩部分內(nèi)容:1)AXI接口簡介;2)AXI IP核的創(chuàng)建流程及讀寫邏輯分析。 1AXI簡介(本部分內(nèi)容參考官網(wǎng)資料翻譯) 自定義IP核是Zynq學(xué)習(xí)與開發(fā)中的難點(diǎn),AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

IP核 這里簡單舉一個乘法器的IP核使用實(shí)例,使用Verilog調(diào)用。首先新建工程,新建demo.v頂層模塊。

2018-05-28 11:42:14 38569

38569 對于IP核輸出數(shù)據(jù)的解析最好的工具就是其自帶的仿真文件,里面既將接收的數(shù)據(jù)進(jìn)行了解析,又將發(fā)送給IP核的數(shù)據(jù)進(jìn)行了封裝,這對于了解數(shù)據(jù)結(jié)構(gòu)和協(xié)議是十分有幫助的,以太網(wǎng)如此,pcie、ram、fifo等其它IP也如此,我們只需將ip自帶的仿真文件改為我們自己的邏輯即可,接口連接并不變。

2018-07-09 14:07:00 4234

4234 繼USB協(xié)議公布后,USB憑借其占用系統(tǒng)資源少、廉價、通用、可熱插拔等優(yōu)點(diǎn),成為通用的串行接口總線。當(dāng)前,絕大部分計算機(jī)外圍設(shè)備(如打印機(jī)、MP3、移動硬盤等)均采用USB接口。但隨著USB接口應(yīng)用的普及,基于USBl.x和USB2.O規(guī)范的USB接口逐漸暴露其缺點(diǎn)。

2019-06-03 08:02:00 2510

2510

信號層被編碼成NRZI位信息后傳送出去。數(shù)據(jù)傳輸層用來實(shí)現(xiàn)在USB主機(jī)端的客戶端驅(qū)動程序和設(shè)備端的功能接口之間傳輸有一定意義的信息,這些信息在協(xié)議層被打包成包格式。

2019-03-22 14:59:59 2021

2021 在WiFi模塊中,USB充當(dāng)著一個重要的角色。WiFi模塊上的數(shù)據(jù)傳輸有兩端:一端是WiFi芯片與WiFi芯片之間,通過無線射頻進(jìn)行數(shù)據(jù)傳輸;另一端則是WiFi芯片與CPU之間,通過USB接口進(jìn)行

2020-03-27 10:09:56 3503

3503 自定義sobel濾波IP核 IP接口遵守AXI Stream協(xié)議

2019-08-06 06:04:00 4566

4566 國內(nèi)對該領(lǐng)域的研究尚處于較初級的階段。本文對USB IP核設(shè)計方法,提出了一種USB2.0設(shè)備接口IP核固件的實(shí)現(xiàn)方案,該方案采用合理定義的層次模型并已被實(shí)現(xiàn),實(shí)驗(yàn)結(jié)果表明該方案具備良好穩(wěn)定性和可擴(kuò)展性的固件結(jié)構(gòu)。

2020-04-04 10:48:00 3182

3182

基于此.本文重點(diǎn)討論在IC設(shè)計過程中IP核的驗(yàn)證測試問題并以互聯(lián)網(wǎng)上可免費(fèi)下載的原始IP核資源為例.在與8位RISC架構(gòu)指令兼容的微處理器下載成功。

2020-07-16 08:49:42 4138

4138 前提:各個IP核的初始化和配置過程確認(rèn)正確。

2022-02-16 16:21:32 4815

4815

IP核的開發(fā)過程中,面臨著許多關(guān)鍵技術(shù),比如IP核的規(guī)格定義、基于接口的設(shè)計、IP核測試存取結(jié)構(gòu)標(biāo)準(zhǔn)、IP核的驗(yàn)證與打包等。對于IP核的驗(yàn)證,主要是建立參照模型和測試平臺,然后進(jìn)行回歸測試和形式驗(yàn)證

2022-06-13 15:54:10 1686

1686 ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 16

16 IP核的開發(fā)過程中,面臨著許多關(guān)鍵技術(shù),比如IP核的規(guī)格定義、基于接口的設(shè)計、IP核測試存取結(jié)構(gòu)標(biāo)準(zhǔn)、IP核的驗(yàn)證與打包等。對于IP核的驗(yàn)證,主要是建立參照模型和測試平臺,然后進(jìn)行回歸測試和形式驗(yàn)證

2022-06-10 11:50:16 1026

1026

IP核的開發(fā)過程中,面臨著許多關(guān)鍵技術(shù),比如IP核的規(guī)格定義、基于接口的設(shè)計、IP核測試存取結(jié)構(gòu)標(biāo)準(zhǔn)、IP核的驗(yàn)證與打包等。對于IP核的驗(yàn)證,主要是建立參照模型和測試平臺,然后進(jìn)行回歸測試和形式驗(yàn)證

2022-06-13 11:47:03 1087

1087

的不同模塊進(jìn)行實(shí)體/塊的仿真。前文回顧如何測試與驗(yàn)證復(fù)雜的FPGA設(shè)計(1)——面向?qū)嶓w或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執(zhí)行面向全局的仿真,而這也是測

2022-06-15 17:31:20 1373

1373

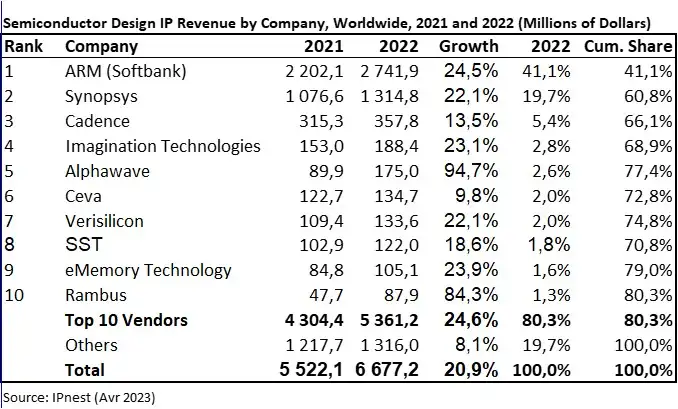

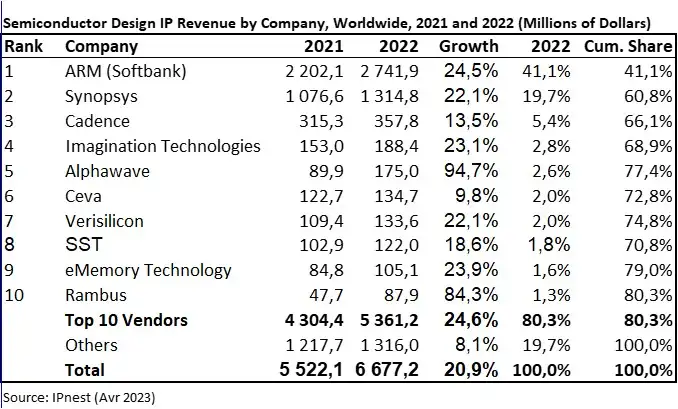

半導(dǎo)體IP通常也稱作IP核(IP core),此處IP也就是指知識產(chǎn)權(quán)(Intellectual Property)。IP核就是一些可重復(fù)利用的、具有特定功能的集成電路模塊,包含處理器IP、接口IP、物理IP、數(shù)字IP等。研究顯示,近5年,接口IP的增速高于處理器IP。‘

2023-09-15 15:59:13 1515

1515

電子發(fā)燒友網(wǎng)站提供《基于NiosII的USB接口模塊設(shè)計.doc》資料免費(fèi)下載

2023-10-27 09:49:42 0

0 西門子數(shù)字化工業(yè)軟件近日發(fā)布了Solido? IP驗(yàn)證套件,這是一套全面的自動化簽核解決方案,專為設(shè)計知識產(chǎn)權(quán)(IP)的質(zhì)量保證而生。此套件專注于為標(biāo)準(zhǔn)單元、存儲器以及IP模塊等提供高質(zhì)量保證,覆蓋從設(shè)計到簽核的全流程。

2024-05-28 10:38:56 1137

1137 本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數(shù)據(jù)>>測試verilogHDL>>TestBench仿真>>結(jié)果驗(yàn)證>>FFT運(yùn)算。

2024-11-06 09:51:43 5641

5641

。 圖源:億歐智庫 IP,即知識產(chǎn)權(quán)(Intellectual Property),在芯片設(shè)計中特指那些經(jīng)過驗(yàn)證的、可重復(fù)利用的電路模塊,也被稱為IP核。這些IP核如同芯片的基因片段,攜帶著特定的功能信息,如處理器核心、通信接口、圖像處理單元等。 另外,通過復(fù)用經(jīng)過驗(yàn)證的IP核,芯片

2024-11-28 10:09:39 1845

1845

電子發(fā)燒友App

電子發(fā)燒友App

評論