介紹了一款可配置的USB IP核設計,重點描述USB IP核的結構劃分,詳細闡述了各模塊的設計思想。為了提高USB lP的可重用性,本USB IP核設計了總線適配器,經

2010-07-17 10:39:51 3124

3124

本文討論了OCP-IP的協議與特點,設計了基于AMBA總線的OCP-IP接口,提出了一種IP自動封裝的方法,為IP核的集成和管理帶來極大的方便。

2012-01-09 11:11:08 3035

3035

1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 6783

6783

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

想請教各位前輩,wishbone在工作中很常用嗎?我最近在學關于這個的代碼,感覺很難懂,而時間又感覺不大夠用,需要重點攻擊, 所以想知道是否值得投入大量的時間去研究它。望各位前輩不吝賜教

2014-03-02 23:37:04

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

FPGA的IP軟核使用技巧主要包括以下幾個方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實現細節。它通常只經過功能

2024-05-27 16:13:24

FSL總線IP核及其在MicroBlaze系統中的應用

2015-01-18 21:01:20

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

我在用e203搭mcu,用wishbone總線實現mcu,看到e203有ICB轉wishbone模塊,但是8位的又和I2C總線有關,不太明白,我要的是32位的,應該怎么改,這部分轉換能說明一下,謝謝

2025-11-10 07:15:22

vivado中,怎么將e203內核源代碼封裝成ip核,并添加總線?

2025-11-10 07:22:49

剛剛接觸IP核做FFT,現在用的是FFTV9.0,已經建立了一個IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應該怎樣呢,謝謝指點。

2011-04-21 10:22:31

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

的《USB2.0的IP核(詳細verilog源碼和文檔).rar》。下圖是對應的Architecture。具體的文件列表如下圖所示:2、ahb轉wishbone的bridge具體項目參考百度網盤鏈接中

2022-11-23 14:47:33

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

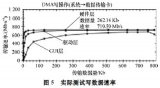

本文的應用背景為某一工業測控系統,該系統采用FPGA實現測量數據的采集和控制信號的輸出,通過定制PCI接口IP實現一個32位目標設備的PCI總線接口轉換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

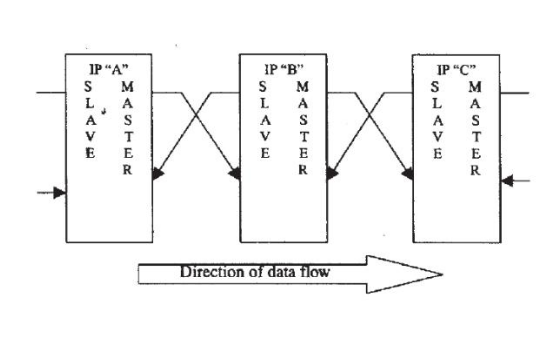

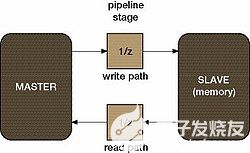

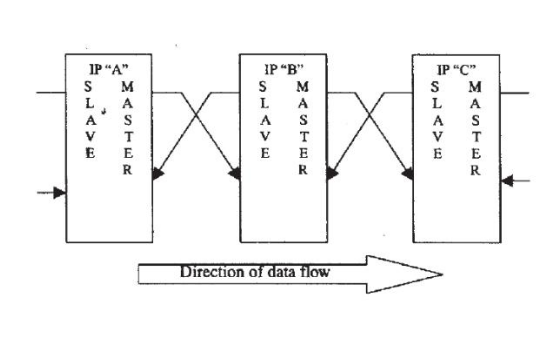

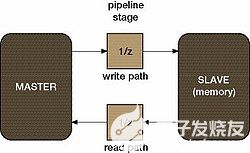

作Slave;下面的框圖代表封裝接口模塊;從Master出來并進入Slave的箭頭表示請求命令,從Slave出來并進入Master的箭頭表示響應;加黑的線段代表片上互連總線。兩個IP核通過接口通信

2019-06-11 05:00:07

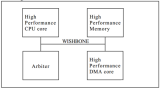

][tr][td] WISHBONE總線簡介WISHBONE總線規范是一種片上系統IP核互連體系結構。它定義了一種IP核之間公共的邏輯接口,減輕了系統組件集成的難度,提高了系統組件的可重用性、可靠性

2018-12-05 10:35:32

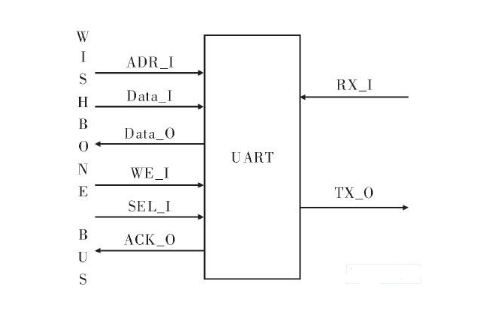

UART內部可劃分為哪幾個模塊?這些模塊有什么功能?基于APB總線的UART接口軟核該如何去設計?

2021-06-18 08:20:15

文章目錄一、 項目介紹:寫命令和寫數據總線介紹寫控制模塊框圖及波形代碼(1)連續寫(2)間隔部分測試代碼一、 項目介紹:本章節將會講解 A7 芯片內自帶的 DDR3 SDRAM 的 IP 核的寫時序

2022-02-08 07:08:01

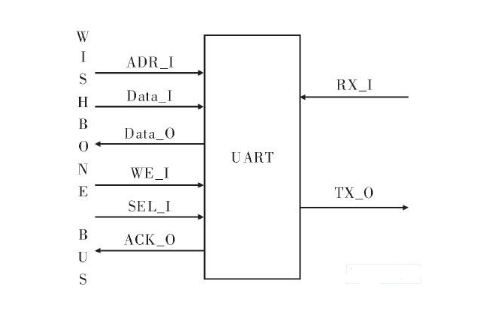

on Chip)是以嵌入式系統為核心,以IP復用技術為基礎,集軟、硬件于一體的設計方法。使用IP復用技術,將UART集成到FPGA器件上,可增加系統的可靠性,縮小PCB板面積;其次由于IP核的特點

2019-08-20 07:53:46

本文利用Altera公司的Quartus開發工具設計了一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。

2021-04-08 06:25:12

封裝接口模塊;從Master出來并進入Slave的箭頭表示請求命令,從Slave出來并進入Master的箭頭表示響應;加黑的線段代表片上互連總線。兩個IP核通過接口通信的過程是:作為Master

2018-12-11 11:07:21

所搭的IP軟核的通訊協議與總線支持的通訊協議(ICB)不同怎么轉換?

2023-08-17 07:05:35

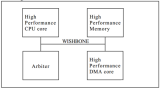

經過努力,開源軟核處理器OpenMIPS的實踐版終于新鮮出爐了,相對OpenMIPS教學版而言,OpenMIPS實踐版最大的特點是引入了Wishbone總線接口,組建了SOPC,包括SDRAM控制器

2014-01-06 17:41:21

三個問題:Linflexd_Uart_Ip_AsyncReceive 函數被阻塞(與接口的異步特性不一致)。測試的串口數據接收接口為Uart_AsyncReceive,調用了Linflexd_Uart_Ip

2023-03-21 07:20:15

介紹了基于MicroBlaze 軟核處理器的可編程片上系統結構。提出了一種LCD 控制器IP 核的設計方法。該控制器具有片上外設總線接口,和其它標準IP 核一起組成以MicroBlaze 為核心的片上系

2009-08-31 10:58:53 11

11 IC設計技術中的IP核互連:隨著IC 設計復雜度的不斷提高,在SoC 中集成的IP 核越來越多,基于片上總線的SOC 設計技術解決了大規模集成電路的設計難點,但是片上總線的應用帶來了

2009-10-14 12:50:23 8

8 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 20

20 本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能劃分設計,并對IP 核的仿真驗證,最后加入到NiosII 系統中。該I

2009-11-30 14:33:46 16

16 介紹了基于IP 的可重用的SOC 設計方法;選用MC8051 IP 核為核心控制器,自主開發了UART IP 核、I2C IP 核、USB IP 核,采用Wishbone 片上總線架構,集成了一個MCU 系統;同時設計了針對此MCU

2009-11-30 15:06:20 33

33 USB設備接口IP核的設計:討論了用Verilog硬件描述語言來實現USB設備接口IP核的方法,并進行了FPGA的驗證。簡要介紹USB系統的體系結構,重點描述USB設備接口IP核的結構劃分和各模塊的

2010-01-08 18:15:38 22

22 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 基于Avalon總線的可配置LCD 控制器IP核的設計

本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能

2010-02-09 09:34:44 27

27 基于ASIC/SoC的UART核的設計

摘要:本文描述了通用異步收發機UART(Universal Asynchronous Receive Transmitter)核的一種優化設計實現的設計流程。通過采用劃分功能模塊使結構直觀

2010-06-19 09:55:32 26

26 本文詳述了一種基于AMBA總線接口的IIC總線控制器IP核設計,給出了該IP核的系統結構以及各個子模塊的詳細設計方法,并對該IP核進行了功能仿真、FPGA原型驗證,可測性設計以

2010-07-17 16:20:22 21

21 設計了一款基于Avalon總線的8051MCU IP核。它支持MCS-51指令集,優化內部的結構,通過采用流水線技術、指令映射技術、指令預取技術、微代碼技術等極大的提高了IP核的工作速度,使IP

2010-09-28 10:44:06 54

54 在SOC設計日趨復雜化的今天,其發展的兩大挑戰是IP復用技術和IP互聯技術,研究IP復用技術對于業界具有重要的現實意義。SPI接口技術是一種高速、全雙工、同步的通信總線,

2010-10-20 16:21:54 47

47 摘要:基于IP可重用的設計方法,利用WISHBONE總線協議,把兩個已成功開發出的具有自主知識產權的THUMP內核在一個芯片上,實現了片上多處理器FPGA。開發重點是實

2009-06-20 15:29:35 839

839

本文討論了OCP-IP的協議與特點,設計了基于AMBA總線的OCP-IP接口,提出了一種IP自動封裝的方法,為IP核的集成和管理帶來極大的方便。

2011-05-19 10:07:43 13048

13048

本文簡要介紹了AMD 公司Am29LV160D 芯片的特點,并對WISHBONE總線作了簡單的介紹,詳細說明了FLASH memory 與WISHBONE 總線的硬件接口設計及部分Verilog HDL 程序源代碼。

2011-06-23 16:32:40 18

18 本內容寫出了CAN總線控制器IP核的代碼,并做出了詳細分析

2011-06-28 11:39:42 6798

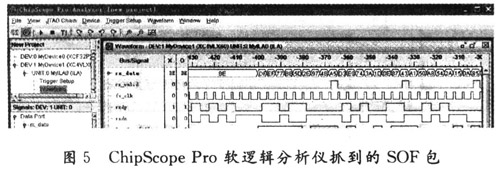

6798 本文所要驗證的8位RISC MCU IP核是與Microchip公司的8位MCU指令集完全兼容的IP核,采用哈佛總線結構,地址總線和數據總線分開,程序和數據分別存儲在程序存儲器和數據存儲器中。

2011-07-19 10:13:38 1988

1988

文章采用TOP-DOWN 的方法設計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結構模塊均實現了RTL級建模

2011-07-25 18:10:52 93

93 通用IO接口是Soc系統中非常重要的一種外圍端口.本文完成了一種基于WISHBONE總線的GPIO_W B拉制器的邏拜設計和物理實現.文中較其體地介紹了GPIO_W B核的體系結構以及WISHBONE接Q和DMA傳偷方式

2011-09-21 16:57:22 32

32 該設計采用了自頂向下的模塊化劃分和有限狀態機相結合的方法,由于其應用了標準的Wishbone總線接口,從而使微機系統與串行設備之間的通信更加靈活方便。驗證結果表明,這種新的架構

2011-10-19 15:01:54 27

27 根據Nios II處理器的Avalon總線規范,設計了一款面向步進電機的控制器IP核。該定制IP核采用軟、硬件協同設計的方法,功能符合Avalon總線的讀寫傳輸時序,具有完備的步進電機驅動能力。仿

2011-12-23 14:02:32 44

44 介紹了基于硬件描述語言Verilog HDL設計的SDX總線與Wishbone總線接口轉化的設計與實現,并通過Modelsim進行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調試。實驗

2012-01-11 10:21:21 25

25 介紹了SoPC(System on a Programmable Chip)系統的概念和特點,給出了基于PLB總線的異步串行通信(UART)IP核的硬件設計和實現。通過將設計好的UART IP核集成到SoPC系統中加以驗證,證明了所

2012-03-05 17:53:49 63

63 摘 要: 設計了一種基于NiosII處理器的片上系統(SoC),集成了Nios II處理器IP、PCI接口IP、網絡接口IP以及基于Wishbone總線的串行接口IP核、 CAN接口IP核等。系統具有可重配置、可擴展、靈

2012-10-18 16:50:29 14300

14300

本文以UART IP核和PLB總線為例,討論了在SoPC系統下UART IP核的設計方法,該方法對其他IP核的設計有一定的參考作用。

2013-01-08 09:03:27 6450

6450

FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 Xilinx FPGA工程例子源碼:PCI總線IP核(華為的商用)

2016-06-07 14:54:57 32

32 基于8051內核IP核的應用,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 18:18:32 1

1 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

基于AMBA與WISHBONE的SoC總線橋KBar控制器的設計_陳俊銳

2017-03-19 11:31:31 0

0 基于Avalon總線的非標準以太網控制器IP核設計_薛毅

2017-03-19 11:33:11 1

1 電子設計工程 基于FPGA的Flexray IP核通信的研究與實現

2017-08-30 16:08:32 13

13 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10749

10749 采用IP核的設計方法,將外設組件互連標準(PCI)總線接口與具體功能應用集成在一個FPGA上芯片, 提高了系統的集成度。在對PCI IP核進行概述的基礎上,介紹了IP核的設計方法,實現了PCI總線

2017-11-17 12:27:03 7056

7056

作者:薩其日娜 內蒙古魯電電力工程有限公司 摘要: 應用MicroBlaze軟核作為CPU的硬件平臺,在此平臺上設計了基于AXI總線的通用實時時鐘IP核。給出了創建IP核的過程和導入IP核的方法

2017-11-17 16:34:42 4415

4415 。本文介紹PCI Express 總線接口的設計方法,,并實現一個基于IP核的PCI Express 總線接口。

2018-07-18 10:35:00 2911

2911

DMA控制器是常見的總線設備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,Fujitsu等芯片

2017-12-06 13:41:59 4364

4364

大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 IP復用是片上系統時代的核心技術之一。由于IP核的設計千差萬別,它們要能夠直接連接,就要遵守相同的接口標準。在片上系統中,處理器核和所有外設通過共享總線互通互聯,因此這些IP核必須遵守相同的總線

2018-07-04 09:02:32 5769

5769

支持用戶定義的標簽。這些標簽可以用于為地址、數據總線提供額外的信息如奇偶校驗,為總線周期提供額外的信息如中斷向量、緩存控制操作的類型等。Wishbone規范只定義標簽的時序,而標簽的具體含義用戶可自行定義。支持用戶定義的標簽是Wishbone規范區別與其他片上總線規范的重要特征之一;

2018-07-06 08:07:31 3486

3486

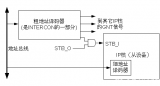

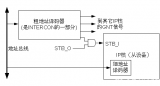

Wishbone部分地址譯碼的實現如圖26所示。對于圖中所示IP核,我們假設其只有4個地址,對應4組寄存器。地址譯碼器首先譯碼出其地址并給出選擇信號,該選擇信號與共享總線的STB_O相與輸入到IP核的STB_I。而地址總線的最低2位被直接連接到IP核,IP核再根據這兩位譯碼出當前操作選中的是具體哪個寄存器。

2018-08-05 08:44:59 4141

4141

在以上介紹的三種總線中,CoreConnect雖免費不過需要IBM 公司許可,ARM 沒有明確的正式說法,可能也會免費,而Wishbone 是絕對免費的。三種總線都是同步的總線,使用時鐘上升沿驅圖7 8-bit SLAVE輸出端口動和采樣信號。

2018-08-11 09:14:22 5307

5307

AD的IP核哪里有?

2018-10-06 15:37:29 469

469 JTAG UART是要自己添加的一個IP核,通常用來是實現PC和Nios II系統間的串行通信接口,它用于字符的輸入輸出,在Nios II的開發調試過程中扮演了重要的角色。

2019-09-30 07:02:00 3396

3396

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 用于便攜式IP核的WISHBONE1片上系統(SoC)互連結構是一種靈活的設計方法,可用于半導體IP核。其目的是通過緩解片上系統集成問題來促進設計重用。這是通過在IP核之間創建一個公共接口來實現的。這提高了系統的可移植性和可靠性,并縮短了最終用戶的上市時間。

2021-01-19 15:23:59 21

21 兩邊數據跨時鐘域無丟失的轉換。為滿足高速數據轉換的要求,采用了Wishbone總線,將多個IP核集成為VoIP網關系統。

2021-05-22 11:44:55 3136

3136

IP核目前的IP設計已成為目前FPGA設計的主流方法之一,應用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數據塊。IP核在SoC中的集成方式及應用場景,芯片設計中的IP核具有特定功能的可復用的標準性和可交易性,已經成為集成電路設計技術的核心與精華。

2021-10-01 09:08:00 3100

3100 Gowin UART Master IP 和 Slave 參考設計用戶指南主要包括功能簡介、

信號定義、工作原理、GUI 調用等,旨在幫助用戶快速了解 Gowin UART

Master IP 和 Slave 參考設計的特性及使用方法。

2022-09-15 10:11:24 0

0 電子發燒友網站提供《Gowin SDIO UART IP用戶指南.pdf》資料免費下載

2022-09-16 14:27:25 0

0 Wishbone B.3總線。以類似的方式,Altera引入了自己的互連方案,稱為Avalon Bus,SOPC Builder和Nios(II)系統就是圍繞該方案制造的。Xilinx 還推出了自己的總線,稱為片上外設總線與處理器本地總線 相結合。

2022-11-14 15:38:55 1899

1899

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7272

7272

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5641

5641

電子發燒友App

電子發燒友App

評論