本文深入介紹GMSL技術,重點說明用于視頻數據傳輸的像素模式和隧道模式之間的差異。文章將闡明這兩種模式之間的主要區別,并探討成功實施需要注意的具體事項。

2025-10-10 13:49:02 2004

2004

在LTE/LTE-A高速網絡即將普及和4K視頻浪潮的驅動下,業界都認為視頻數據將會成為移動網絡數據中最大的一個組成部分,如何解決高清視頻數據的傳輸速率和功耗問題已成為越來越大的設計挑戰。

2013-11-28 11:32:24 1531

1531 構成的傳輸數據的通道, 一般由數據線、地址線、 控制線構成。?Xilinx從6系列的 FPGA 開始對 AXI 總線提供支持, 此時 AXI 已經發展到

2020-12-25 14:07:02 6724

6724

在 AXI 基礎第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協議檢查工具。在本次第4講中,我們將來了解下如何使用它在 AXI4 (Full) 主接口中執行驗證(和查找錯誤)。

2022-07-08 09:31:38 4371

4371 在某些情況下,通過嗅探 AXI 接口來分析其中正在發生的傳輸事務是很有用的。在本文中,我將為大家演示如何創建基本 AXI4-Lite Sniffer IP 以對特定地址上正在發生的讀寫傳輸事務進行計數。

2022-07-08 09:35:34 1394

1394 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

2023-11-23 16:03:45 5162

5162

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號的時鐘并行視頻數據,即同步sync或消隱blank信號或者而后者皆有)轉換成AXI4-Stream接口形式,實現了接口轉換。該IP還可使用VTC核,VTC在視頻輸入和視頻處理之間起橋梁作用。

2025-04-03 09:28:14 2418

2418

,MicroBlaze 應用程序)可能會發生沖突。在 IP 定制時,我們能夠分配的空間需要注意。接下來創建一個以 Xilinx FPGA(S7-50 )為目標的小項目,項目主要演示AXI Virtual FIFO

2022-11-04 11:03:18

AXI-stream一般的數據傳輸過程如下: 1、首先slave將TREADY信號拉高,表示自己可以接收信號。 2、當master將TDATA,TKEEP,TUSER準備就緒之后,將TVALID拉高,傳輸開始

2021-01-08 16:52:32

下式排列,Table 1-5給出了用于傳輸視頻模式0、1、2、3、12的兩個像素的例子。像素數據被連續打包,像素之間沒有任何填充。當N*DW不是8的倍數整數時,視頻數據在msb上補零,如Figure

2022-11-14 15:15:13

我想知道AXI4流互連IP 2中True Round-Robin和Round-Robin仲裁方案之間的區別,特別是當所有從接口都不活動時。我已經參考了文檔PG085,并提到“如果所有從接口都不活動

2020-05-20 14:51:06

,只不過是專門針對視頻、圖像等二維數據的。除了上面的還有一個AXI-CDMA IP核,這個是由PL完成的將數據從內存的一個位置搬移到另一個位置,無需CPU來插手。上面的IP是完成總線協議轉換,如果需要

2022-04-08 10:45:31

我正在實施以下系統ChIP1(外設)最初廣告數據,CHIP2(中央)掃描,當ChIP2遇到廣告時,CHIP1發送掃描響應包并切換到掃描(Central),當ChIP2獲得掃描響應包時,它切換到廣告

2018-12-29 15:47:31

IP核均采用AXI總線接口,已經不再支持native接口。故做除法運算的重點從設計算法電路轉變成了調用AXI總線IP核以及HDL中有符號數的表示問題,極大降低了開發難度。以下就上述兩個方面進行探討

2018-08-13 09:27:32

各位大神,求指導!小弟的項目是這樣的,FPGA開發板對采集到的視頻數據做圖像處理,需要將處理后的視頻數據,傳輸給ARM,然后讓ARM通過以太網傳輸視頻數據。小弟想知道,如何實現讓FPGA開發板傳輸視頻數據給ARM開發板???求指導!謝謝

2014-02-26 10:04:25

of Active Video)和“有效視頻數據的結束”(End of Active Video)。SAA7113 對 SAV 和 EAV 數據格式的定義如表 7-1 所示。從表 7-1 中可以看到在完整的一幀圖像

2018-12-11 09:47:09

需要實現兩塊FPGA之間的8位并行數據傳輸,用什么握手協議比較好呢?想請問一下各位的建議。這兩塊FPGA使用的時鐘是36M的,同一個晶振產生。除了8位數據線外,兩塊FPGA之間還有10根可供使用的線。

2015-01-26 14:20:10

用的的是兩塊JZ2440的開發板,均與同一路由器相連,想通過網口通信在A板發布指令控制B板點燈,有人會嗎?(PS:在網上找過一些網口通信的收發程序,但都是PC機與開發板之間的通信,有試過將它們交叉

2018-05-05 14:24:26

大家好,我在進行兩塊TMS320F28069之間的SPI通信, 中斷機制。當主從的程序都只有RX和TX中斷時, 主從收發都正確。但是,當程序中加入采樣ADCINT1和EPWMINT1中斷后, 丟失

2018-10-08 17:00:44

兩塊芯片的連接應該沒有問題,SIMO、SOMI、SPICLK分別連上,從機的SPISTEA連到主機的控制GPIO口上,兩塊芯片也共地了,主機可以正常發送,從機無法接收,CCS在線調試時發現從機的SPI INT ENA位始終為0,SPIRXBUF中沒有數據。

2018-10-30 09:56:37

(STM32F407,以太網控制器為DP83848)。兩塊板子與電腦利用以太網通信都沒問題,但兩塊板子之間通信就走不通了(RJ45接口,綠燈不亮,應該是沒有建立連接)。。。代碼是直接用的例程的源碼,只是將兩塊板子的IP和端口號改了下并對應起來了問下各位大神,是哪個地方出問題了嗎?

2019-08-29 04:35:33

。散熱盤與芯片面的緊密接觸得到低的結溫(θjc)。為減少散熱盤與芯片間的熱阻,在兩者之間使用高導熱膠體。使得封裝內熱量更容易耗散。為更進一步改進散熱性能,外部熱沉可直接安裝在散熱盤上,以獲得封裝低的結溫

2018-09-11 15:20:04

處理功能,并通過高速接口把視頻數據傳輸給嵌入式微處理器,然后由嵌入式Linux系統完成網絡傳輸功能。 目前DSP與微處理器之間的高速通信方式有以下幾種:共享內存,此種技術對軟硬件的設計要求都非常高

2018-11-26 11:12:49

HPM6750的AXI內存分為XRAM0和XRAM1兩塊,但在用戶手冊16章系統內存映射表上這兩塊SRAM的地址是連續的,請問這樣設計是有什么特殊考慮嗎,如果程序連續讀寫這一段內存空間,跨越兩塊AXI SRAM時會不會有問題出現

2023-05-26 06:44:46

將兩塊空硬盤合并為“一塊”,掛載到指定目錄下,達到在一個目錄使用2塊硬盤所有空間的效果。

2019-07-18 06:46:08

,是汽車、儀表、醫療設備等視頻顯示的理想方案。該芯片組不僅可以在兩點之間傳送視頻信號,有時,人們還希望其同時傳送音頻信號。在本應用筆記中,我們將討論如何利用視頻信號的消隱期,通過控制信號通道將音頻數據傳送到顯示器。我們還將解釋怎樣把數字音頻數據轉換成模擬音頻信號,并給出了顯示面板端揚聲器驅動的系統結構。

2011-03-04 21:37:00

1AXI4總線協議

AXI4總線協議是由ARM公司提出的一種片內總線協議 ,旨在實現SOC中各模塊之間的高效可靠的數據傳輸和管理。AXI4協議具有高性能、高吞吐量和低延遲等優點,在SOC設計中被

2025-06-02 23:05:19

:(1)ACLK信號:總線時鐘,上升沿有效;(2)ARESETN信號:總線復位,低電平有效(3)TREADY信號:從機告訴主機做好傳輸準備;(4)TDATA信號:數據,可選寬度

2018-01-08 15:44:39

1.AXI簡要介紹

AXI全稱(Advanced eXtensible Interface),主要描述了主設備和從設備之間的數據傳輸方式。適合高帶寬低延時設計,無需復雜的橋就能實現高頻操作,能滿足

2023-11-03 10:51:39

數據傳輸量,突發長度,延遲,和總線事務。它有助于用戶在設計初期對AXI總線的瓶頸進行分析。 VARONIP包括可配置的主站或從站IP,提供可合成的FPGA IP。這使得將AXI總線作為硬件實現起來很容易

2020-11-02 16:54:39

AXI IP核,就必須先了解AXI接口。先介紹如下:1) AXI(Advanced eXtensibleInterface)協議主要描述了主設備(Master)和從設備(Slave)之間的數據傳輸方式

2016-12-16 11:00:37

申請理由:一直從事單片機的數據通信,想實現一次藍牙的數據傳輸功能。項目描述:兩塊板實現數據傳輸。比如,A板采集芯片內部溫度,通過藍牙發送給B板,經B板串口發送給上位機。

2016-01-19 16:05:58

之間的數據傳輸方式,在該協議中,主設備和從設備之間通過握手信號建立連接。AXI協議是一種高性能、高帶寬、低延遲的片內總線,具有如下特點:1、總線的地址/控制和數據通道是分離的;2、支持不對齊的數據傳輸

2020-10-22 15:16:34

請問主板從PCI接口獲取視頻數據后如何才能將其播放出來呢? 我的意思是采用PCI接口將外部視頻數據傳輸給CPU板,硬件上就是CPU通過PCI橋外擴PCI設備。軟件上是如何實現的呢?Windows下和VxWorks下的應用程序都是怎么做的? 感謝您的回答!

2015-04-27 14:38:53

嘗試使用兩塊ble-nano進行數據傳輸,8mhz的板子,最高波特率為34800,超過此波特率板子會燒。藍牙連接步驟:1.電腦接從機,NL和CR模式,輸入AT,得到ok,進入AT指令模式;2.輸入

2022-03-02 06:53:59

你好,我的FPGA接收視頻,視頻格式是1080p@ 60fps,YYY2。這是使用“32位從FIFO同步”傳輸視頻數據的唯一方法嗎?32位數據格式是什么?(D:7:0]?D [15:8]?D [23∶16]?,D [31:24]?我不知道如何分配我的視頻數據謝謝

2019-09-26 13:26:58

和 TDES960 解串器協同工作,通過單根超細線同時傳輸高分辨率視頻、控制信號和電源。這些設備有助于在傳感器和處理器之間建立鏈接,以聚合時鐘、未壓縮視頻、控制、電源和通用輸入/輸出信號,如圖 2

2021-09-07 11:25:18

1、兩塊fpga之間采用12根線連接,包括8根數據線,2根同步時鐘線,2根使能信號線。2、每塊fpga的引腳配置為[3:0]rxd(接受數據),rxc(接受時鐘),rxen(接受使能信號),[3:0

2021-08-18 16:58:35

嗨,我開始使用Vivado了。我正在嘗試配置從Dram讀取數據的自定義IP,處理它們然后將結果發送到Bram控制器。我想過使用AXI主接口制作自定義IP。但是,我不知道將AXI主信號連接到我的自定義邏輯,以便我可以從Dram讀取數據并將結果發送到Bram。謝謝。

2020-05-14 06:41:47

嗨,我打算通過GPIO在2塊FPGA板之間傳輸數據。為了傳輸數據,我知道我需要同步兩塊板。為了同步,我需要有一個共同的clk信號,如附圖所示?PN

2020-06-03 13:24:44

本文針對視頻數據流數據量大、實時性要求高的特點,采用流模式傳輸,將視頻采集數據通過DMA從存儲資源緊張的片內緩存區搬運至片外SDRAM幀緩沖區,實現圖像的高速傳輸。

2021-06-08 06:05:11

,所以也就沒有同時監測主機的接收buf,監視主機的接收buf與監視從機的方法是一樣的。四、調試過程需要注意的問題1、兩塊板子一定要共地。2、兩塊板子的MOSI與MISO不需要交叉連接。

2020-06-01 08:00:00

如果FPGA有兩塊qspi flash并行燒錄的功能,我在hardware manager里是否可以指定燒錄哪一塊flash呢?我想把我自己的數據燒錄到第二塊flash中,把bit流燒錄到第一塊

2023-04-18 19:45:55

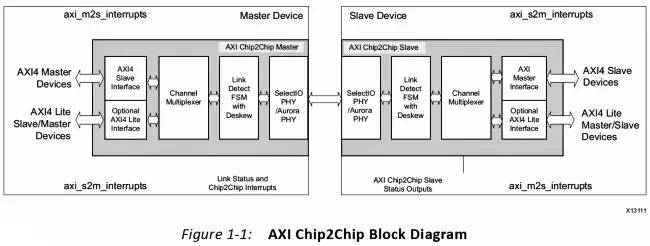

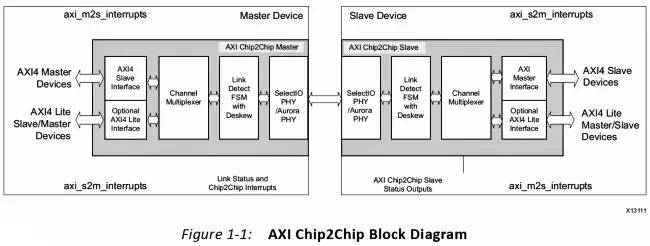

你好,我正在嘗試將Zynq UltraScale +模塊連接到AXI互連模塊,然后連接到一些AXI Chip2Chip模塊。 Chip2Chip塊的最大ID_WIDTH為12,但PS-> PL

2019-10-09 09:37:52

我在使用BF706進行開發,我想在代碼中對芯片進行標識,方式是在代碼中寫入芯片的chip id,這樣同樣的代碼燒到另一塊板卡就可以不能運行,但在手冊中沒有發現chip id對應的是哪個寄存器(雖然手冊中提到IDCODE 這個寄存器,但感覺這不是我想要的那個),哪位朋友知道的話幫忙回一下,

2023-11-29 06:23:36

各位大神,請你們給指導指導!小弟用兩塊mini板子,搞無線傳輸視頻,結果傳輸和接受到的圖像都不對,求指導???

2020-05-21 04:35:16

不做過多的講解(小伙伴可以自行下載AMBA總線協議規范或者翻看網絡上AXI4總線協議相關文章)。在SpinalHDL中,關于Axi4總線,包含了配置和實現兩塊內容,其內容均在

2022-08-02 14:28:46

,因為我知道所有AXI協議都有地址線。#2。 AXI-4 Stream協議是否與AXI-4 64位協議不同,如果是,兩者之間的主要區別是什么。謝謝

2020-04-28 10:00:42

兩塊相同的openharmony開發板之間可以通信傳輸數據嗎?如果可以辦法問對方是用什么實現呢?

2022-06-13 10:07:34

您好,我希望有人可以幫我確定我是否有可能做的事情。我在兩塊PCB上有兩個Artix-7 FPGA(參見下面的簡單草圖;我將左側FPGA稱為“FPGA1”,將右側FPGA稱為“FPGA2”)。我將數據

2020-08-28 06:22:25

有兩塊母版為EVAL-ADF7XXXMB4Z,主芯片為ADF7023BC,請問如何進行兩塊模擬嵌套板之間的無線通信?小白一只 請指教

2019-01-22 12:40:24

已將2塊WiFi模塊分別連接上2塊開發板,并透過AT指令配置,將RM04模塊設為STA模式、ESP8266模塊設為AP模式,想要在這兩塊開發板之間透過WiFi模塊傳輸數據,并將開發板分別接上USART連上PC確認數據,請問原子哥,要如何做才能使WiFi模塊傳送或接收數據啊?!

2019-02-12 22:37:35

我有兩塊STM32F429的板子,已經調通了,怎么測試這兩塊板子之間以太網的通信速率或傳輸速度?

2020-03-18 02:26:09

). Besides the CPU, the FPGA hosts an on-chip bus,bus controller, parallel port, RAM,video controller, and an externalSRAM contro

2009-07-27 17:37:39 97

97 在由ARM+DSP組成的嵌入式視頻處理平臺當中,需要將視頻數據從DSP端發送給ARM處理器,以便ARM將視頻數據傳輸到遠端服務器進行處理。提供了一種ARM與DSP雙核之間視頻數據通信的解

2010-10-25 16:09:06 38

38 什么是Chip

英文縮寫: Chip

中文譯名: 碼片

分 類: 其它

解 釋: 碼片是擴頻碼分多址移動通信中數據

2010-02-22 17:19:46 2620

2620 什么是cps (chip per second)

英文縮寫: cps (chip per second)

中文譯名: 碼片速率單位,每秒碼片

2010-02-22 17:23:29 2013

2013 摘 要:研究一種基于FPGA的多路視頻合成系統。系統接收16路ITU656格式的視頻數據,按照畫面分割的要求對視頻數據流進行有效抽取和幀合成處理,經過視頻編碼芯片轉換成模擬信號輸出

2012-09-12 17:18:31 99

99 Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口: 所以要把標準的VESA信號 轉為

2017-02-08 08:36:19 886

886

在變電站中,為了保證現場環境、設備外部狀況的全面監測,需要安裝大量的攝像頭進行晝夜監控,攝像頭采集的視頻數據量比其他的環境狀態數據、設備狀態數據量要大得多。數據信息的快速傳輸是站內狀態實時監控實現

2017-11-15 16:27:42 14

14 首先介紹了基于FPGA視頻采集系統的整體設計,對于采集和存儲過程中實時性和高效性的要求,分別討論了ITU656視頻解碼中需要從采集到的視頻數據中提取出有效視頻數據流,以及將其調整為符合VGA顯示

2017-11-17 01:28:55 4742

4742

提出,該協議專門針對視頻、音頻、數組等數據在片內通信設計。利用IP核進行嵌入式系統開發具有簡化設計、縮短開發周期等明顯優勢。

2017-11-17 08:58:01 5344

5344 iPhone X手機內部有兩塊電池 鳳凰科技訊 據phoneArena北京時間11月3日報道,對蘋果iPhone X手機的拆解顯示,L形電池并非鐵板一塊,而是由兩塊電池組成,總容量為2715毫安

2018-01-23 14:06:10 19860

19860

在本演示視頻中,請參閱兩個Xilinx FPGA之間以25 Gbps傳輸的數據模式,該模式跨越由Amphenol / FCI PCI Express CEM連接器和跟蹤卡組成的通道。

2018-11-28 06:53:00 4700

4700 芯片,構建一個集成NiosII軟核處理器、存儲器、I/O接口、自定義外設的可編程片上系統系統(System On Programmable Chip,SOPC)。利用FPGA高速并行處理能力,可同時對多路視頻數據進行視頻解碼,大大提高系統數據采集前端的處理能力。

2019-02-11 09:39:26 2549

2549

復旦大學微電子學院某國家重點實驗室內部教學視頻:基于ZYNQ FPGA與PC的IP設計與驗證方案。

關鍵詞:IP設計,IP驗證,AXI總線協議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 2714

2714

這里的基本概念是FPGA或者SoC中的具體化的IP和FMC-to-FMC線連接“消失”了,器件上的其他邏輯認為它是在與傳統的AXI端口對話,同時發送出去的和接收到的數據就像是它開創了一條連接線纜的道路一樣,在另一塊板的上器件中的AXI端口上出現。

2019-07-24 15:44:33 3799

3799

Xilinx Logicore IP直接數字合成器(DDS)編譯核心采用Axi4流兼容接口,實現高性能、優化的相位生成和相位-正弦電路。

2019-09-09 08:00:00 23

23 xilinx logicore?ip塊內存生成器(bmg)核心是一個高級內存構造函數,它使用xilinx fpgas中的嵌入式塊ram資源生成面積和性能優化的內存。用戶可以快速創建優化的內存,以利

2019-10-30 08:00:00 5

5 之前分享過的SPI通訊實例:STM32硬件SPI主從通信實例,是基于一塊STM32的兩個SPI通訊。如果要進行兩塊STM32之間的SPI通訊,需要注意一些什么呢?

2020-04-04 17:24:00 16410

16410 在FPGA程序設計的很多情形都會使用到AXI接口總線,以PCIe的XDMA應用為例,XDMA有兩個AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過

2020-10-30 12:32:37 5116

5116

Xilinx LogiCORE IP塊內存生成器(BMG)內核是一種高級內存構造函數,它使用XilinxFPGAs中的嵌入式塊RAM資源生成區域和性能優化的內存。

2020-12-09 15:31:00 22

22 1、兩塊fpga 之間采用12 根線連接,包括8 根數據線, 2 根同步時鐘線, 2 根使能信號線。

2021-02-25 09:58:00 47

47 AD8065-KGD-CHIP:知識良好的數據Sheet

2021-04-16 21:05:38 2

2 傳輸系統的組成結構如圖1所示,主要由兩塊ATCA板和一塊ATCA機箱背板組成。兩塊ATCA板上各放置一片FPGA作為串行鏈路的兩個端點,兩片 FPGA之間用兩對差分線進行連接,形成雙向各

2021-05-05 16:49:00 6265

6265

兩塊fpga之間采用12根線連接,包括8根數據線,2根同步時鐘線,2根使能信號線。

2021-04-27 09:35:16 50

50 ,它使用通用的AXI4接口在系統中移動或轉換數據,而不解釋數據。 這些基礎的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎構架IP。 ° AXI Register slices

2021-05-11 14:52:55 7870

7870

@[兩塊STM32之間 SPI DMA通信]這里講的是兩塊STM32F407板子的互相通訊,折騰了3天,終于比較清楚了,特此記錄。首先,硬件連接方式,主機

2021-12-14 18:51:39 79

79 AXI4S攜帶實際的視頻數據(無行場消隱),由主機和從機接口驅動,如Figure 1-1所示。

2022-11-14 09:15:25 2220

2220 某公司服務器,配備24塊FC硬盤,兩塊硬盤出現故障掉線,導致服務器上層的卷無法掛載。

2023-01-09 15:37:20 1420

1420 外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 11848

11848

電子發燒友網站提供《UltraScale FPGA收發器向導v1.7 LogiCORE IP產品指南.pdf》資料免費下載

2023-09-15 10:04:16 0

0 以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

AXI4和AXI3是高級擴展接口(Advanced eXtensible Interface)的兩個不同版本,它們都是用于SoC(System on Chip)設計中的總線協議,用于處理器和其它外設之間的高速數據傳輸。

2024-05-10 11:29:50 13096

13096

電子發燒友網為你提供()Abrupt Junction Varactor Diode Chip相關產品參數、數據手冊,更有Abrupt Junction Varactor Diode Chip的引腳

2025-07-09 18:34:50

你有沒有遇過這種情況:系統里有兩塊 FPGA 或者 FPGA + CPU + FPGA,需要它們之間高速、低延遲、可靠地互傳數據,甚至需要像訪問本地內存那樣訪問對方的寄存器與 BRAM?這時候傳統的 SPI / UART /以太網通信帶來的延遲、帶寬與開銷就顯得捉襟見肘。

2025-10-10 10:09:15 515

515

電子發燒友App

電子發燒友App

評論