引言

數字圖像處理技術廣泛地應用在信息處理領域,如何高效、靈活地將現實世界圖像數字化是信息處理的關鍵技術之一。本文基于FPGA技術設計了一個高速多路視頻數據采集系統。基于Altera Cyclone II芯片,構建一個集成NiosII軟核處理器、存儲器、I/O接口、自定義外設的可編程片上系統系統(System On Programmable Chip,SOPC)。利用FPGA高速并行處理能力,可同時對多路視頻數據進行視頻解碼,大大提高系統數據采集前端的處理能力。

SOPC系統是可編程片上系統,由單個芯片完成整個系統的主要邏輯功能,同時具有靈活的可重構特性。可根據實際應用中的不同需求裁剪、擴充、升級系統,并且軟硬件系統均可編程。NiosII軟核CPU的外設可由設計者自由配置,具有靈活且運行速度快的特點。

1 系統功能及特點

1.1 功能描述

本文所提出的系統以Altera公司CycloneII系列的EP2C70為核心,通過外接擴展板接入視頻信號,可同時采集處理2~6路視頻數據,將視頻數據解碼后提取出圖像區域的RAW DATA。SOPC系統通過自定義FIFO接口緩存數據,利用DMA技術將視頻數據搬移至存儲區域,供后續程序調用。

1.2 系統特點

本系統主要具有以下特點:

①采用硬件描述語言編寫的視頻解碼模塊可以高效地完成視頻編解碼工作,如果接入的視頻信號編碼格式不同,可以靈活重構每路視頻的解碼模塊,而不需要修改硬件設計。

②NiosII軟核CPU可以靈活地進行任務調度,配合Nios IDE軟件編程環境,可以方便的對視頻A/D采集芯片進行I2C總線配置。

③自定義FIFO接口緩存視頻數據,保證數據連貫性和準確性,FIFO的緩沖區的長度和數據寬度均可以定制,針對每一路視頻數據格式配置不同的FIFO緩沖區。

④采用DMA技術完成采集數據從SOPC外設到內存的搬移,減輕CPU的負擔。

2 實現原理及系統結構

2.1 系統總體框架

整個系統主要分為SOPC系統、多路視頻解碼模塊、視頻A/D芯片絹、SDRAM存儲器幾大模塊。SOPC系統和多路視頻解碼模塊均由FPGA可編程邏輯資源實現。SOPC系統通過自定義FIFO(Custom FIFO)緩沖來自多路視頻解碼模塊(Multi-channel Video Decoder Module)的數據,DMA完成數據從Custom FIFO到SDRAM的搬移工作,NiosII CPU通過Avalon總線對視頻A/D采集芯片、自定義FIFO接口模塊以及DMA控制器進行配置。系統總體結構如圖1所示。

SOPC系統以NiosII處理器為核心,通過AvaIon總線作為控制信號和數據傳輸中樞,NiosII軟核CPU及各類外設均掛載在Avalon總線上,本文SOPC系統中包括NiosII處理器、SSRAM、片上內存、JTAG控制接口、I2C總線控制接口、自定義FIFO接口、2個SDRAM控制器、DMA等。

2.2 視頻解碼模塊設計

視頻采集擴展板以TVP5150低功耗視頻A/D芯片為核心,采集模擬攝像頭信號,經A/D采樣后量化編碼成8位ITU-RBT.656視頻編碼格式輸出,輸出圖像分辨率為720x 480,像素時鐘為27 MHz。

視頻解碼模塊具有兩個功能:

①根據ITU-RBT.656并行接口規則,將TVP5150芯片輸出的數據流轉換成YUV422的圖像RAW DATA。

②對視頻分辨率進行調整,調整為640×480的分辨率,當數據為有效區域像素時發出數據有效信號,即對自定義FIFO的寫請求信號。

ITU-RBT.656協議中規定的信號中主要有3類:有效視頻區域數據信號、視頻定時基準信號、輔助信號。視頻解碼模塊第一部分任務關鍵是如何快速檢測ITU-RBT.656視頻數據流中視頻定時基準信號SAV/EAV。定時基準信號由4個字節的序列組成,其格式為FF0000XY,前3個字節FF0000為標志序列,最后一個字節XY表示該定時基準信號前后的數據行位于整個數據幀的位置及該定時基準信號類型。最后一字節XY每一位的含義如表1所列。

F、V、H是標志位,取值可為0或1。F位標識圖像數據是奇場數據還是偶場數據,V位標識當前數據是否為有效數據,H位標識該定時基準信號為SAV還是EAV。F、V、H標志位的取值與含義如表2所列。其中低四位P3~P0是由高4位經異或運算獲得,用于F,V和H值校驗和糾錯碼。 P3~P0的定義為:P3=VH,P2=FH,P1=FV,P0=FVH。

傳統序列檢測通常使用狀態機來實現。本設計創新的使用滑動窗法來快速檢測定時基準信號,這種設計程序結構清晰,在很大程度上減少了代碼量。根據ITU-RBT.656協議中定時基準信號的定義,聲明變量SAV=(Window==24’hFF0000)&(iData[4]==1’b0)。其中Window聲明24位寄存器,iData[7:0]是8位輸入信號,這里只取第4位。滑動窗更新時每次左移8位,低8位用輸入信號補齊。

解碼模塊的第二個功能在調整分辨率的時候引入Skip信號,當Skip信號有效時,該像素點數據跳過。本設計通過除法器控制Skip信號,將行像素計算器的輸出值作為除法器的分子,分母為9,skip信號由除法器余數控制,當余數為0時Skip信號有效。采用這種方案將行像素點由720轉換為640。

2.3 SOPC自定義FIFO接口

由于視頻輸入部分工作在27 MHz的時鐘頻率下,而NiosII軟核CPU為了獲取較高的系統處理能力,整個SOPC系統工作在100 MHz的時鐘頻率下。數據從外部進入SOPC系統的過程中由于時鐘的不匹配,極易造成數據重復或丟失,而異步FIFO正是解決這個問題的關鍵。采用異步FI FO作為數據緩沖接口,低速時鐘域接收來自視頻解碼模塊的Raw Data圖像數據,完成寫FIFO操作;高速時鐘域響應DMA控制器的讀請求,由DMA控制器完成讀FIFO操作。

多路視頻數據存儲接口模塊通過SOPC的自定義外設實現,本設計針對多路視頻數據采集,可根據每路視頻數據的不同格式單獨為每路視頻數據定制存儲接口。這種設計一方面降低了系統硬件結構的復雜度,另一方面保證每路數據獨立并行傳輸,提高數據采集的效率。自定義外設接口遵循Avalon總線協議,根據發起數據操作的方式不同,分為Master和Slave兩種,本系統的多路數據存儲接口模塊采用Salve模式。

自定義存儲接口模塊以FIFO IP Core為核心,通過與Avalon總線協議匹配,接收NiosII處理器的控制信號。該模塊利用QuartusII中Mega Wizard Plug-In Manager實例化FIFO IP Core,根據數據格式和系統資源綜合考慮,FIFO的數據寬度為8位,FIFO深度為1024。在這里保留FI FO IP Core的讀時鐘信號readclk、讀請求信號readrequest、8位讀取數據接口q[7:0]、8位寫入數據接口 data[7:0]、寫時鐘信號writec lk、寫請求信號writerequest以及FIFO空狀態信號rdempty。實例化后的FIFO模塊如圖2所示。

在SOPC自定義器件的配置過程中,根據我們所要實現的功能,FIFO的寫入端應為SOPC系統的對外接口,FIFO的讀取端應與Avalon總線掛接,并能被DMA控制模塊讀取。圖3為實例化后FIFO模塊作為自定義外設引入SOPC系統時的接口配置。

2.4 DMA控制器模塊

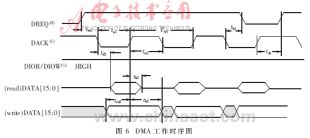

DMA控制器負責將自定義FIFO接口中的數據搬移至存儲區域,每路視頻數據源對應一個FIFO接口,每個FIFO接口配有一個DMA通道,各路視頻數據的解碼、存儲互不影響。SOPC系統所支持的DMA控制器IP Core傳輸模式有3種:

①存儲器到存儲器模式。這種情況下需要同時打開發送通道和接收通道,而且源地址和目標地址都是自增。

②存儲器到外設模式。這種情況下只要打開發送通道,而且源地址自增,目標地址固定。

③外設到存儲器模式。這種情況下只要打開接收通道,而且源地址固定,目標地址自增。

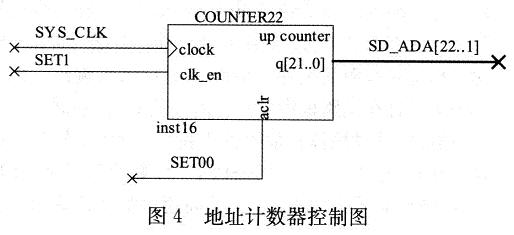

本系統設計中,DMA控制器工作任務是將自定義外設存儲接口的數據搬移至SDRAM內存中,所以采用第3種DMA控制器工作模式,即從外設到存儲器模式。這種工作模式下,源地址是自定義外設的地址,是一個固定地址。而目標地址是SDRAM存儲器地址,需要地址自增,在數據傳輸過程中,由DMA控制器自動完成目標地址自增操作。SOPC系統中的DMA控制器IP Core配置中的DMA寄存器的寬度大小,決定了一次DMA傳輸所能傳輸的數據量大小。本設計所需搬移的數據量為一幀圖像大小。

2.5 存儲空間設計

本系統方案中根據開發板的資源,將多路采集的視頻數據分別存儲在兩塊SDRAM中,SOPC系統中兩塊SDRAM的基地址分別為SDRAM_0_BASE與SDRAM_1_BASE。一塊SDRAM中存儲的每路視頻數據間隔RAM_PROTECT_SPACE的地址空間,DATA_SPACE定義了每路視頻數據存儲在SDRAM中的預留空間大小。由此可得第n路視頻數據在SDRAM中的存儲空間的地址。

起始地址:DATA_n_START_Addr=BASE_ADDRESS+RAM_PROTECT_SPACE。

結束地址:DATA_n_END_Addr=DATA_n_START_addr+DATA_SPACE。

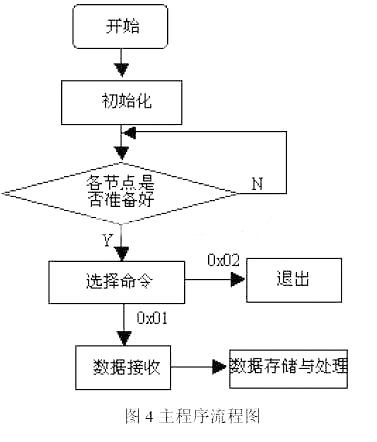

3 系統軟件設計

本方案軟件部分主要為TVP5150芯片初始化、DMA控制器的配置等。軟件結構流程如圖4所示。

4 實驗結果

為檢驗高速多路視頻數據采集系統的圖像采集效果,系統外接4路攝像頭同時采集圖像數據,在實際視頻數據采集過程中,多路視頻圖像顯示連貫流暢。將存儲在SDRAM中的圖像數據讀取后,通過后期融合算法,融合成環境平面圖像,實際多路圖像采集融合效果如圖5所示。

結語

本文基于FPGA設計了一種高速多路視頻數據采集系統,該系統通過外接視頻擴展板連接多個視頻攝像頭,通過在FPGA內部構建視頻解碼模塊,能夠對每路視頻數據并行解碼,提高要求實時性的多路數據采集的效率,并可在不更改硬件設計的前提下對編碼格式的數據采用不同的解碼模塊。SOPC系統的自定義FIFO接口能夠高速緩存視頻數據。通過DMA IP Core的使用,可減少Niosll軟核CPU讀取低速I/O接口數據所占用的時鐘周期,提高整個系統的工作效率。

電子發燒友App

電子發燒友App

評論