以下文章來源于OpenFPGA,作者碎碎思

你有沒有遇過這種情況:系統里有兩塊 FPGA 或者 FPGA + CPU + FPGA,需要它們之間高速、低延遲、可靠地互傳數據,甚至需要像訪問本地內存那樣訪問對方的寄存器與 BRAM?這時候傳統的 SPI / UART /以太網通信帶來的延遲、帶寬與開銷就顯得捉襟見肘。

什么是 Chip2Chip + Aurora 通信?

先說兩個組件:

Aurora 協議:Xilinx 提供的一種輕量級串行高速鏈路協議,適合 FPGA 間用高速串行收發器(GT 或 GTY / SERDES)連接。好處是延遲低、鏈路效率高。

Chip2Chip IP 核:Chip2Chip(AXI Chip2Chip)是一款由 Xilinx (AMD) 公司提供 的低引腳數、高性能AXI協議軟核IP,主要用于實現多設備SoC系統中的FPGA與SoC之間的高效通信。它通過通道復用、數據寬度轉換和支持多種物理層接口(如SelectIO和Aurora),能夠將AXI4和AXI4-Lite接口透明地橋接起來,可以讓一個 FPGA 向另一個 FPGA(或一個擁有對應 IP 的芯片)發起 AXI 或 AXI-Lite 總線訪問,就好像對方走在自己的地址圖里那樣,讀寫對方的內存或寄存器。

接下來我們就使用Chip2Chip + Aurora 實現一個簡單的DEMO。

實際用例

在這個例子里,用的是 Aurora 64b/66b,速率 10.3125Gbps。

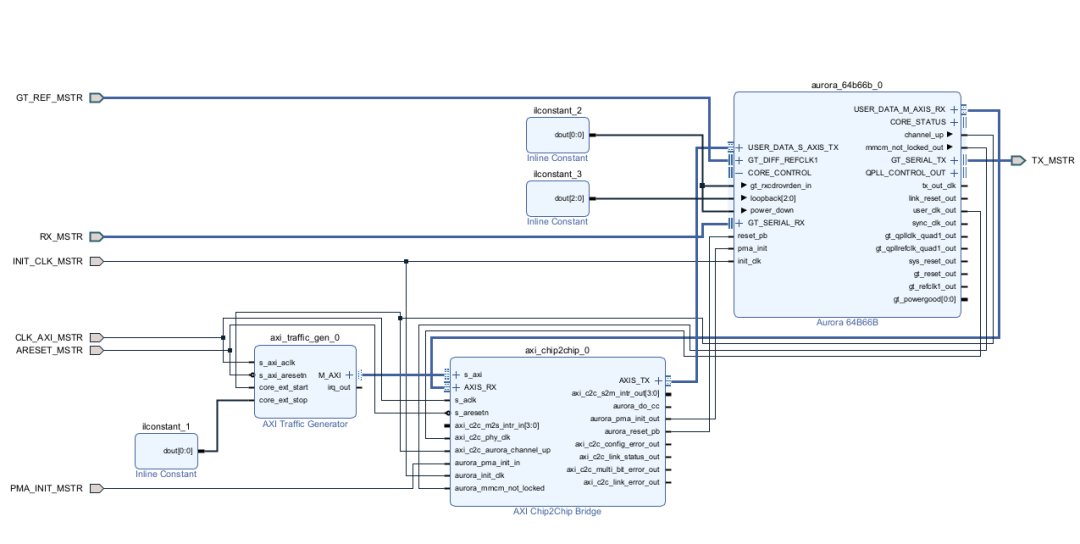

Chip2Chip 的 主端會對外提供 AXI 接口(如果啟用了,還會有 AXI-Lite 接口)。這樣一來,不管是片上的處理器、MicroBlaze,還是其他的 AXI master,都能通過這個 IP 發起讀寫操作,去訪問對端設備的 AXI 地址空間。

把 Chip2Chip IP 接到 Aurora 上其實很簡單,主要就是連上復位、初始化邏輯,還有一些狀態信號(比如 channel_up)。

在測試的時候,主端這邊掛了一個 AXI Traffic Generator 來制造讀寫流量,通過 Chip2Chip 傳過去。

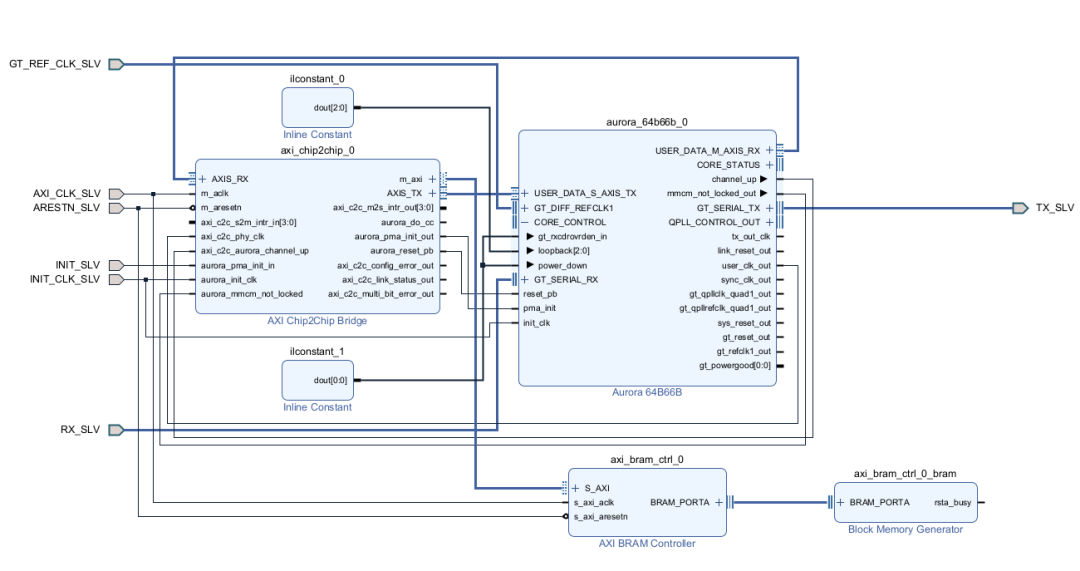

在 從端這邊,隨便接個 BRAM,讓它當成內存映射的目標。

時鐘這塊,兩邊的配置保持一致:初始化時鐘 50MHz,AXI 時鐘 200MHz,GT 參考時鐘用的是 156.25MHz。

這些子模塊(BDCs)最后會組合在頂層 IP Integrator 里,里面還會連收發器(GTs)和時鐘管理模塊(比如 Clocking Wizard 之類的)。

要注意的一點是:主從兩邊的地址映射一定要對齊,否則互相訪問時就會錯位。

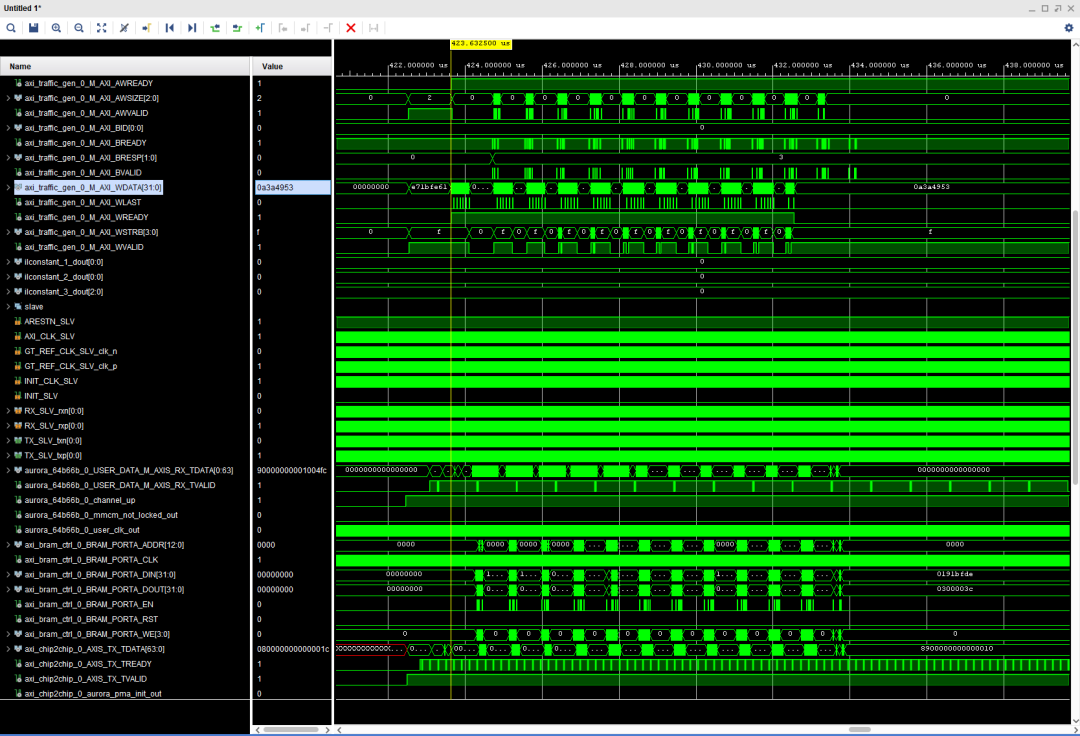

這種架構可以直接拿來仿真,不用真的接兩塊板子。仿真的時候你能看到:

先在主端這邊發起 AXI 寫操作

過一小會兒,就能在從端那邊看到對應的寫入

開源鏈接

https://github.com/ATaylorCEngFIET/mz616

小結

我比較喜歡這個 IP,原因是有些場景確實很實用。比如在工業應用里,經常需要不同模塊之間保持電氣隔離,這時候用光纖 + Aurora + Chip2Chip 就特別合適,可以很方便地在設備之間傳數據。

它讓我們不必把所有交互都扔給軟件來完成,也不必忍受傳統通信方式那么多中間層的折損。對于追求低延遲、高確定性、模塊化重用的工程項目,這一對組合確實能“提速不少”。

-

FPGA

+關注

關注

1662文章

22455瀏覽量

637916 -

以太網

+關注

關注

41文章

6087瀏覽量

181297 -

cpu

+關注

關注

68文章

11305瀏覽量

225516 -

通信

+關注

關注

18文章

6419瀏覽量

140168 -

Xilinx

+關注

關注

73文章

2202瀏覽量

131580

原文標題:FPGA世界里的“芯片對芯片”通信:Chip2Chip IP 核帶來的效率提升

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

esp8266 FREERTOS 3.3中沒有提供CHIP_ID函數,怎么實現獲取CHIP_ID的功能?

Micro chip官網現在沒有DEMO源碼嗎?

CHIP1是如何知道掃描發生的?

Chip Monolithic Ceramic Capaci

LED CHIP IQC檢驗規范

使用Chip2Chip+Aurora實現一個簡單的DEMO

使用Chip2Chip+Aurora實現一個簡單的DEMO

評論