在 FPGA 開發(fā)過程中,燒寫bit文件和使用ILA進行調(diào)試是再常見不過的操作。但如果 FPGA 板卡被放在機房,或者通過PCIe插在服務器上,那么每次調(diào)試時我們都不得不帶著筆記本電腦跑去機房或服務器旁,接上 JTAG 線后才能進行調(diào)試,非常不便。

2025-06-05 16:41:28 2215

2215

在Vivado中,VIO(Virtual Input/Output)是一種用于調(diào)試和測試FPGA設計的IP核,它允許設計者通過JTAG接口實時讀取和寫入FPGA內(nèi)部的寄存器,從而檢查設計的運行狀態(tài)并修改其行為。VIO IP核提供了一個簡單易用的接口,使得用戶可以輕松地與FPGA內(nèi)部寄存器進行交互。

2025-06-09 09:32:06 3372

3372

基于FPGA vivado 17.2 的數(shù)字鐘設計

2018-06-08 09:41:47 11516

11516

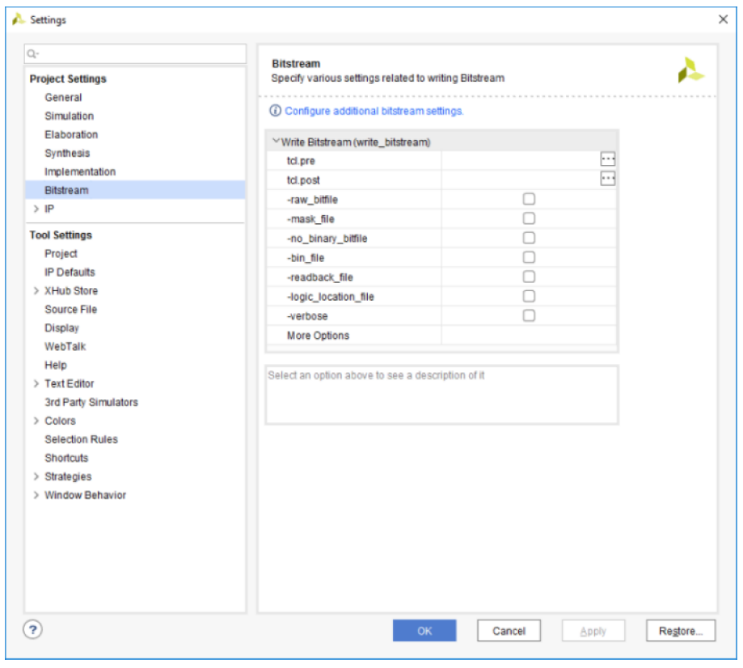

上篇主要是分享了Vivado編譯軟件遠程調(diào)試的方法。杰克使用Vivado軟件進行遠程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內(nèi)容是對使用Vitis軟件遠程調(diào)試的方法進行總結(jié)和分享。

2023-05-25 14:36:58 4231

4231

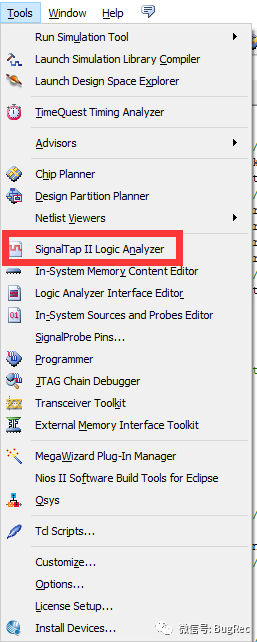

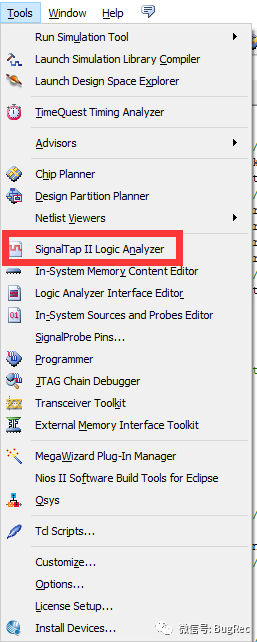

兩大主流廠商的軟件集成邏輯分析儀供使用,Altera的Quartus自帶SignalTap、Xilinx的Vivado自帶ILA邏輯調(diào)試工具。

2023-10-01 17:08:00 7441

7441

ILA Cross Triggering功能使得ILA核心之間、以及ILA核心與處理器(例如,AMD Zynq 7000 SoC)之間可以進行Cross Trigger。這個功能在你需要在不同時鐘域的兩個ILA核心之間觸發(fā),或者在處理器和ILA核心之間執(zhí)行硬件/軟件跨觸發(fā)時非常有用。

2023-11-30 10:17:59 2422

2422

在硬件調(diào)試時,經(jīng)常需要用 ILA 采集一些 FPGA 內(nèi)部或者對外的初始化信號,然而在下載完 Bitstream 后立即采集這些變化稍縱即逝的信號,比如在 1uS 內(nèi)手動觸發(fā) ILA 采集信號,以

2024-02-23 09:45:49 1990

1990

調(diào)試,即Debug,有一定開發(fā)經(jīng)驗的人一定會明確這是設計中最復雜最磨人的部分。對于一個龐大復雜的FPGA工程而言,出現(xiàn)問題的概率極大,這時如果沒有一個清晰的Debug思路,調(diào)試過程只能是像無頭蒼蠅一樣四處亂撞。

2025-03-04 11:02:19 1758

1758

`基于FPGA的在線系統(tǒng)調(diào)試概述本文節(jié)選自特權(quán)同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》(特權(quán)同學版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA

2015-09-02 18:39:49

This application note covers key methods of debugging FPGAs along with technologies that reduce the number of pins needed for debug.

2019-08-08 12:24:46

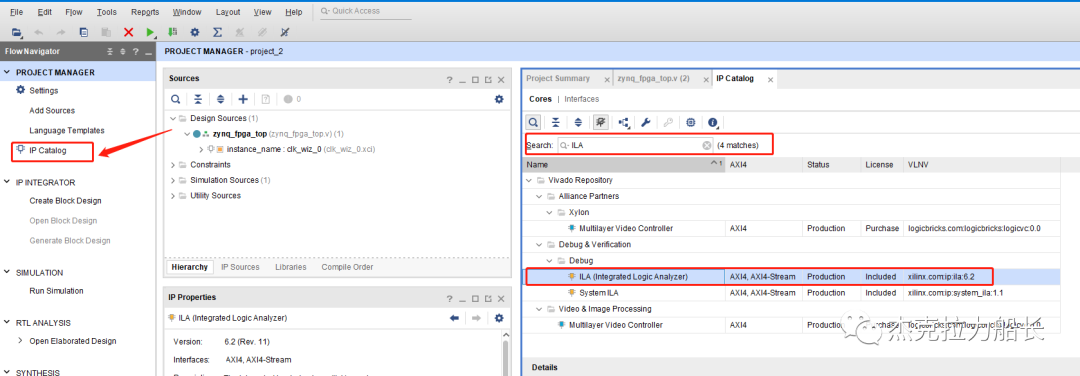

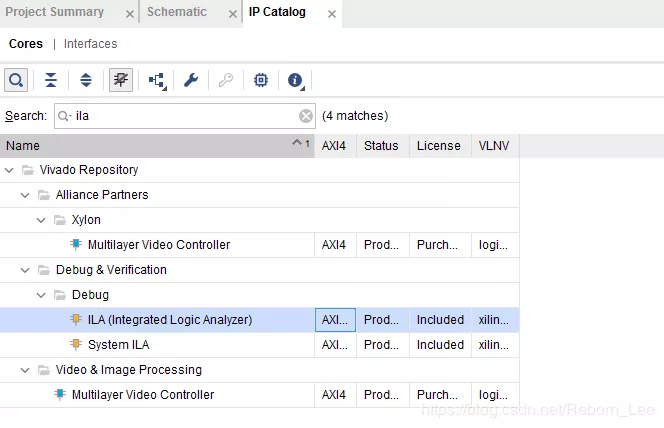

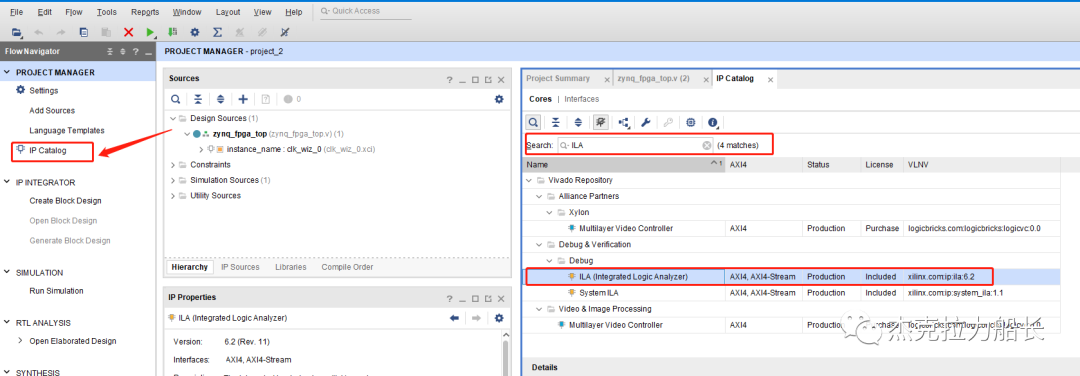

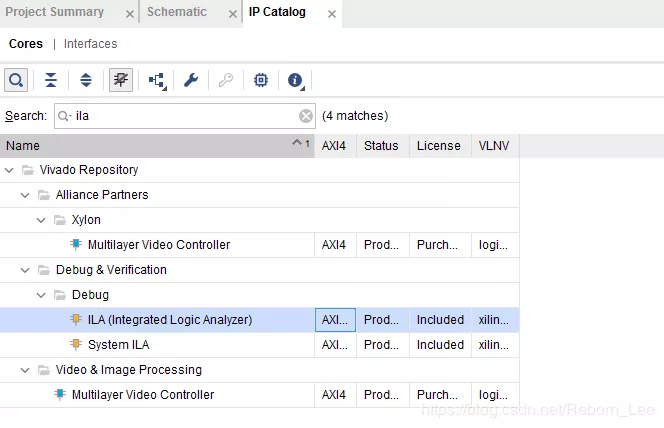

我們在調(diào)BUG的過程中單純利用引腳輸出中間變量的方法可能比較困難,因此我們在實際的開發(fā)過程中使用了ILA內(nèi)嵌式邏輯分析儀來進行內(nèi)部信號的捕捉和觀察。

1、在E203的 vivado工程中打開IP

2025-10-29 08:03:17

當我有一個ILA核心存在時,我的設計通常會失敗,我在程序框圖中標記了網(wǎng)絡上的調(diào)試。我注意到當Vivado使用調(diào)試向?qū)薷膞dc文件時,存在這種約束set_property

2018-10-29 14:12:56

在vivado中生成比特流,下板子同時用ILA抓取[5:0]}state和[2:0]count兩個信號,不知道為什么count信號一直是常量,如下圖,,但是代碼中功能是每進入一次狀態(tài)9即對count加1,而從ILA看,是可以進入狀態(tài)9的,如下圖,,希望大神指教。

2017-08-16 11:22:05

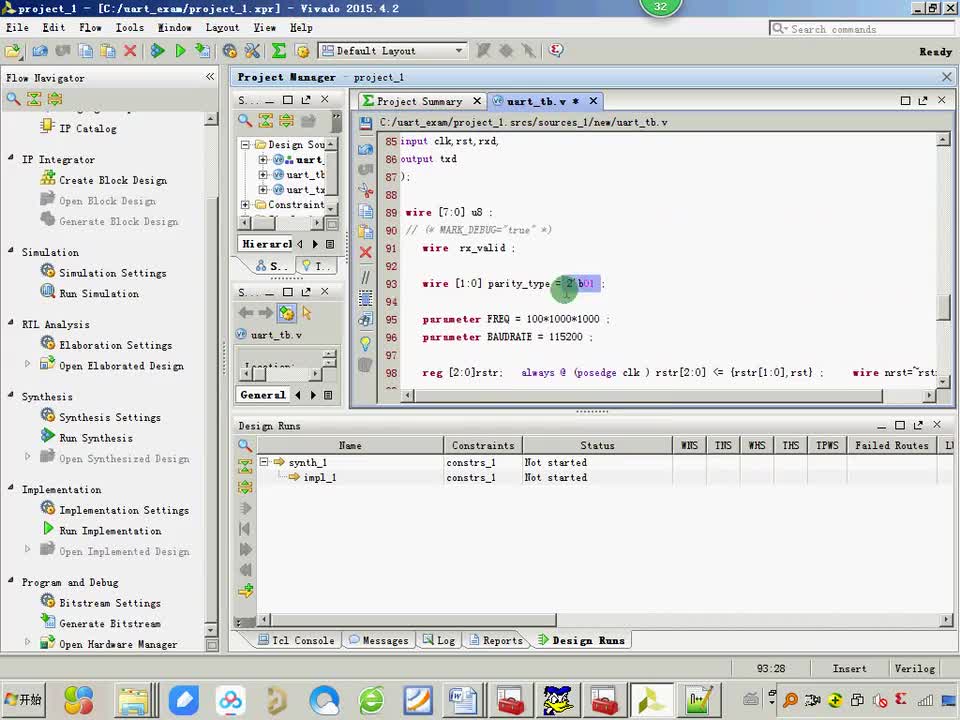

出發(fā)信號,然后設置觸發(fā)值,重新運行后,能夠定位到觸發(fā)值。2,方法2-在代碼中添加綜合屬性,實現(xiàn)在線調(diào)試。I 去掉ila_0的實例化。小技巧,可以選擇多行,然后右擊,選擇Toggle Line

2023-04-06 21:48:03

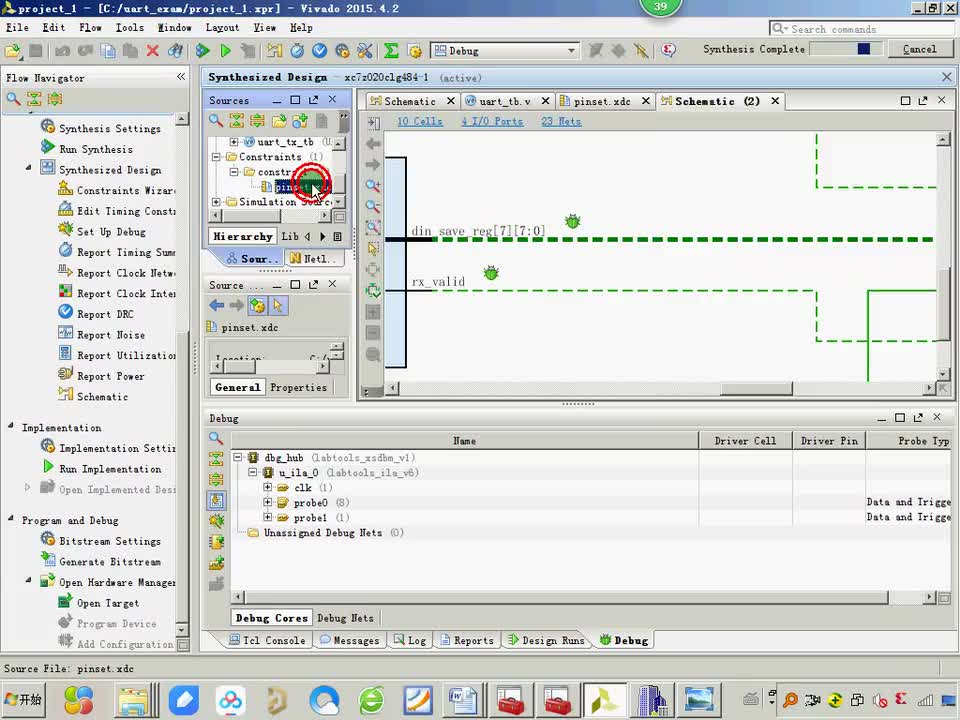

,確認無誤后直接點擊finish即可,如下圖所示:在“Debug”子窗口中的“Debug Cores”選項卡中,可以看到Vivado已經(jīng)添加了ILA IP核,并且“Unassigned Debug

2023-04-17 16:33:55

在用Vivado實現(xiàn)某個工程時,功能仿真正確,時序滿足要求,比特流也能生成,但是在ILA調(diào)試和下板子時,無法得到正確的結(jié)果信號,請問各位大神可能是什么問題?

2017-12-11 11:10:47

在使用vivadao在線調(diào)試功能時,對需要抓的信號MARK DEBUG,調(diào)用了ILA測試核,添加了時鐘約束,但是總是顯示no nets matched的warning,最后燒到片子里界面沒有跳轉(zhuǎn)到在線調(diào)試界面,無信號,顯示沒有添加ILA,問題出在哪里呢?求大神解答

2015-06-08 11:19:27

DSP的CCS軟件在線調(diào)試,不僅能觀察數(shù)據(jù),還能在線修改參數(shù)值,我想問一下vivado在線調(diào)試有這個功能嗎,我看見debug好像只能在線觀察,我想把bit文件下載到板上,我不僅要觀察,還想在線改變一些參數(shù)值(不需重新編譯),vivado有這個功能嗎??急求,謝謝大家了!!!

2017-12-20 14:03:27

大家好,我在使用Arty(Artix 7 FPGA)進行調(diào)試時遇到了一些麻煩。背景:我使用ILA在Zybo(Zynq)和Nexys 4 DDR(也是Artix 7)上調(diào)試我的程序,一切正常。我

2020-08-26 15:20:18

of an implementation issue with Vivado. I am attempting to add debug cores to my design with ILA cores and probes.

2019-01-03 11:00:14

dbg_hub_CV.0文件夾甚至不存在,這可以解釋為什么我收到錯誤。有誰知道我為什么看到這個以及我能做些什么來繞過它?日志錯誤:錯誤:[Chipscope 16-212]處理Vivado調(diào)試IP時出現(xiàn)故障“c:/F

2018-11-13 14:18:54

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

請問GD32用Embedded軟件debug在線調(diào)試失敗可能是什么原因?

2024-09-27 07:13:28

MDK在線調(diào)試TQ2440,Debug后就直接全速運行了,我已經(jīng)設置了run to main(),求解

2015-03-23 16:44:02

簡介STM32支持連接調(diào)試器進行在線Debug調(diào)試,可以用于一步步的排查程序的錯誤STM32F1系列的Cortex-M3 支持兩種調(diào)試主機接口(debug host interface ) :第一個

2022-01-26 07:09:06

所有: 我在VC707主板上使用Vivado 2015.4中的ILA內(nèi)核時遇到問題。有時它被硬件管理員識別,有時不被識別。當硬件管理器識別出來時,我有時會收到數(shù)據(jù)已損壞的錯誤消息。 是否可以告訴

2018-10-31 16:15:41

的JTAG Chain和Debug Core,因此本文提出一種比較方便的調(diào)試方法來同時使用這兩個core:ILA通過analyzer查看,VIO通過TCL控制。使用步驟:使用CoreGEN生成VIO

2012-03-08 15:29:11

就跑非的,前面幾步還是可以正常走,走著走著就會跑飛了。3.工程A和工程B的代碼基本功能一樣。4.我的懷疑有兩點,一個是工程配置的問題,還有一點就是代碼不一致,引出的在線debug跑飛的情況。問題解決:1.我新建一個工程C,使用可以在線debug的A工程的代碼 ,結(jié)果是可以在線單步調(diào)試;2

2022-02-22 06:20:14

你好這是我第一次嘗試添加ILA來調(diào)試loigc。在Vivado我添加了ILA IP核 ila_0 ila_0_INST( .clk(sys_clk),//輸入線clk.probe0

2019-10-10 05:57:42

。結(jié)果是我可以使用prj A在板上進行調(diào)試,但是在使用prj B進行調(diào)試時失敗了。錯誤消息在圖中。圖示意圖顯示我將clk連接到ILA。圖debug_error顯示了HW調(diào)試中的錯誤消息。以上來自于谷歌

2019-03-27 09:56:05

最近我一直在使用vc709板來研究PCIe示例,然后我想用ILA IP調(diào)試核心.AndI就像視頻所說的那樣,在我創(chuàng)建比特流并打開之后調(diào)用插入調(diào)試核心到Design.But很難,Vivado給我一個

2020-07-27 14:28:58

2或4處的調(diào)試集線器。要確定用戶掃描鏈設置,請打開已實現(xiàn)的設計并使用:get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]。警告

2019-10-16 09:34:16

嗨,大家好,我目前正在創(chuàng)建一個PCIe接口卡,我正處于項目的調(diào)試階段。我試圖監(jiān)視用戶_clkrate的AXI突發(fā)。關(guān)于ILA核心和PCIe端點(在VC709上)我有一些問題。1.當我嘗試將

2019-09-25 09:26:14

hw_server以檢測用戶掃描鏈2或4處的調(diào)試集線器。要確定用戶掃描鏈設置,請打開已實現(xiàn)的設計并使用:get_property C_USER_SCAN_CHAIN [get_debug_cores

2020-08-17 10:04:52

仿真和生成mcs文件后運行的結(jié)果如下(仿真的結(jié)果和實際傳回的數(shù)據(jù)結(jié)果不同,并且相同的c程序前后兩次傳回的結(jié)果都不同),目前想用ila調(diào)試,看錯在那一步了,但ila一直不出波形,三種加debug的方法

2023-08-16 06:37:13

你好,我在合成后插入了調(diào)試核心。并生成了位文件。在對FPGA進行編程之后,我能夠看到ILA內(nèi)核和信號。但是無法觸發(fā),也無法看到波形。我在Ubuntu 14上使用Vivado 2014.4。有人遇到過這個問題?如果我得到一個帶有調(diào)試核心的小示例項目,那將會很棒。謝謝哈

2020-07-30 09:49:48

該板卡,直接使用Recent Targets,之前的配置應該保存在列表中。如下圖所示。

如下圖所示連接后,即可正常使用 Vivado。FPGA 器件可以使用 ILA 內(nèi)核進行編程和調(diào)試,就像在本地PC上操作一樣,同時獲得更強大的服務器處理器的綜合和實現(xiàn)優(yōu)勢。

2024-07-31 17:36:01

[Chipscope 16-119]實現(xiàn)調(diào)試核心u_ila_0 failed.ERROR:無法為u_ila_0生成核心。中止IP生成操作。錯誤:[Chipscope 16-218]嘗試從IP緩存

2018-10-26 15:10:15

大家好如果我想在ILA調(diào)試模式下看到顯示信號的幅度怎么辦?你覺得有可能在屏幕上看到嗎?例如,我在附加的圖片上標記了紅色箭頭和藍色箭頭。你認為我可以調(diào)整信號的幅度嗎? (如示波器)或調(diào)整ILA顯示

2019-04-11 08:37:24

因此,在最終解決了由許可證問題引起的最后2-3個問題之后,我又一次遇到了許可證問題。這次是使用ILA塊。沒有它,我理解我無法進行任何調(diào)試。我剛剛收到“未找到Vivado分析器許可證”的錯誤在我可以

2018-11-29 16:15:10

/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c 1概述基于Vivado的板級調(diào)試介紹,可以參考文檔《玩轉(zhuǎn)Zynq-基礎篇:基于Vivado的在線板級調(diào)試概述.pdf》。這里我們以zstar_ex54工程為例,對FPGA的在線邏輯

2019-10-28 11:14:02

1概述基于Vivado的板級調(diào)試介紹,可以參考文檔《玩轉(zhuǎn)Zynq-基礎篇:基于Vivado的在線板級調(diào)試概述.pdf》。這里我們以zstar_ex55工程為例,對FPGA的Virtual IO

2019-11-18 15:08:59

更加獨特的調(diào)試手段。在FPGA器件支持并且剩余邏輯資源足夠的情況下,設計者往往習慣于使用開發(fā)軟件提供的在線邏輯分析儀進行調(diào)試,如Vivado的ILA和QuartusII的SignalTapII,它們

2019-05-24 15:16:32

程序使用IAR軟件在線調(diào)試debug時提示“the debugging session could not be started,eiither the debugger

2024-04-26 06:41:00

斑梨電子樹莓派Pico RP2040官方原裝USB串口調(diào)試套件Raspberry Pi Debug ProbeRaspberry Pi Debug Probe是一個一體化的USB調(diào)試套件,提供所有

2023-02-25 10:48:18

什么是D-ILA投影技術(shù)

D-ILA(Direct-Drive Image Light Amplifier,直接驅(qū)動圖像光源放大器)技術(shù)。D-ILA技術(shù)在提供高分辨率和高對比度方面顯示了技術(shù)優(yōu)勢,

2010-02-05 10:42:23 945

945 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

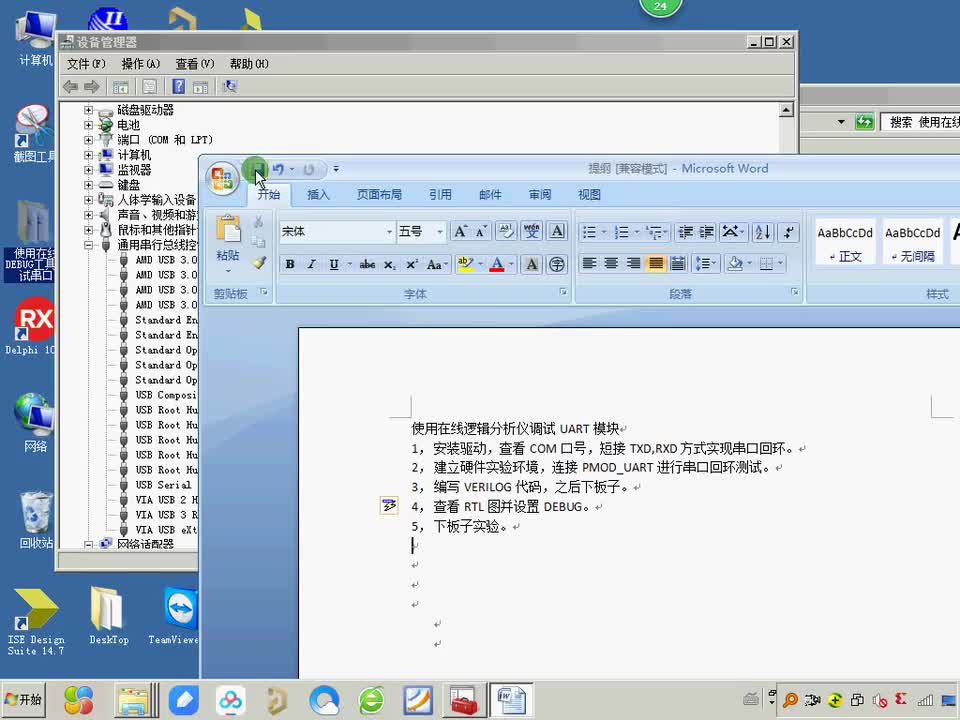

65 在ISE中稱為ChipScope而Vivado中就稱為in system debug。下面就介紹Vivado中如何使用debug工具。 Debug分為3個階段: 1. 探測信號:在設計中標志想要查看的信號 2. 布局布線:給包含了debug IP的設計布局布線 3. 分析:上板看信號。

2017-11-17 14:05:02 63651

63651

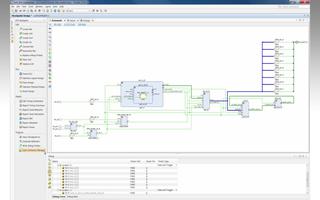

PL部分調(diào)試,作為PL DMA的控制APB總線,將其設置為Mark Debug,如下圖所示。綜合完成,不進行implemention,在綜合菜單下面找到“Set Up Debug”,進行ILA配置。

2017-11-28 15:46:26 8562

8562 本文檔內(nèi)容介紹了基于chipscope使用教程以及FPGA在線調(diào)試的方法,供參考

2018-03-02 14:09:49 9

9 FPGA設計中的信號連接到ILA核的時鐘和探針輸入如圖1。這些信號附加到探針輸入,以設計速度采樣,并使用片上塊RAM(BRAM)存儲。核參數(shù)指定探針的數(shù)量、跟蹤樣本深度和每個探針輸入的寬度。使用與FPGA的JTAG接口連接的自動實例化調(diào)試核心集線器與ILA核進行通信。

2018-08-04 10:29:00 2914

2914

其實這兒便很簡單了,可以直接在畫布上添加一個ILA核,再把想要的信號線連進來就行了呀,都不需要在代碼里定義這個ILA核。不過這樣做就說明你還沒能靈活的使用Xilinx的在線調(diào)試工具了,因為還有更簡單的辦法哈哈。

2018-11-14 10:47:56 7490

7490

了解使用Vivado 2016.3中引入的系統(tǒng)內(nèi)IBERT進行調(diào)試的好處,以及將其添加到設計中所需的步驟。

2018-11-20 06:43:00 6397

6397 了解使用Vivado 2016.1中引入的增量編譯流程進行調(diào)試的好處,以及在使用增量編譯實現(xiàn)時添加/刪除/修改ILA內(nèi)核所需的步驟。

2018-11-30 06:19:00 3483

3483

了解Vivado中的Logic Debug功能,如何將邏輯調(diào)試IP添加到設計中,以及如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進行交互。

2018-11-30 06:22:00 3889

3889 了解使用Vivado 2016.1中引入的ECO流程進行調(diào)試的好處,以及在ECO布局中替換ILA調(diào)試探針所需的步驟。

2018-11-29 06:01:00 4313

4313

了解如何使用Vivado在設備啟動時及其周??圍進行調(diào)試。

你也會學習

使用Vivado 2014.1中引入的Trigger at Startup功能來配置和預先安裝a

調(diào)試核心并觸發(fā)設備啟動時或周圍的事件......

2018-11-22 07:05:00 5047

5047 Vivado在使用A7芯片時,使用內(nèi)部邏輯分析儀時,在非AXI總線下最多只能綁定64組信號(例化一個或者多個ILA模塊,信號組數(shù)相加不能超過64),如果超過64組會出現(xiàn)錯誤。

2018-11-23 09:38:55 2045

2045 STM32F1系列的DEBUG調(diào)試功能需要配置嗎?

2020-03-01 13:57:43 4223

4223 說說STM32調(diào)試DEBUG相關(guān)知識

2020-03-06 15:23:22 5033

5033 FPGA的調(diào)試是個很蛋疼的事,即便Vivado已經(jīng)比ISE好用了很多,但調(diào)試起來依舊蛋疼。即便是同一個程序,FPGA每次重新綜合、實現(xiàn)后結(jié)果都多多少少會有所不同。而且加入到ila中的數(shù)據(jù)會占用RAM資源,影響布局布線的結(jié)果。

2020-03-08 17:35:00 12847

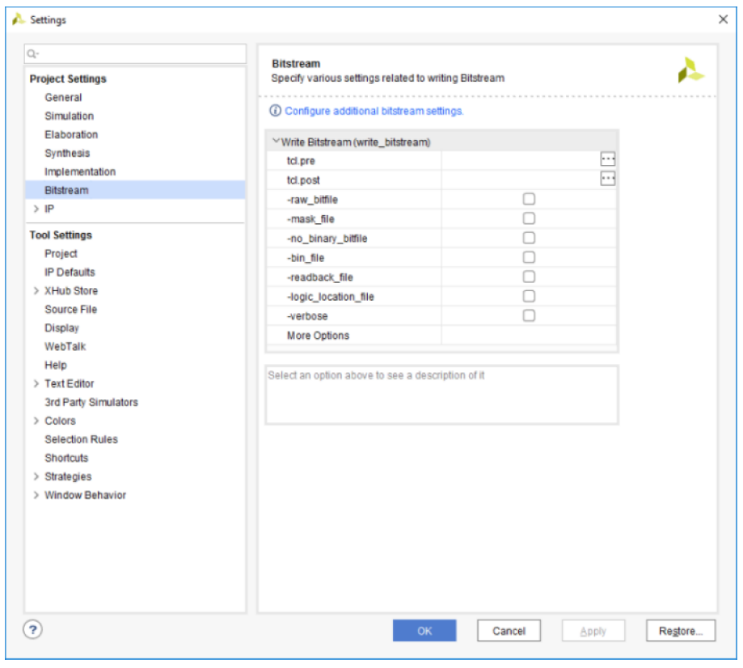

12847 Vivado中提供了多種Debug的操作方式,下面就來總結(jié)一下: 1. 代碼中例化ILA IP核 第一種,直接例化ILA IP核: 需要探測多少個信號,信號的位寬是多少,直接選擇即可: 下面界面可以

2020-11-11 17:07:13 11668

11668

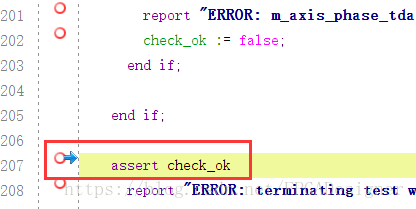

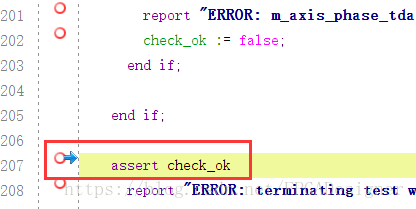

源代碼級別調(diào)試 Vivado Simulator提供了在仿真過程中debug設計的特性,通過為源代碼添加一些可控制的執(zhí)行條件來檢查出問題的地方。總的來說有三種調(diào)試方法: 1.使用Step逐行調(diào)試

2020-12-29 15:57:04 17560

17560

在線調(diào)試也稱作板級調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 5441

5441

集成邏輯分析儀 (Integrated Logic Analyzer :ILA) 功能允許用戶在 FPGA 設備上執(zhí)行系統(tǒng)內(nèi)調(diào)試后實現(xiàn)的設計。當設計中需要監(jiān)視信號時,應使用此功能。用戶還可以使用此功能在硬件事件和以系統(tǒng)速度捕獲數(shù)據(jù)時觸發(fā)。

2022-02-08 11:35:19 28930

28930

集成邏輯分析儀 (Integrated Logic Analyzer :ILA) 功能允許用戶在 FPGA 設備上執(zhí)行系統(tǒng)內(nèi)調(diào)試后實現(xiàn)的設計。當設計中需要監(jiān)視信號時,應使用此功能。用戶還可以使用此功能在硬件事件和以系統(tǒng)速度捕獲數(shù)據(jù)時觸發(fā)。

2021-01-22 07:52:04 20

20 不一致,從而出現(xiàn)Bug。一種debug的方式就是用FPGA工具提供的ILA模塊(xilixn在ISE中叫:chipscope),來實時抓取FPGA內(nèi)部數(shù)字信號的波形,分析邏輯錯誤的原因,幫助debug。 ILA

2021-08-09 14:12:05 19554

19554

配置VScode編譯、調(diào)試STM32(二)Cortex-Debug插件

2021-12-01 12:21:04 17

17 調(diào)試STM32時能下載程序但調(diào)試模式(debug)無法進入main函數(shù)問題 今天調(diào)試程序時,突然發(fā)現(xiàn)程序不正常,然后給板子插上JTAG調(diào)試器,連上電腦,進入Debug模式,竟然無法進入主程序,連

2021-12-01 13:36:07 17

17 【流水燈樣例】基于 FPGA Vivado 的數(shù)字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 27

27 就跑非的,前面幾步還是可以正常走,走著走著就會跑飛了。3.工程A和工程B的代碼基本功能一樣。4.我的懷疑有兩點,一個是工程配置的問題,還有一點就是代碼不一致,引出的在線debug跑飛的情況。問題解決:1.我新建一個工程C,使用可以在線debug的A工程的代碼 ,結(jié)果是可以在線單步調(diào)試;2

2021-12-27 19:31:35 6

6 學習STM32開發(fā),肯定少不了debug調(diào)試這一步驟。那么,本文帶你了解一下這個調(diào)試相關(guān)的知識。

2022-02-08 16:02:48 9

9 昭曉Fusion Debug?是一款基于創(chuàng)新架構(gòu)的全面調(diào)試系統(tǒng),建立在芯華章全新的、自主開發(fā)的調(diào)試數(shù)據(jù)庫之上,并由創(chuàng)新的設計推理引擎和高性能分析引擎提供動力,可輕松進行信號連接跟蹤和根本原因分析

2022-05-23 17:06:06 1966

1966 主題 1:VIVADO 開發(fā)流程和資源評估? 學習目標:? 1、掌握 VIVADO 開發(fā)流程 2、掌握 VIVADO 的在線調(diào)試流程 3、掌握資源評估的方法 學習內(nèi)容:? 1、開發(fā)流程:新建

2022-06-21 06:50:44 619

619 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調(diào)用(Block Memory)。

2023-02-02 10:14:01 5002

5002 Xilinx LabTools工具是Xilinx FPGA單獨的編程和調(diào)試工具,是從ISE或Vivado中獨立出來的實驗室工具,只能用來下載FPGA程序和進行ILA調(diào)試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 9161

9161 Xilinx被AMD收購的事情把我震出來了,看了看上上一篇文章講了下仿真的文件操作,這篇隔了很久遠,不知道該從何講起,就說說FPGA的在線調(diào)試的一些簡單的操作方法總結(jié)。

2023-06-19 15:52:21 2703

2703

之前的文章介紹了FPGA在線調(diào)試的方法,包括選定抓取信號,防止信號被優(yōu)化的方法等等。

2023-06-20 10:38:48 9670

9670

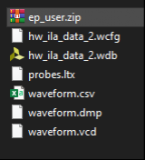

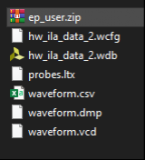

現(xiàn)在,您不僅可以使用 Python 腳本執(zhí)行調(diào)試分析,更重要的是,借由 Vivado ILA 所生成的 ILA 文件可以進一步簡化此操作。通過將 *.ila 擴展名重命名為 *.zip 然后將生成的文件解壓,即可將其轉(zhuǎn)換為 CSV 文件。

2023-06-26 09:20:46 2364

2364

電子發(fā)燒友網(wǎng)站提供《Vivado Design Suite用戶指南:編程和調(diào)試.pdf》資料免費下載

2023-09-13 14:47:21 2

2 電子發(fā)燒友網(wǎng)站提供《Vivado設計套件用戶指南:編程和調(diào)試.pdf》資料免費下載

2023-09-13 11:37:38 0

0 《Vivado Design Suite 用戶指南:編程和調(diào)試》 文檔涵蓋了以下設計進程: 硬件、IP 和平臺開發(fā) : 為硬件平臺創(chuàng)建 PL IP 塊、創(chuàng)建 PL 內(nèi)核、功能仿真以及評估 AMD

2023-10-25 16:15:02 1642

1642

ILA應該是調(diào)試AMD-Xilinx FPGA最常用的IP。

2024-05-01 10:43:00 2308

2308

Cadence的統(tǒng)一調(diào)試平臺Verisium Debug,為從IP到SoC級別的復雜設計提供了全面的調(diào)試解決方案。該平臺集成了多種調(diào)試功能,包括RTL調(diào)試、UVM仿真平臺調(diào)試、UPF調(diào)試以及DMS

2025-02-17 11:10:06 1389

1389

電子發(fā)燒友App

電子發(fā)燒友App

評論