前言

在 FPGA 開發(fā)過程中,燒寫bit文件和使用ILA進(jìn)行調(diào)試是再常見不過的操作。但如果 FPGA 板卡被放在機(jī)房,或者通過PCIe插在服務(wù)器上,那么每次調(diào)試時我們都不得不帶著筆記本電腦跑去機(jī)房或服務(wù)器旁,接上 JTAG 線后才能進(jìn)行調(diào)試,非常不便。

其實(shí),Vivado本身支持通過以太網(wǎng)遠(yuǎn)程連接服務(wù)器上的硬件工具,直接完成調(diào)試操作。也就是說,我們無需額外工具、無需親臨現(xiàn)場,就能在本地電腦上遠(yuǎn)程燒寫bit文件和調(diào)試ILA,大大提升了開發(fā)效率。

環(huán)境配置(遠(yuǎn)程主機(jī)端)

安裝Vivado Lab套件

訪問AMD-Xilinx官網(wǎng),在Download專區(qū)獲取最新版Vivado Lab Edition安裝程序。Download官網(wǎng)鏈接,也可以通過文末附錄A獲取。

將下載的安裝包如Xilinx_Vivado_Lab_Lin_2020.2_1118_1232.tar.gz(建議校驗(yàn)MD5哈希值確保完整性)傳輸至連接FPGA開發(fā)板的遠(yuǎn)程操作主機(jī)

注:該主機(jī)指直接通過JTAG/USB接口與FPGA硬件建立物理連接的計(jì)算機(jī)。

# 解壓 tar -xf Xilinx_Vivado_Lab_Lin_2020.2_1118_1232.tar.gz cdXilinx_Vivado_Lab_Lin_2020.2_1118_1232/ # 安裝 sudo./xsetup --agree XilinxEULA,3rdPartyEULA,WebTalkTerm --batch Install --edition"Vivado Lab Edition (Standalone)" --location /opt/Xilinx

配置系統(tǒng)環(huán)境變量

編輯/etc/environment文件,在PATH變量的末尾追加 Vivado 安裝后的 bin 路徑。我這里是將 Vivado 安裝在/opt目錄下的,讀者可以根據(jù)自己的實(shí)際安裝路徑進(jìn)行相應(yīng)修改。

:/opt/Xilinx/Vivado_Lab/2020.2/bin

安裝Jtag驅(qū)動

和windows不同的點(diǎn)是Linux的jtag驅(qū)動是需要手動安裝的

cd/opt/Xilinx/Vivado_Lab/2020.2/data/xicom/cable_drivers/lin64/install_script/ sudo./install_drivers

安裝完成后需重新插拔JTAG電纜,并重啟Linux以更新環(huán)境變量。

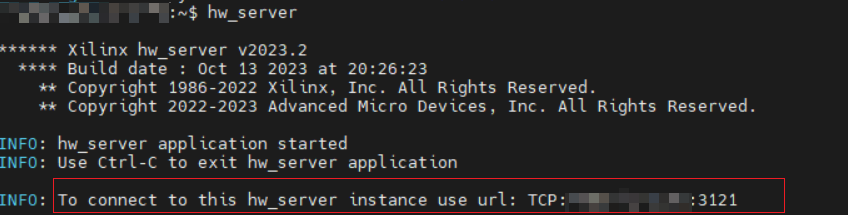

啟動遠(yuǎn)程主機(jī)端vivado服務(wù)

hw_server

成功啟動后將顯示連接信息:

INFO: To connect to this hw_server instance use url: TCP:主機(jī)名:3121

本地Vivado連接配置

本地就是你自己的電腦

1.打開vivado

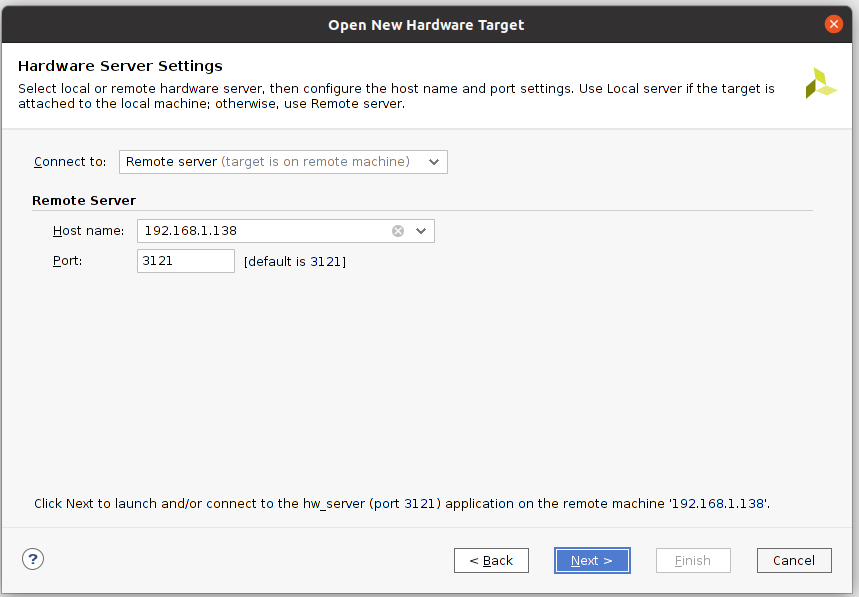

打開本地Vivado → Hardware Manager → Open Target → Open New Target

2.選擇Remote Server

選擇Remote Server并輸入:

Host name: 遠(yuǎn)程主機(jī)IP(示例:192.168.1.138)

Port: 3121(默認(rèn)值)

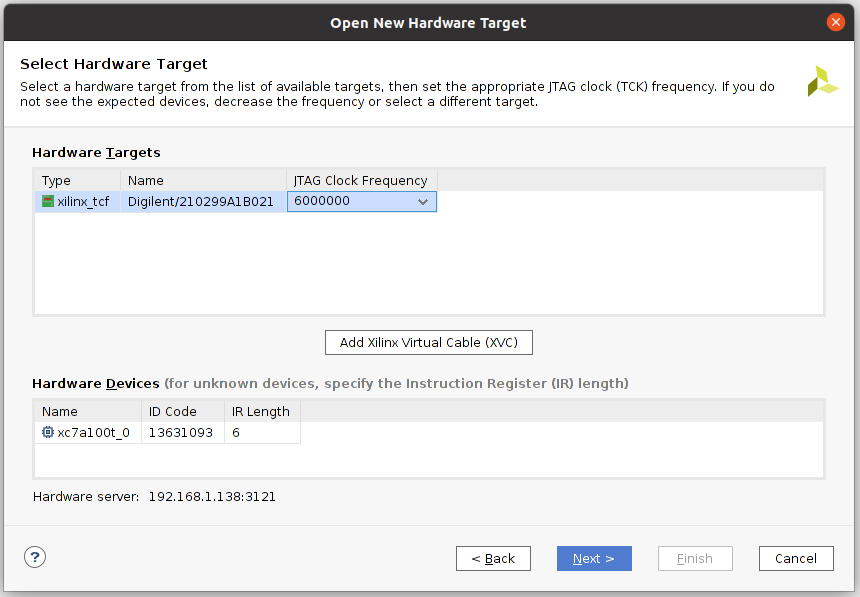

3.連接主機(jī)

點(diǎn)擊Next后,Vivado將自動連接遠(yuǎn)程服務(wù)器并顯示可用硬件設(shè)備:

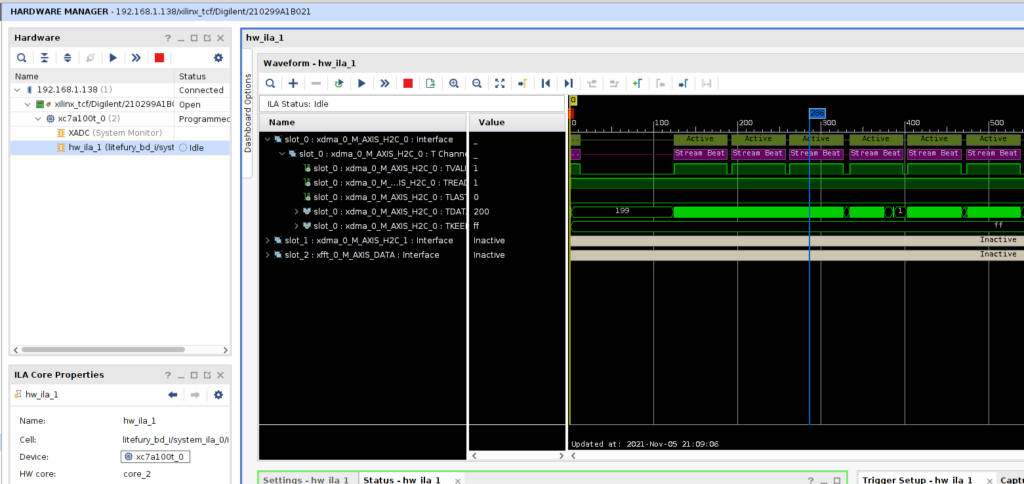

4.調(diào)試

一旦連接上遠(yuǎn)程主機(jī),燒寫調(diào)試體驗(yàn)就和直接用線連JTAG沒什么區(qū)別了

其他

故障排查

| 現(xiàn)象 | 解決方案 |

| 連接超時 | 檢查3121端口防火墻設(shè)置 |

| 設(shè)備未識別 | 重新插拔JTAG電纜并驗(yàn)證驅(qū)動安裝 |

| 權(quán)限拒絕 | 確認(rèn)用戶加入dialout組 |

| Vivado版本不匹配 | 確保Lab版本與本地Vivado一致 |

網(wǎng)絡(luò)連接要求

| 網(wǎng)絡(luò)類型 | 配置復(fù)雜度 | 典型延遲 | 安全性 | 適用場景 |

| 同一網(wǎng)段 | ★☆☆☆☆ | <1 ms | 中 | 實(shí)驗(yàn)室內(nèi)部調(diào)試 |

| 跨子網(wǎng)局域網(wǎng) | ★★☆☆☆ | 1-5ms | 中 | 企業(yè)多樓層部署 |

| VPN連接 | ★★★☆☆ | 10-50ms | 高 | 遠(yuǎn)程團(tuán)隊(duì)協(xié)作 |

| 公網(wǎng)直連 | ★★★★☆ | 50-200ms | 低 | 跨地域調(diào)試(需安全加固) |

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636233 -

服務(wù)器

+關(guān)注

關(guān)注

14文章

10251瀏覽量

91480 -

遠(yuǎn)程調(diào)試

+關(guān)注

關(guān)注

0文章

58瀏覽量

8909 -

Vivado

+關(guān)注

關(guān)注

19文章

857瀏覽量

71104

原文標(biāo)題:FPGA遠(yuǎn)程調(diào)試指南,無需親臨現(xiàn)場也能燒寫bit和調(diào)ILA

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

vivado ILA 實(shí)現(xiàn)在線調(diào)試功能報(bào)錯,顯示沒有添加ILA,怎么解決?

Arty是否有可能不支持ILA調(diào)試?

FPGA配置– 使用JTAG是如何燒寫SPI/BPI Flash的?

xilinx vivado zynq pldma PL部分ILA調(diào)試

xilinx FPGA bit 文件加密

如何采用DATA進(jìn)行Flash的在線燒寫

FPGA開發(fā)要懂得使用硬件分析儀調(diào)試——ILA

Vivado調(diào)試ILA debug結(jié)果也許不對

NODEMCU V3燒寫 AT固件

STM32:程序燒寫方式

Jlink使用技巧之燒寫SPI Flash存儲芯片

FPGA遠(yuǎn)程燒寫bit文件和調(diào)試ILA指南

FPGA遠(yuǎn)程燒寫bit文件和調(diào)試ILA指南

評論