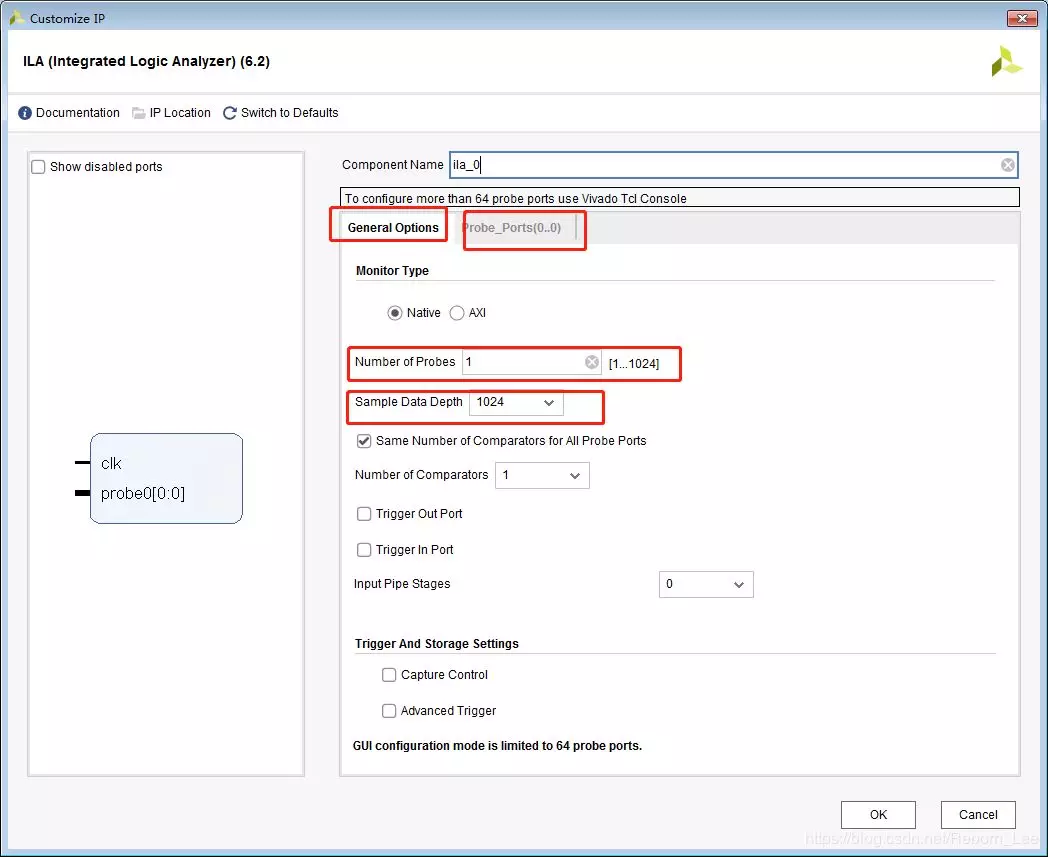

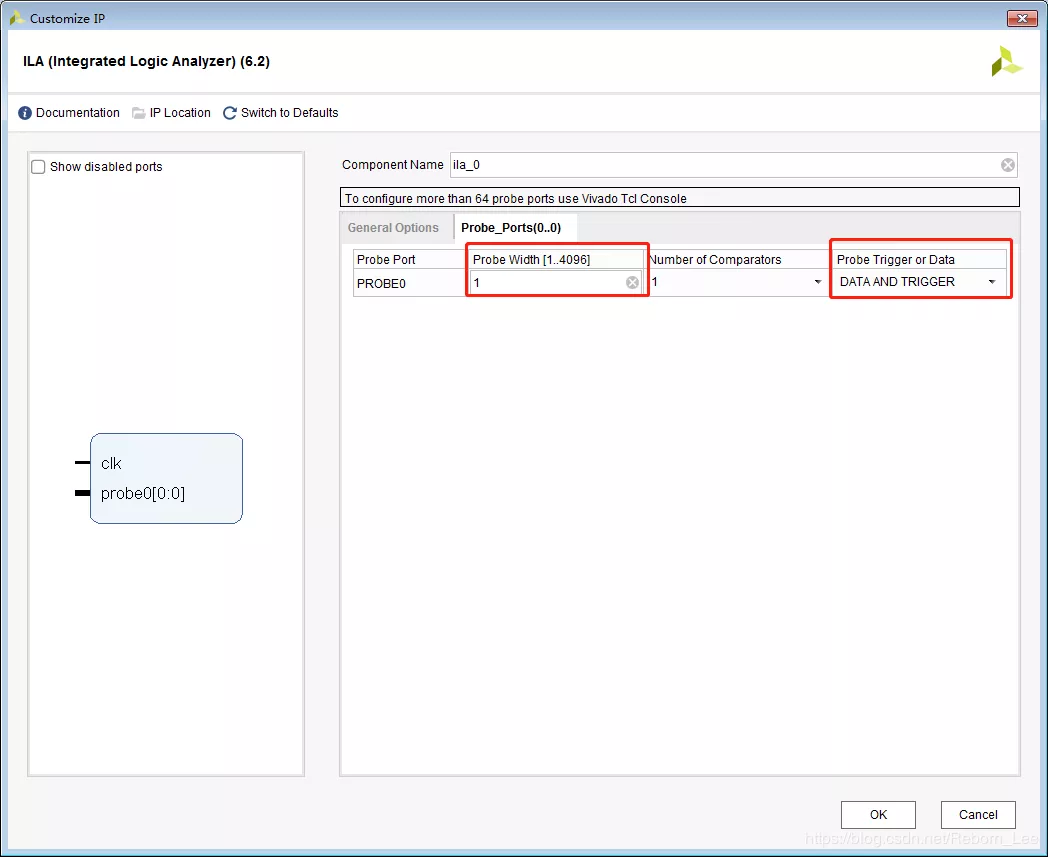

下面界面可以選擇探測信號寬度以及觸發方式:

可謂之簡單粗暴,如果沒人干預你,就這樣用也沒關系。之后直接在程序中例化即可。

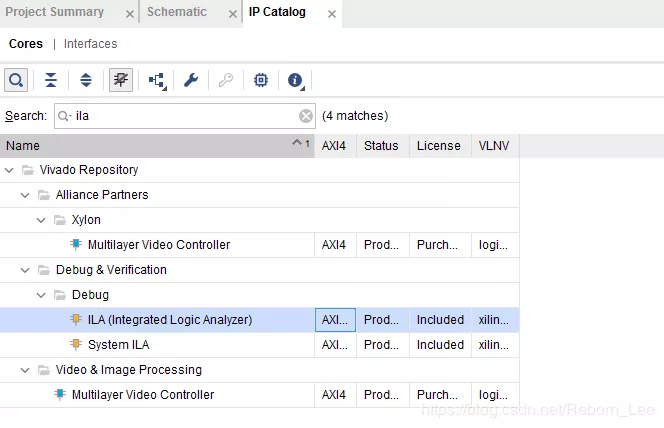

2. 通過網表標記

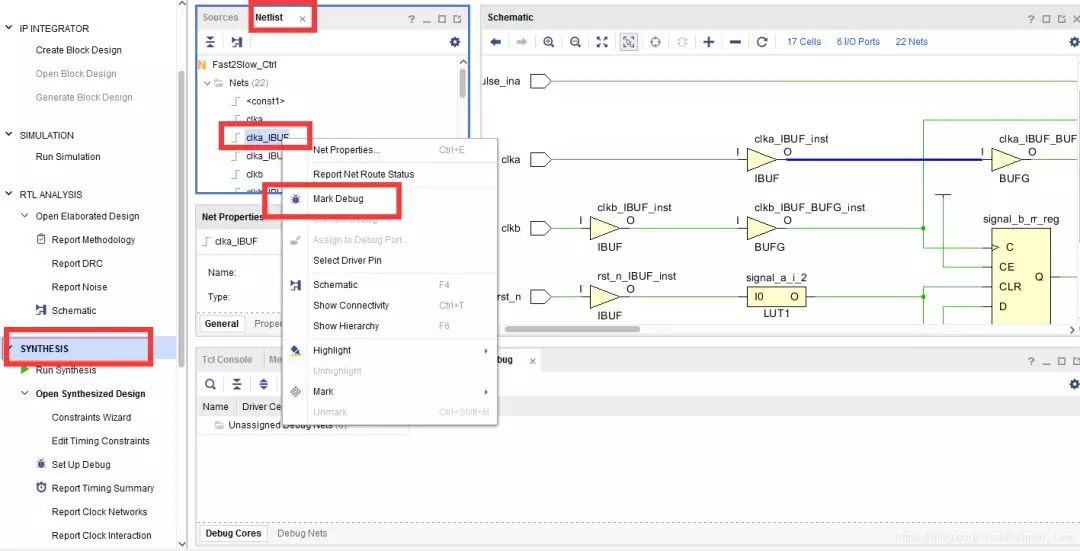

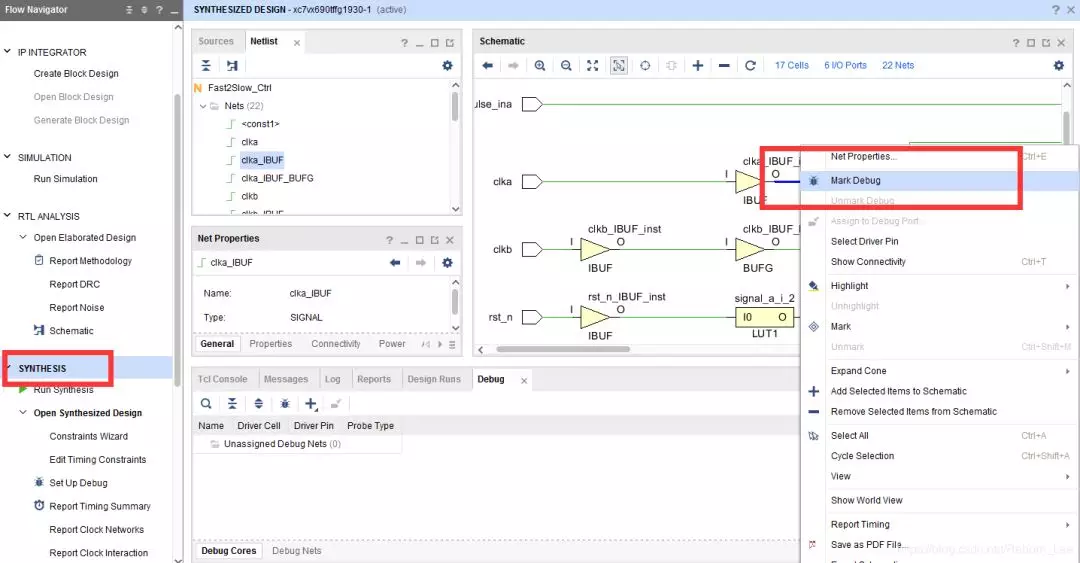

綜合后生成網表,在網表中設置Debug:Mark Debug。

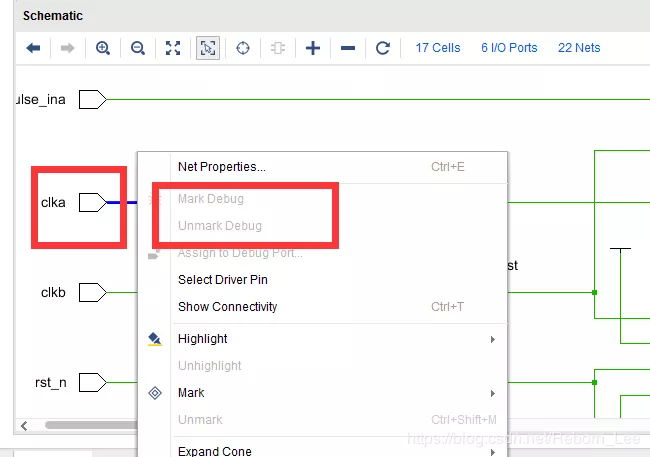

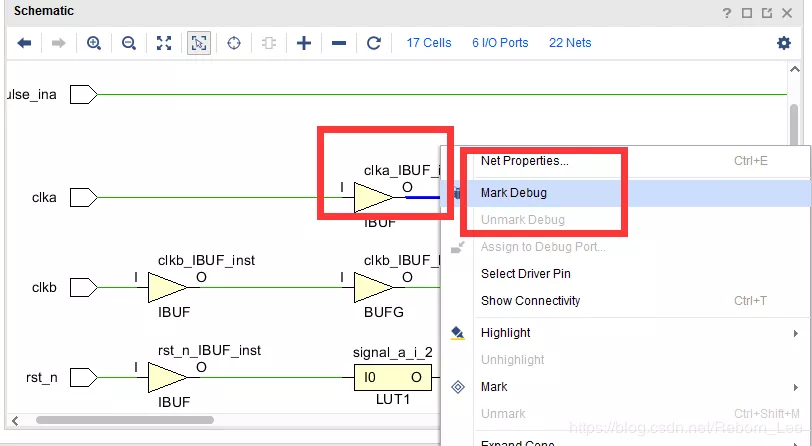

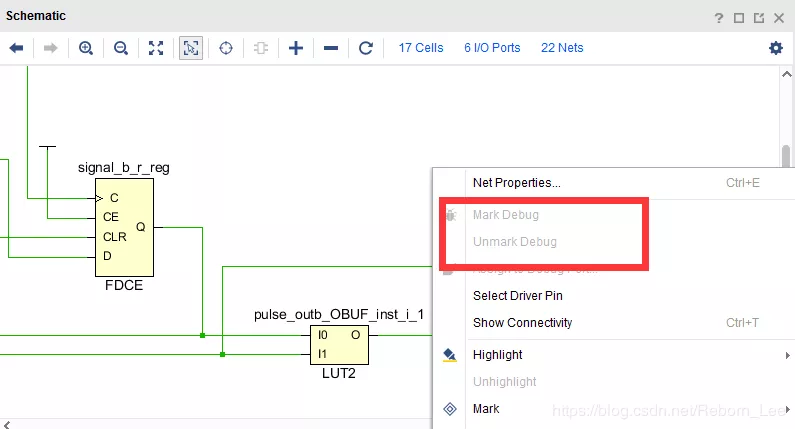

或者在綜合后的原理圖中Mark Debug,這和網表debug是一致的:

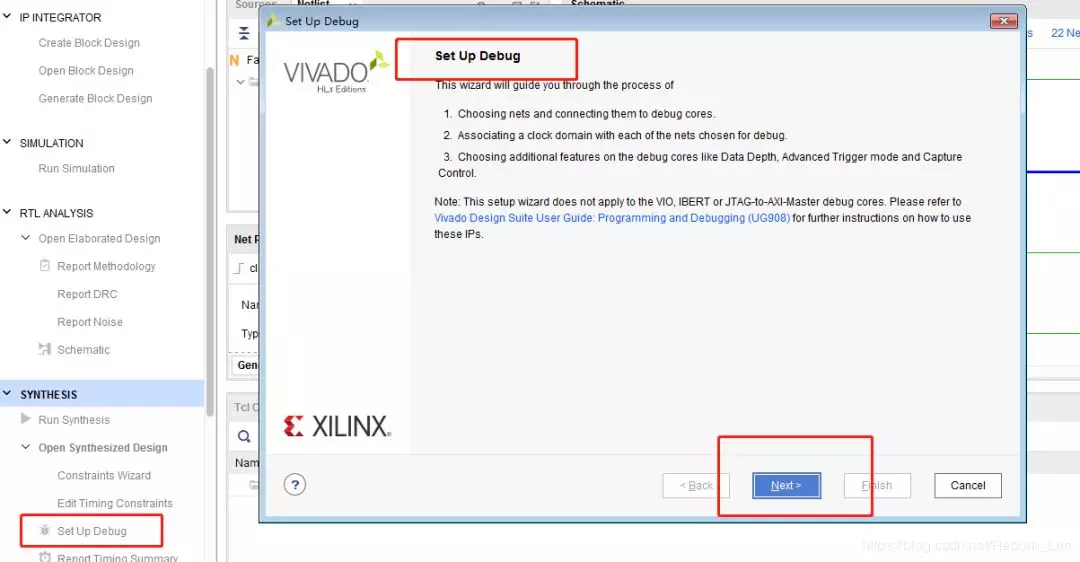

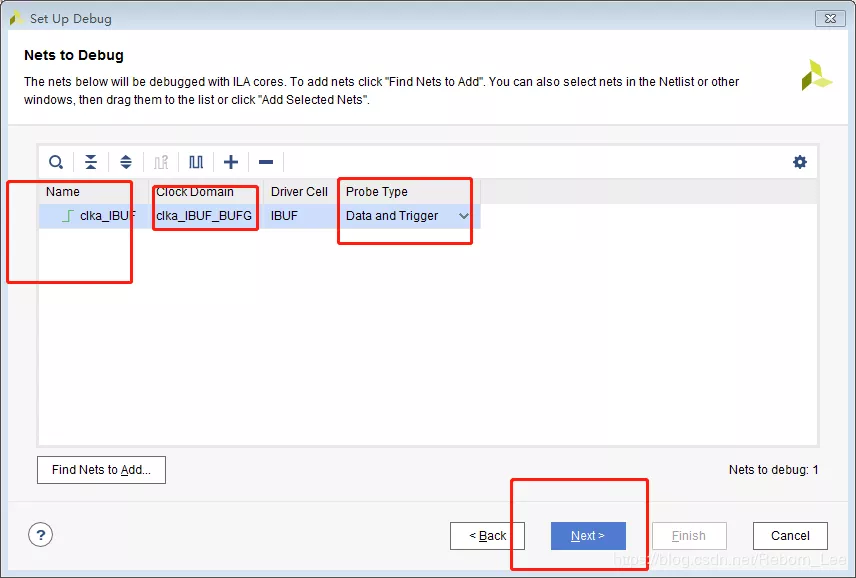

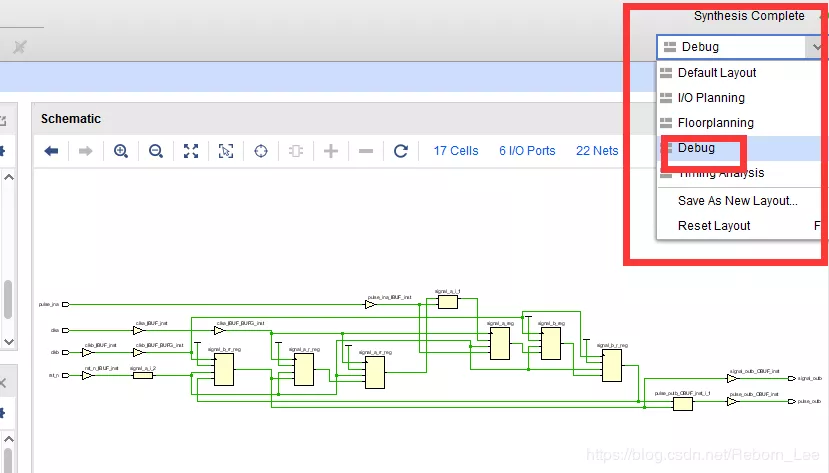

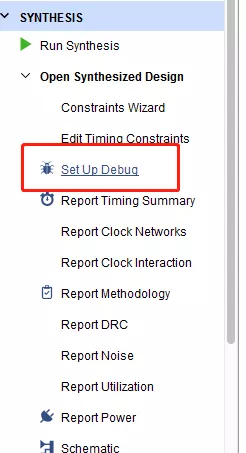

在標記Debug后,就等于選擇了需要debug的信號,之后在綜合設置里設置Debug參數即可:

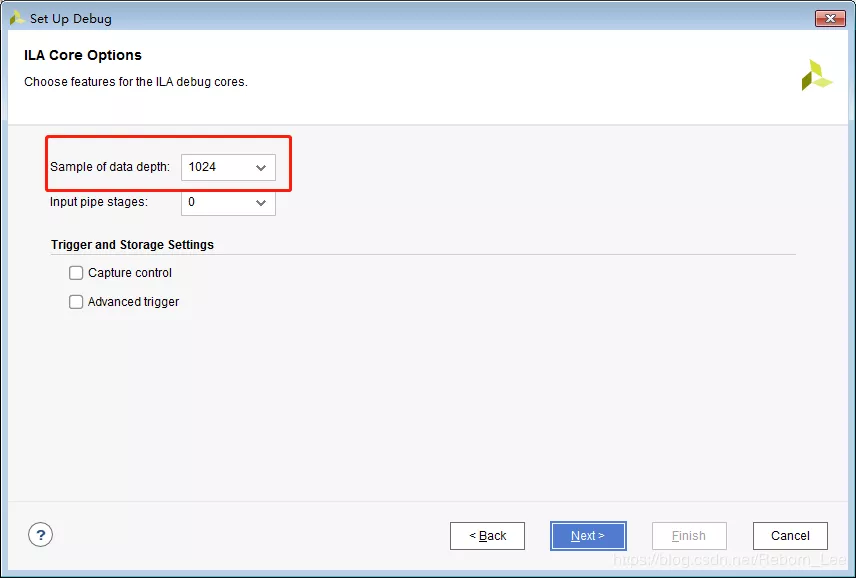

選擇采樣深度:

之后,重新綜合,實現生成bit流文件即可完成debug,準備上板子吧。

注意:有些信號能夠Mark Debug,有些則不能,例如模塊直接的輸入信號不能:

它經過一個Buf之后就可以:

最后的輸出也不能?

哎呀, 具體什么個原則我也不知道了,不如就直接在網表中試試吧,如果不行,就找類似的代替唄。

綜合后,也許你說自己找不到原理圖在哪里,那就看這里:

方式二已經很實用了吧,不用修改代碼!

3. 代碼中Mark_debug

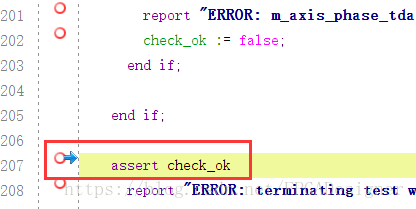

第三種還要在代碼中加入標記:

之后綜合,在set up debug,之后的操作同方式二。

編輯:hfy

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

DEBUG

+關注

關注

3文章

95瀏覽量

21379 -

Vivado

+關注

關注

19文章

857瀏覽量

71107

發布評論請先 登錄

相關推薦

熱點推薦

FPGA中三種常用復位電路

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復位電路:同步復位、異步復位和異步復位同步釋放,以及相應的Verilog代碼示例。

發表于 05-14 14:44

?3502次閱讀

詳細解讀Zynq的三種啟動方式(JTAG,SD,QSPI)

本文介紹zynq上三種方式啟動文件的生成和注意事項,包括只用片上RAM(OCM)和使用DDR3兩種情況。 JTAG方式 JTAG方式是調試中

發表于 11-10 14:49

?1.6w次閱讀

Vivado中使用debug工具步驟與調試技巧

在ISE中稱為ChipScope而Vivado中就稱為in system debug。下面就介紹Vivado中如何使用debug工具。 Debug

發表于 11-17 14:05

?6.4w次閱讀

Vivado使用技巧:debug仿真設計的三種調試方法

源代碼級別調試 Vivado Simulator提供了在仿真過程中debug設計的特性,通過為源代碼添加一些可控制的執行條件來檢查出問題的地方。總的來說有三種調試方法: 1.使用Step逐行調試

一文解析Vivado的三種封裝IP的方式

Vivado提供了三種封裝IP的方式:(1)將當前工程封裝為IP;(2)將當前工程中的BD(IPI 設計)封裝為IP;(3)將指定的文件目錄封裝為IP。 IP Packager支持的輸入文件HDL

FPGA應用之vivado三種常用IP核的調用

今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

發表于 02-02 10:14

?5075次閱讀

Redis實現限流的三種方式分享

當然,限流有許多種實現的方式,Redis具有很強大的功能,我用Redis實踐了三種的實現方式,可以較為簡單的實現其方式。

Windows管理內存的三種主要方式

Windows操作系統提供了多種方式來管理內存,以確保系統資源的有效利用和性能的優化。以下是關于Windows管理內存的三種主要方式的詳細闡

關于Vivado中三種操作Debug的方式

關于Vivado中三種操作Debug的方式

評論