Vivado集成設計環境(IDE)交互式處理設計。工程模式下,既可以通過圖像界面下操作(GUI操作,鼠標操作),也可以通過運行Tcl腳本的方式在Vivado Tcl shell 中運行。 優勢: 工作模式

2020-11-09 17:15:47 5785

5785

作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 4357

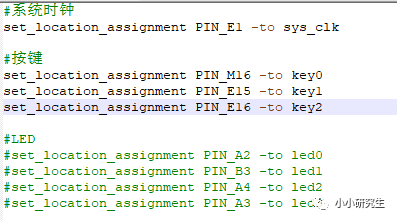

4357 時序約束的目的就是告訴工具當前的時序狀態,以讓工具盡量優化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創建基本的時序約束。Vivado使用SDC基礎上的XDC腳本以文本形式約束。以下討論如何進行最基本時序約束相關腳本。

2022-03-11 14:39:10 11063

11063 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 2515

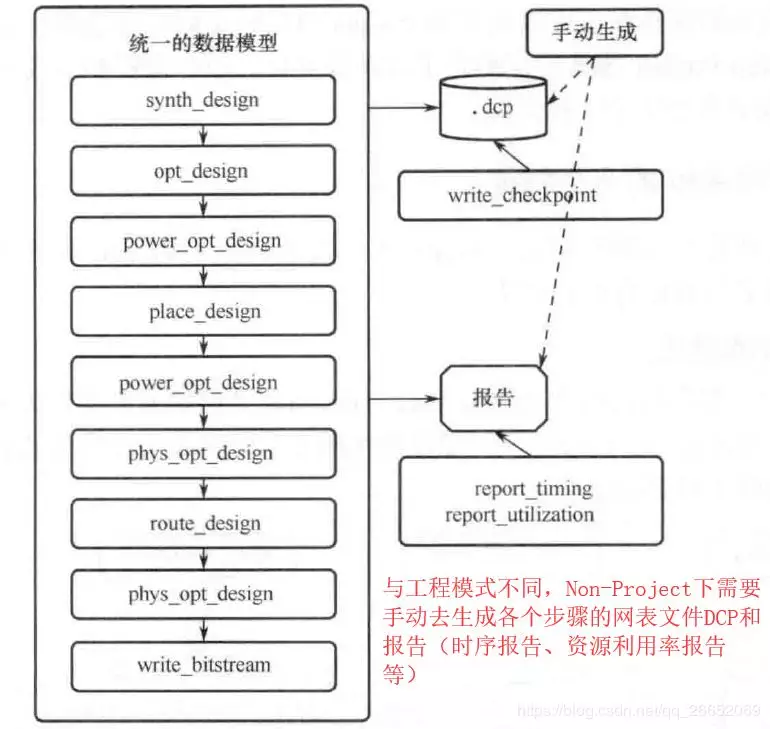

2515 Non-Project模式下使用OOC / 542.4 綜合后的設計分析 / 542.4.1 時鐘網絡分析 / 542.4.2 跨時鐘域路徑分析 / 562.4.3 時序分析 / 602.4.4 資源利用率分析

2020-10-21 18:24:48

/vivado.tcl”第30行)************************************************** *************為什么該工具在'input'目錄中搜索edf文件,后綜合

2018-10-18 14:26:39

1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

在ISE中直接添加IP核網表文件;Vivado的dcp文件中包括綜合網表)4、初步綜合——點評:在添加約束前,最好先綜合,以便明確綜合后網表中的clk的名字。Vivado實時檢查代碼是否存在語法錯誤

2021-01-08 17:07:20

,Vivado會自動按照上述的流程順序來進行編譯。快捷啟動的按鈕如下圖所示:在編譯過程中Vivado會顯示進行到哪一步了,可以查看messege,log等窗口。在sumarry窗口中也會有簡單的提示如下

2019-07-18 15:40:33

,Vivado會自動按照上述的流程順序來進行編譯。快捷啟動的按鈕如下圖所示:在編譯過程中Vivado會顯示進行到哪一步了,可以查看messege,log等窗口。在sumarry窗口中也會有簡單的提示如下

2023-09-06 17:55:44

嗨,我需要為Vivado 2016.3運行tcl來運行多個測試平臺。如果我使用下一個:launch_simulationrun -allwait_on_run [current_run

2020-05-20 15:53:34

和源碼,減少硬盤空間占用。 1.打開Vivado工程,在Tcl Console中輸入reset_project命令(Type a Tcl command here處輸入reset_project后回車

2020-08-17 08:41:25

的全局綜合之前,單獨地進行OOC綜合并生成輸出產品(Generate Output Products),包括綜合后的網表等各種文件。在對頂層進行綜合時,OOC模塊會被視為黑盒子,并且不會參與到頂層的綜合中

2023-04-17 16:33:55

將程序從低版本的vivado搬移到高版本的vivado的時,直接在高版本的vivado下升級軟核中的各個IP后,在綜合過程中報錯。在低版本的vivado平臺下,原程序已經完成編譯。

2020-11-14 20:57:13

本文利用NucleiStudio IDE 和 vivado 對 NICE demo協處理器進行軟硬件聯合仿真。

1. 下載demo_nice例程:https://github.com

2025-11-05 13:56:02

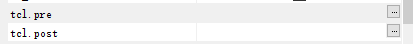

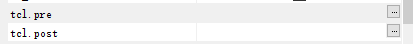

的opt_Desing中的tcl.pre中關聯導入的balck.tcl文件:Finally,我們就可以進行正常的綜合及布局布線了,布局布線完成后我們得到的網表和正常工程一模一樣。原作者:玉騏

2022-07-18 16:01:04

opt_design的tcl.pre中指定,使之有效(如下圖所示)。在Vivado的圖形界面中,綜合(Synthesis)和實現(Implementation)階段的每個子步驟都可以添加Tcl腳本。其中

2022-06-17 14:52:14

先按照官方給的開源項目,e203_hbirdv2-masterfpgamcu200t目錄下的Makefile內容手動創建vivado工程。

在調用.tcl文件的過程中,每次進行

2025-10-28 07:19:22

你好,我做了Project->生成TCL腳本。現在,我希望能夠從tcl腳本中指定.bit文件名。我怎么做?以上來自于谷歌翻譯以下為原文hello,I did the Project->

2018-11-09 11:49:07

在工程項目中常常使用xilinx的IP時常會遇到一些加密的verilog和vhdl,打開后是以Xlx開始的十六進制文件,某些IP中的tcl和ttcl也是用這種方式保存的十六進制文件。vivado中使用這些文件都沒有什么問題,就想知道這些文件是如何產生出來的?

2021-06-20 17:50:58

我們在做參賽課題的過程中發現,上FPGA開發板跑系統時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado ip核的soc系統進行仿真。在這種情況下

2025-10-24 07:28:03

在hbirdv2參考文檔中使用make指令生成system.bit和system.mcs文件,但是虛擬機本身會消耗計算資源,導致運行速度變慢,對于不習慣在linux下編輯代碼的人,還需要來回倒騰代碼

2025-10-27 08:25:28

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?買了一個第三方的IP,給出了端口列表和核心模塊發射機的.edf已經綜合過的網表文件,該網表文件里面富含了大量的信息,我想知道edf文件怎樣添加到Vivado工程中去?要不然的話,總是提示核心模塊實例化失敗!

2016-09-07 11:34:10

的在shell終端窗口執行Tcl腳本命令,無需打開Vivado軟件就進行編譯生成bit 文件,變得更高效了。如果需要修改工程的Block Design文件,可以打開Vivado進行修改或者直接修改

2020-06-07 13:59:52

請問大家,這個tcl腳本文件是做什么用的呢????本人是菜鳥,還望大家多多指教啊

2013-06-14 16:05:26

在modelsim里面對源程序進行編譯,在進行此操作前需要需改領個地方:a:只需要在vivado工程路徑下找到xxx.sim文件夾下面的“xxx_tb_compile.do”文件,打開該do文件,刪除該文

2018-10-16 19:43:20

求助大神 制作能夠 “加載TCL腳本功能”得用什么控件!求指教求指點~!萬分感謝~!{:36:}百度了好幾天都沒有~!

2013-04-22 09:55:43

,之所以叫門級仿真是因為綜合工具給出的仿真網表已經是與生產廠家的器件的底層元件模型對應起來了,所以為了進行綜合后仿真必須在仿真過程中加入廠家的器件庫,對仿真器進行一些必要的配置,不然仿真器并不認識其中

2018-01-24 11:06:12

嗨,Vivado的新手問題;是否有可能為后綜合模擬和/或后PAR網表模擬生成VHDL或Verilog網表?謝謝,埃里克

2019-11-11 07:33:05

嗨,專家我以前在Windows下設計,最近我搬到了linux。是否有關于如何使用腳本運行ISE / VIVADO的指南,例如Perl的?謝謝。克里斯以上來自于谷歌翻譯以下為原文Hi, experts

2019-02-19 10:59:18

你好,我編寫了一個Tcl腳本來合成Vivado Design Suite 2014.4中的設計(適用于Zynq ZC 706)。設計中的庫未編譯。彈出錯誤,表示找不到特定的.vhd文件。我檢查了

2020-04-16 10:15:31

。

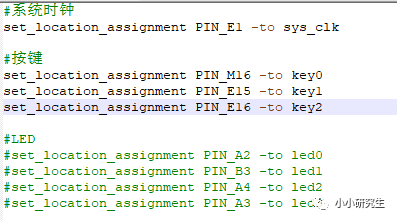

vivado加載所有的約束文件,這里需要將舊的文件remove掉,也就是藍框的兩個文件。

進行綜合時,如果提示jtag tck的iobuf錯誤,建議在約束文件中添加如下約束:

set_property

2025-10-31 08:46:40

無法使用基于ISE的策略運行綜合和實施,或導入ngc網表。請設置XILINX環境以獲得完整功能。source run_ippack.tcl -notrace確實在我打開vivado并添加我的IP并完成我

2020-04-03 08:48:23

所有: 我正在嘗試編寫一個TCL腳本來重命名帶有修訂號的.bit文件。我需要一種方法讓Vivado告訴我活動實現的名稱。例如,如果我的活動實現是impl_5,我需要知道這一點,以便找到正確的.bit

2018-11-12 14:23:34

嗨,我想試試JESD204硬件演示。為此,我必須在Windows命令提示符下使用“vivado -mode batch -source”運行.tcl腳本,但是當我輸入此內容時,我收到一條錯誤,即vivado命令未知或錯誤。我現在能做什么?非常感謝您提前和最好的問候揚 - 菲利普

2020-07-30 07:00:03

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

預先寫 好的 Tcl 腳本,返回值會即時顯示在這個對話框。

舉例來說,設計調試過程中,需要將一些約束應用在某些網表目標上(具體可參照《Tcl 在 Vivado 中的應 用》所示),推薦的做法就是在

2023-06-28 19:34:58

你好,嘗試使用kcu105 TRD設計中的.tcl在2018.2中進行ti構建設計,我遇到了這個錯誤。錯誤:[BD_TCL-109]此腳本是使用Vivado生成的,正在Vivado中運行。請在

2019-10-18 09:36:13

如何利用tcl腳本在lc_shell中批量把.lib文件轉化成.db文件?

2021-01-04 07:36:19

嗨,現在我正在使用GTECH綜合網表和dw_foundationin asic work porcess。但我不確定我是否可以使用GTECH綜合網表和dw_foundation到virtex5

2020-07-08 08:53:36

如何保證RTL設計與綜合后網表的一致性文章簡介:在超大規模數字集成電路的設計中,我們使用邏輯綜合工具來完成從RTL設計到門級網表的轉化。我們希望它綜合出的門級網表

2009-01-23 23:10:52 19

19 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

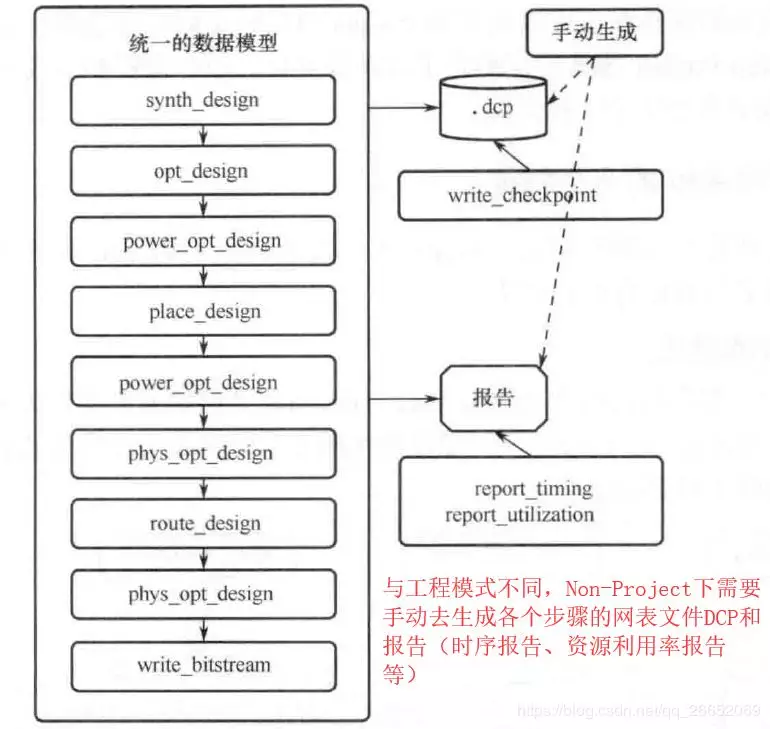

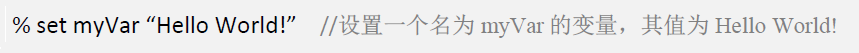

65 其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 4100

4100

Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。本文介紹了Tcl在Vivado中的基礎應用,希望起到拋磚引玉的作用,指引使用者在短時間內快速掌握相關技巧,更好地發揮Vivado在FPGA設計中的優勢。

2017-11-18 03:52:01 5363

5363

在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 6145

6145 用于共享工具命令語言腳本的開源庫已發布在GitHub.com上。 在過去五年里,賽靈思把戰略重點放在設計方法和工具上,通過提供業界最先進、最全面的開發環境,解決生產力問題,加快設計周期,促使產品更快

2017-11-18 09:10:23 8284

8284

關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布局布線的設計上

2017-11-18 18:26:46 5856

5856

TCL腳本語言 Tcl(Tool Command Language)是一種很通用的腳本語言,它幾乎在所有的平臺上都可以解釋運行,而且VIVADO也提供了TCL命令行。最近發現TCL腳本貌似比GUI下操作VIVADO效率高一些,方便一些。

2018-04-11 12:09:00 10954

10954 Vivado HLS 是 Xilinx 提供的一個工具,是 Vivado Design Suite 的一部分,能把基于 C 的設計 (C、C++ 或 SystemC)轉換成在 Xilinx 全可編程芯片上實現用的 RTL 設計文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 7420

7420

工具命令語言(TCL)是集成在VIVADO環境中的腳本語言。TCL是半導體工業中用于應用程序編程接口的標準語言,并由SyoSype?設計約束(SDC)使用。

2018-08-09 08:00:00 38

38 本文通過一個簡單的例子,介紹Vivado 下的仿真過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 38382

38382 觀看視頻,學習如何將 Vivado IP 和第三方綜合工具配合使用。 此視頻將通過一個設計實例引導您完成創建自定義 IP 的步驟;用第三方綜合工具IP黑盒子來審查所需 IP 輸出;整合 Vivado IP 網表和第三方綜合工具網表的兩個方法,即 “網表項目模式” 和 “非項目 Tcl 腳本模式”。

2018-11-21 06:34:00 5691

5691 了解如何使用Tcl命令語言以批處理模式運行Vivado HLS并提高工作效率。

該視頻演示了如何從現有的Vivado HLS設計輕松創建新的Tcl批處理腳本。

2018-11-20 06:06:00 3634

3634 實際上Tcl的功能可以很強大,用其編寫的程序也可以很復雜,但要在Vivado或大部分其它EDA工具中使用,則只需掌握其中最基本的幾個部分

2019-07-24 16:52:00 4121

4121

從 Vivado 2019.1 版本開始,Vivado 綜合引擎就已經可以支持增量流程了。這使用戶能夠在設計變化較小時減少總的綜合運行時間。

2019-07-21 11:02:08 2129

2129 上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向導(Constraints Wizard)。兩者都可以在綜合或實現后的Design中打開。

2020-03-08 17:17:00 20443

20443

Vivado IDE約束管理器將任何已編輯的約束保存回XDC文件中的原始位置,但不會保存在Tcl腳本中。 任何新約束都保存在標記為目標的XDC文件的末尾。

2020-11-13 10:53:38 5530

5530

與上一代開發工具ISE,一個巨大的提升就是全面支持Tcl腳本語言。由于全面支持Tcl腳本,所以可以利用Tcl來做一些好玩的事情。這里拋磚引玉,分享一點關于Vivado Tcl的使用小心得。 通常的工程中,直接生成的文件是bit文件(如果需要調試,可能還需要ltx文件)。而量產項目中,bit文件的內

2020-11-13 12:48:53 4267

4267

,還是從對使用者思路的要求,都是全新的;在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。 本文介紹了Tcl在V

2020-11-17 17:32:26 3306

3306 這里帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。

2020-11-29 11:04:53 5256

5256

有的時候需要查找一些官網的例程進行學習和參考,但是總感覺無從下手,今天就教大家怎么利用官網和Vivado的Documention進行相關的操作。 ?不清楚使用哪些IP或者不清楚需要參考哪個文檔 首先

2020-12-28 09:39:13 3210

3210

我們都知道FPGA的實現過程分為2步:分析綜合與布局布線后就可以產生目標文件,這兩個步驟中間有個非常重要的文件,那就是-網表。 下圖是Vivado中網表列表示例: ? ? ? ? ? Vivado

2021-05-14 10:46:53 5414

5414

。 摘要: 在學個Antenna:HFSS腳本建模入門中,介紹了利用HFSS自帶的Record Script To File功能進行腳本錄制。但是大部分情況下,工程師們只是希望錄制簡單的后處理腳本。這期推文就來介紹下如何解放雙手,一鍵式處理。 本文使用的軟件為AnsysEM

2021-07-29 11:15:02 4396

4396 符。 Vivado Synthesis Hangs/StopsVivado在綜合時,如果顯示一直在運轉,但不再輸出任何log信息時,檢查一下工程路徑是否包含了特殊字符“”。因為“”字符在Tcl腳本里是變量置換

2021-09-12 15:15:19 7447

7447 1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-06 09:20:58 6

6 傳統的FPGA開發都是通過GUI界面進行相關的“按鈕”式操作,Vivado則在引入Tcl解釋器后,可以通過非工程模式進行操作,一個Tcl腳本即可自動化建立工程,對工程進行分析。

2022-04-07 15:02:29 6371

6371 XDC約束可以用一個或多個XDC文件,也可以用Tcl腳本實現;XDC文件或Tcl腳本都要加入到工程的某個約束集(set)中;雖然一個約束集可以同時添加兩種類型約束,但是Tcl腳本不受Vivado工具管理,因此無法修改其中的約束;

2022-06-30 11:27:23 5420

5420 在FPGA設計里,設計仿真完成RTL代碼設計后便是交給設計套件進行綜合及布局布線。在綜合過程里,Vivado里提供的參數選項有點兒多,今天閑暇抽空梳理下。

2022-07-03 10:38:03 4960

4960 在 Windows 下,我喜歡在批處理模式下運行 Vivado 仿真器。 我創建了仿真批文件 (.bat) ,包含以下命令。當我運行批文件,執行第一條命令后腳本中止。如何正確在批模式下運行 Vivado 仿真器?

2022-08-01 09:43:01 1411

1411 Vivado可以導出腳本,保存創建工程的相關命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠遠小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 2471

2471 一個完整的vivado工程往往需要占用較多的磁盤資源,少說幾百M,多的甚至可能達到上G,為節省硬盤資源,可以使用Tcl命令對vivado工程進行備份,然后刪除不必要的工程文件,需要時再恢復即可。

2022-08-02 15:01:06 6814

6814 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-19 16:20:51 2298

2298 Vivado是Xilinx推出的可編程邏輯設備(FPGA)軟件開發工具套件,提供了許多TCL命令來簡化流程和自動化開發。本文將介紹在Vivado中常用的TCL命令,并對其進行詳細說明,并提供相應的操作示例。

2023-04-13 10:20:23 5476

5476 Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 2185

2185 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 2068

2068

設計實現流程后,引出了一個更細節的應用場景:如何利用 Tcl 在已完成布局布線的設計上對網表或是布局布線進行局部編輯,從而在最短時間內,以最小的代價完成個別的設計改動需求。

2023-05-05 15:34:52 4104

4104

如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 5589

5589

Vivado綜合默認是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 1424

1424 目前已經學完了基礎實驗,這里要介紹Quatus自帶的兩個非常重要的功能,第一個是tcl腳本,第二個是SignalTap(下一篇)。

2023-09-07 18:30:49 4395

4395

電子發燒友網站提供《Vivado設計套件Tcl命令參考指南.pdf》資料免費下載

2023-09-14 10:23:05 1

1 電子發燒友網站提供《Vivado設計套件用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-14 14:59:39 1

1 電子發燒友網站提供《Vivado Design Suite用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-13 15:26:43 2

2 插入IBUF/OBUF,同時生成該模塊對應的網表文件。不論是第三方工具還是Vivado都是如此。對RM執行OOC綜合,這在DFX過程中是必要的。在后續布局布線時,工具要依次讀入靜態區的網表文件(RM為

2023-09-27 09:45:29 1385

1385 利用Shell進行腳本程序的設計可以按照以下步驟進行: 選擇Shell解釋器:在Unix和Linux系統中,通常會默認安裝一個或多個Shell解釋器,其中最常見且功能強大的是Bash(Bourne

2023-11-08 10:17:40 1189

1189 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立的IP工程,缺省情況下,IP工程的名字為magaged_ip_project。

2024-04-22 12:22:53 1963

1963

我們在日常開發中經常使用sublime、vim、vs code等第三方的編輯器,這些編輯器可以使用很多插件來提高我們的編碼效率,但是也往往會帶來亂碼的問題。我一般使用的是sublime來進行編碼

2024-10-15 17:24:40 3992

3992

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

2024-10-24 15:08:40 1602

1602

電子發燒友App

電子發燒友App

評論