TCL在IC領(lǐng)域中常用的腳本有Tcl、Perl、Shell、Python等,在這些腳本里面,Tcl(“工具命令語(yǔ)言”( 即Tcl的全稱Tool Command Language))由于其語(yǔ)法簡(jiǎn)單,易上手等特點(diǎn),在FPGA開(kāi)發(fā)中越來(lái)越受到重視。

John K. Ousterhout于 1988 年開(kāi)始開(kāi)發(fā) Tcl/Tk(讀作“tickle tee-kay”),然后是加州大學(xué)伯克利分校的一名教授繼續(xù)對(duì)它進(jìn)行開(kāi)發(fā)。目前TCL在很多EDA工具(Design Complier、quartus、Synplify、modesim、finesim、Vivado等)中都扮演重要角色,這也是為什么在FPGA設(shè)計(jì)中受到重視的主要原因。

TCL讓FPGA開(kāi)發(fā)更完美

目前FPGA幾大廠商中,Xilinx和Intel無(wú)疑在國(guó)內(nèi)占據(jù)很大市場(chǎng),其對(duì)應(yīng)的開(kāi)發(fā)的EDA工具分別為Quartus II和Vivado(老版本ISE),接下來(lái)以Vivado為例簡(jiǎn)單說(shuō)明其Tcl在開(kāi)發(fā)過(guò)程中的應(yīng)用。

Xilinx的設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。其中約束語(yǔ)言XDC及腳本語(yǔ)言TCL的引入更是讓其開(kāi)發(fā)更加完美。

下面從幾個(gè)方面說(shuō)明一下Tcl在Vivado中的應(yīng)用:

非工程模式(NoneProject Mode)

傳統(tǒng)的FPGA開(kāi)發(fā)都是通過(guò)GUI界面進(jìn)行相關(guān)的“按鈕”式操作,Vivado則在引入Tcl解釋器后,可以通過(guò)非工程模式進(jìn)行操作,一個(gè)Tcl腳本即可自動(dòng)化建立工程,對(duì)工程進(jìn)行分析。

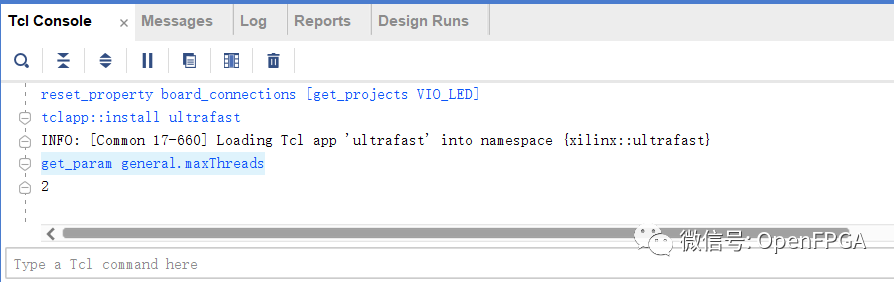

提高編譯效率

Vivado“出現(xiàn)”的比較晚,所以對(duì)于多線程的支持還是比較友好的,默認(rèn)情況下,Vivado在Windows默認(rèn)是2個(gè)線程(綜合階段,Windows/Linux操作系統(tǒng)都是2),實(shí)現(xiàn)階段Windows默認(rèn)也是2個(gè)線程(Linux操作系統(tǒng)的默認(rèn)線程數(shù)為8),我們可以通過(guò)

同時(shí)可以通過(guò)

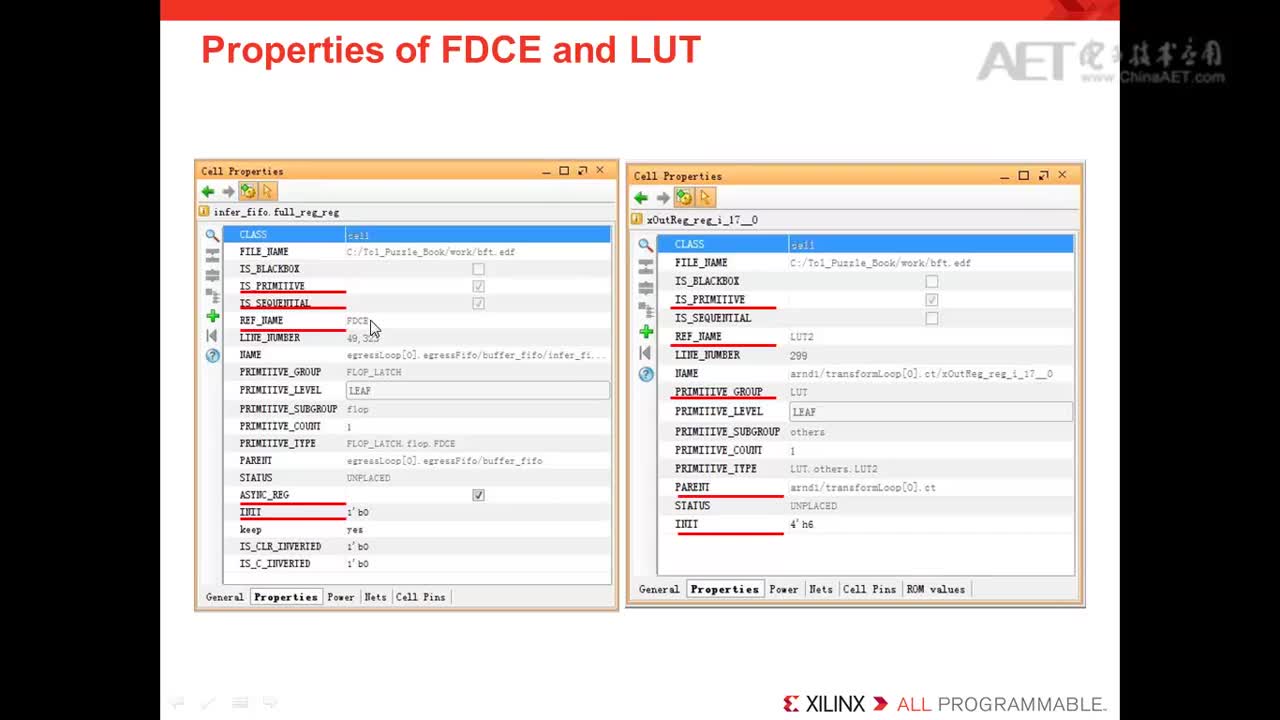

使用Tcl定位目標(biāo)

Vivado實(shí)現(xiàn)完成后,可以對(duì)出問(wèn)題的路徑進(jìn)行分析,同時(shí)對(duì)網(wǎng)表中的目標(biāo)進(jìn)行查找、定位和遍歷,其中常見(jiàn)的命令大家應(yīng)該都有見(jiàn)過(guò):

get_ports

get_cells/get_nets

get_pins

以上只是簡(jiǎn)單介紹了幾個(gè)Tcl在Vivado中的應(yīng)用,還有很多很多方面Vivado的開(kāi)發(fā)都不得不借助Tcl腳本,像XDC約束文本,等等。在一些“高級(jí)”應(yīng)用中,像包括ECO、PR、HD Flow等等都是從Tcl腳本方式開(kāi)始支持。

所以在目前的FPGA開(kāi)發(fā)模式中Tcl是一個(gè)繞不開(kāi)的語(yǔ)言,同時(shí)其特點(diǎn)也讓FPGA開(kāi)發(fā)更完美。

FPGA便捷開(kāi)發(fā)-TCL商店

Vivado在設(shè)計(jì)中集成了很多基礎(chǔ)的Tcl命令,所有的命令及作用都在Xilinx官方文檔UG835中,下面是鏈接(瀏覽器打開(kāi)即可閱讀):

?

https://www.xilinx.com/content/dam/xilinx/support/documentation/sw_manuals/xilinx2021_2/ug835-vivado-tcl-commands.pdf

但是,一旦遇到自己想要的功能(比如:獲取MMCM/PLL信息),但是Vivado中沒(méi)有集成進(jìn)去怎么辦?

今天的主角就閃亮登場(chǎng)了(鋪墊夠久了)-開(kāi)源項(xiàng)目XilinxTclStore

?

https://github.com/Xilinx/XilinxTclStore

方面下載鏈接(后面都會(huì)提供):

?

https://gitee.com/mirrors_Xilinx/XilinxTclStore

簡(jiǎn)介

Tcl Store 是 Tcl 代碼的開(kāi)源存儲(chǔ)庫(kù),主要用于 Xilinx Vivado 設(shè)計(jì)套件。應(yīng)用程序是由所有者發(fā)布和維護(hù)的一個(gè)或多個(gè) Tcl 腳本的組或集合。應(yīng)用程序所有者充當(dāng)該代碼的看門(mén)人,我們只接受所有者對(duì)應(yīng)用程序的貢獻(xiàn)。此外,整個(gè)存儲(chǔ)庫(kù)由 Xilinx 官方管理,它控制對(duì)公共存儲(chǔ)庫(kù)的推送和審核。

更多的介紹可以看下下面的視頻(帶字幕):

項(xiàng)目的WIKI界面有更詳細(xì)的介紹:

?

https://github.com/Xilinx/XilinxTclStore/wiki/Xilinx-Tcl-Store-Home

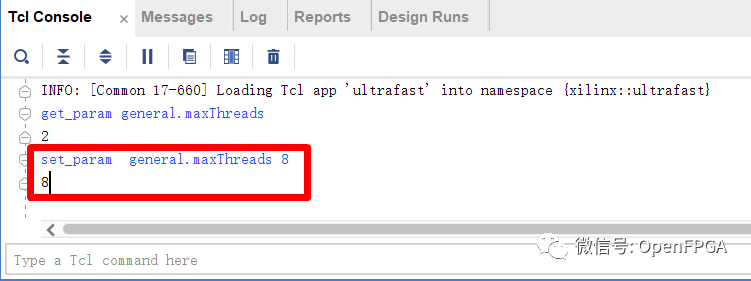

目前支持的幾大部分如下:

使用

其實(shí)整個(gè)開(kāi)源項(xiàng)目主要目的是可以大家集思廣益對(duì)項(xiàng)目做貢獻(xiàn),使用時(shí)非常簡(jiǎn)單的,只需要兩三步即可完成:

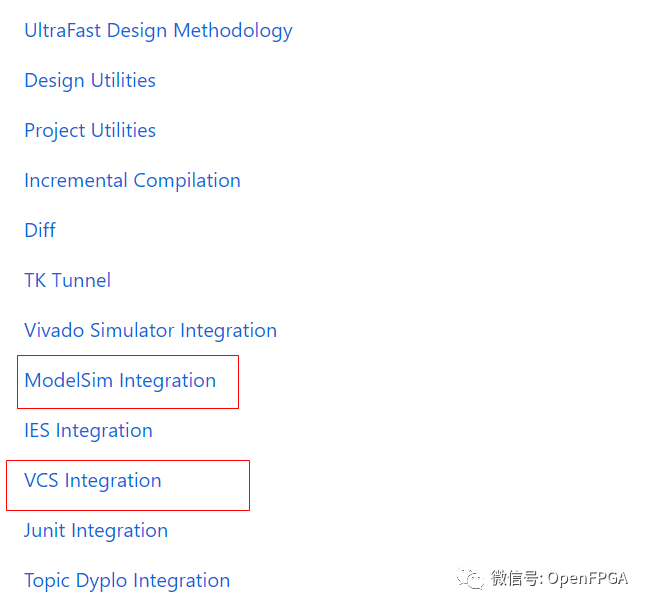

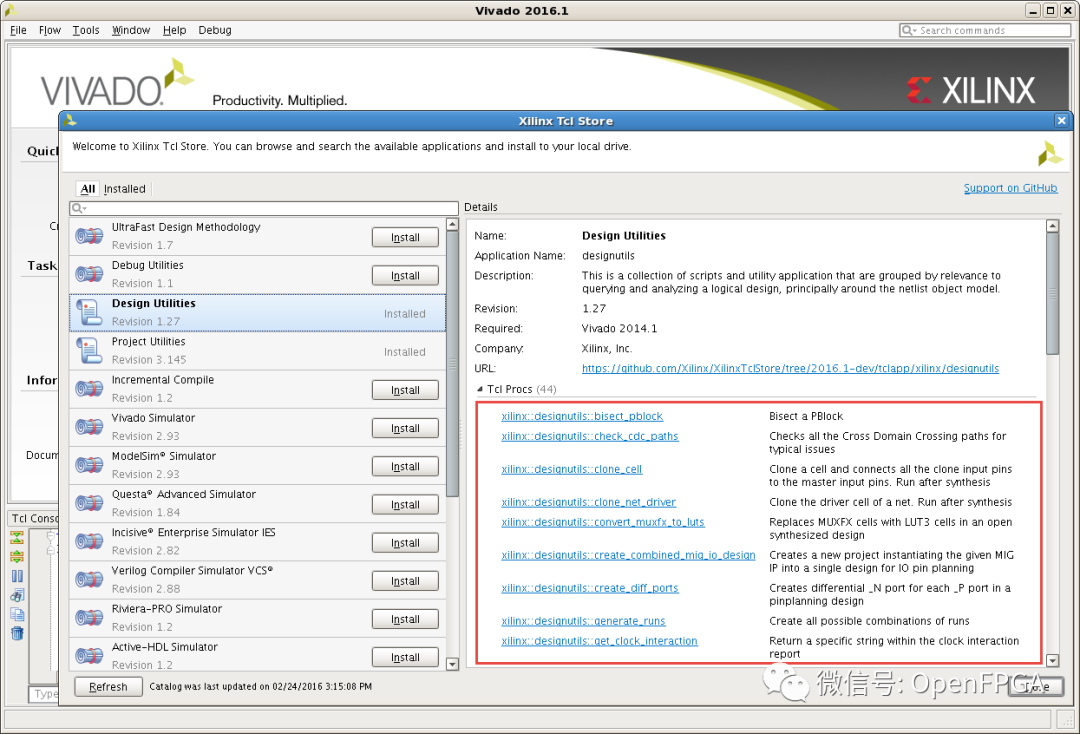

Vivado界面:Tool--> Xilinx Tcl Store,點(diǎn)擊Inatall即可安裝:

安裝程序后,將報(bào)告應(yīng)用程序中可用的 Tcl proc 列表以及一行摘要。

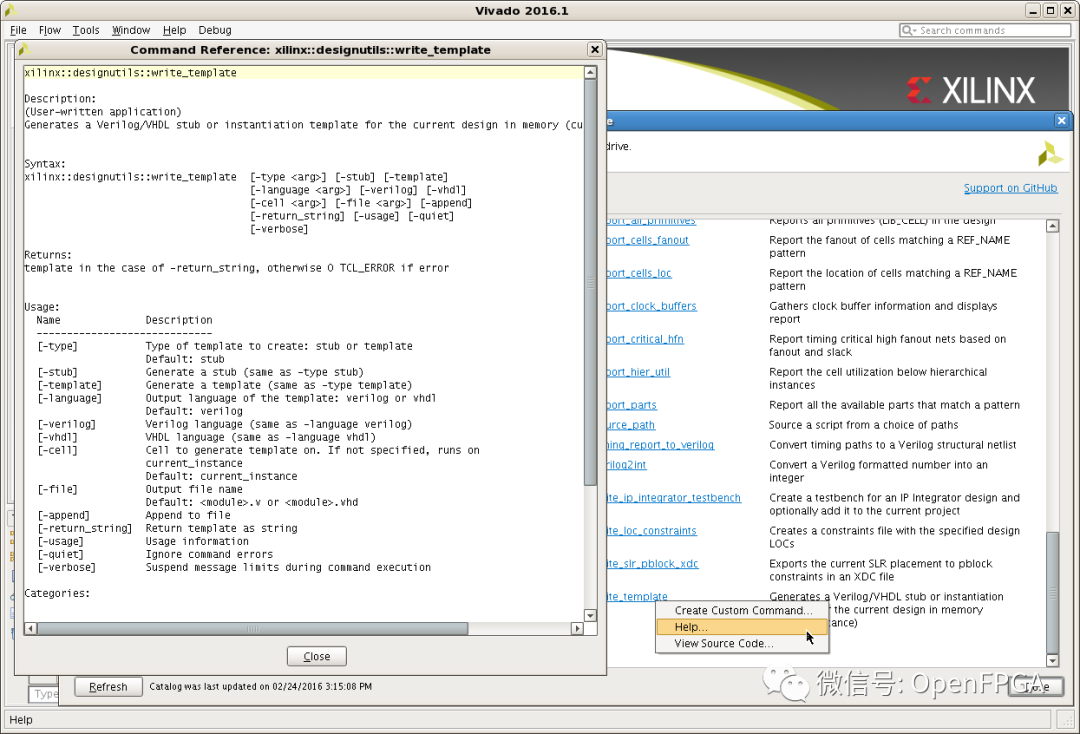

安裝程序后,proc 名稱將更改為超鏈接。單擊任何 proc 名稱會(huì)打開(kāi)一個(gè)帶有幫助菜單項(xiàng)的上下文窗口。選擇幫助會(huì)打開(kāi)所選過(guò)程的嵌入式幫助信息。

安裝程序后,可以通過(guò)兩種不同的方式訪問(wèn)屬于該應(yīng)用程序的所有 proc:

來(lái)自<::myapp 命名空間>。當(dāng) Vivado 啟動(dòng)時(shí),會(huì)自動(dòng)為<::myapp 命名空間>下所有已安裝應(yīng)用程序的所有 proc 創(chuàng)建一個(gè)入口點(diǎn)(包裝器)。 從定義 proc的應(yīng)用命名空間<::myapp>中。

上面說(shuō)的有點(diǎn)繞口,其實(shí)就在安裝完成就有一個(gè)命令,如下(以designutils為例):

圓圈中的命令就可以直接在Tcl中運(yùn)行

上面就是方式一的調(diào)用方式。還有方式二不常用就舉例如下:

vivado>::add_probe vivado>::add_probe

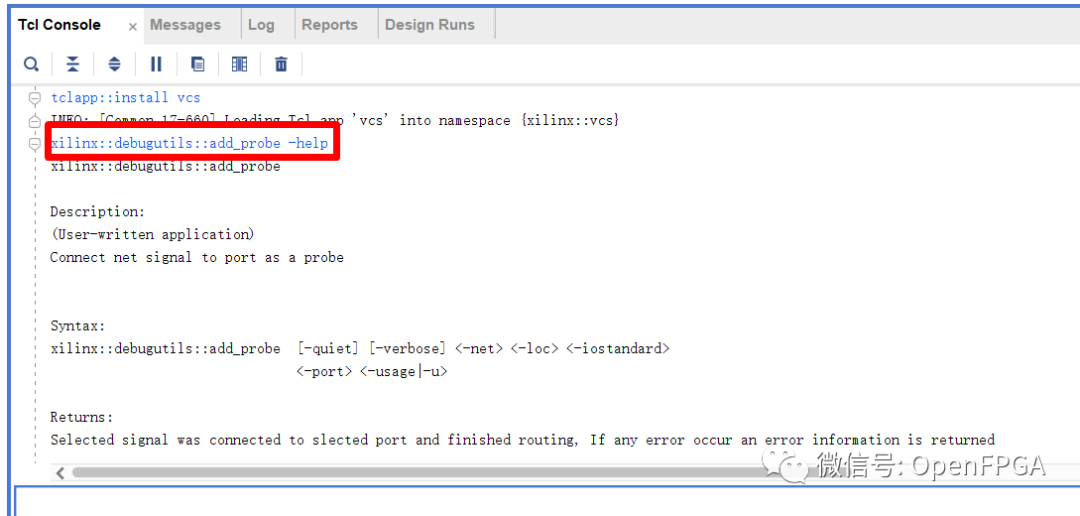

方式一常用的原因是可以帶一些默認(rèn)參數(shù),例如 -help、-verbose 和 -quiet

vivado>::add_probe-help

使用比較簡(jiǎn)單,一些命令很有用,比如在ila中插入一個(gè)PROBE,當(dāng)然可以結(jié)合自己的使用習(xí)慣建一些常見(jiàn)的Tcl命令。

關(guān)于怎么提交自己的代碼,可以看下這個(gè)項(xiàng)目的WIKI,講解的很詳細(xì)。

總結(jié)

今天介紹的項(xiàng)目,應(yīng)該是方便、便捷大家開(kāi)發(fā)FPGA的開(kāi)源項(xiàng)目,對(duì)于一些不怎么常用Tcl的用戶,可以慢慢學(xué)起來(lái)了,因?yàn)閺哪壳翱矗恍└呒?jí)的調(diào)試技巧都是從Tcl出發(fā)的。

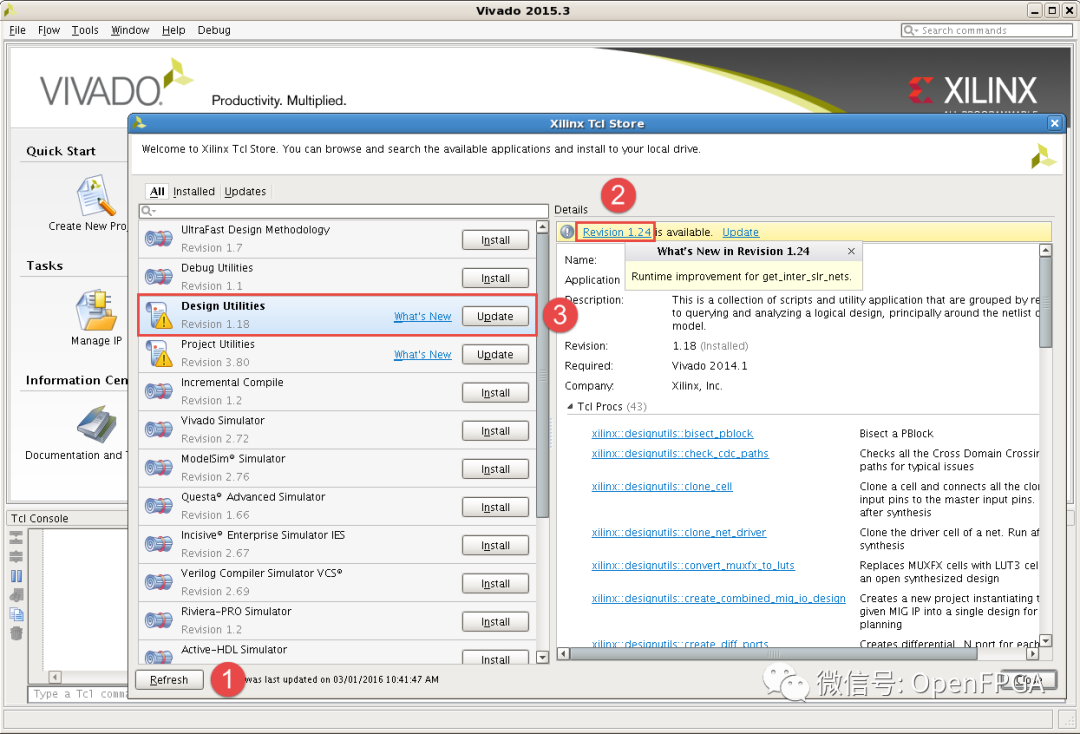

整個(gè)項(xiàng)目使用也是異常簡(jiǎn)單的,而且注意實(shí)時(shí)更新,因?yàn)楣俜綍?huì)經(jīng)常更新一些命令,對(duì)于一些比較成熟的項(xiàng)目,官方會(huì)集成到新的EDA工具中,更新方法如下:

最后,還是感謝各個(gè)大佬開(kāi)源的項(xiàng)目,讓我們受益匪淺。后面有什么感興趣方面的項(xiàng)目,大家可以在后臺(tái)留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見(jiàn)。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1660文章

22410瀏覽量

636273 -

IC

+關(guān)注

關(guān)注

36文章

6410瀏覽量

185618 -

開(kāi)源

+關(guān)注

關(guān)注

3文章

4204瀏覽量

46130

原文標(biāo)題:?FPGA便捷開(kāi)發(fā)-TCL商店(開(kāi)源)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

擁抱開(kāi)源!一起來(lái)做FPGA開(kāi)發(fā)板啦!

【開(kāi)源分享】:開(kāi)源小巧的FPGA開(kāi)發(fā)板——Icepi Zero

在Windows10上運(yùn)行vivado使用tcl文件創(chuàng)建E203項(xiàng)目路徑錯(cuò)誤的問(wèn)題

【開(kāi)源FPGA硬件】硬件黑客集結(jié):開(kāi)源FPGA開(kāi)發(fā)板測(cè)評(píng)活動(dòng)全網(wǎng)火熱招募中......

#硬聲創(chuàng)作季 #FPGA Xilinx開(kāi)發(fā)-08 Vivado里最常用的5個(gè)Tcl命令-3

XILINX FPGA Debug with VIO and TCL

例說(shuō)FPGA連載33:PLL例化配置與LED之使用Tcl Console進(jìn)行引腳分配

FPGA設(shè)計(jì)中Tcl在Vivado中的基礎(chǔ)應(yīng)用

FPGA調(diào)試中常用的TCL語(yǔ)法簡(jiǎn)介

FPGA與STM32開(kāi)發(fā)板開(kāi)源

FPGA與MCU單片機(jī)的綜合開(kāi)發(fā)板開(kāi)源

使用FPGA做的開(kāi)源示波器

開(kāi)源FPGA硬件,核心開(kāi)發(fā)者招募中......

硬件黑客集結(jié):開(kāi)源FPGA開(kāi)發(fā)板測(cè)評(píng)活動(dòng)全網(wǎng)火熱招募中......

?FPGA便捷開(kāi)發(fā)-TCL商店(開(kāi)源)

?FPGA便捷開(kāi)發(fā)-TCL商店(開(kāi)源)

評(píng)論