有的時候需要查找一些官網(wǎng)的例程進(jìn)行學(xué)習(xí)和參考,但是總感覺無從下手,今天就教大家怎么利用官網(wǎng)和Vivado的Documention進(jìn)行相關(guān)的操作。不清楚使用哪些IP或者不清楚需要參考哪個文檔

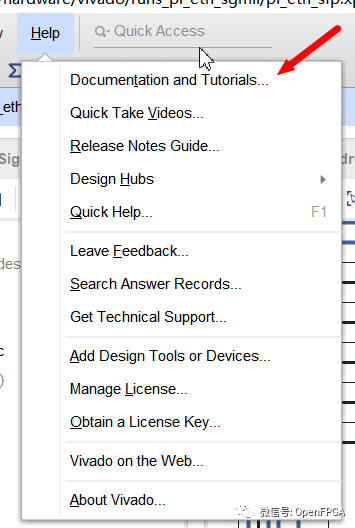

首先點擊Help-->Documention and Tutorials就可以打開XIlinx Documention瀏覽器了。

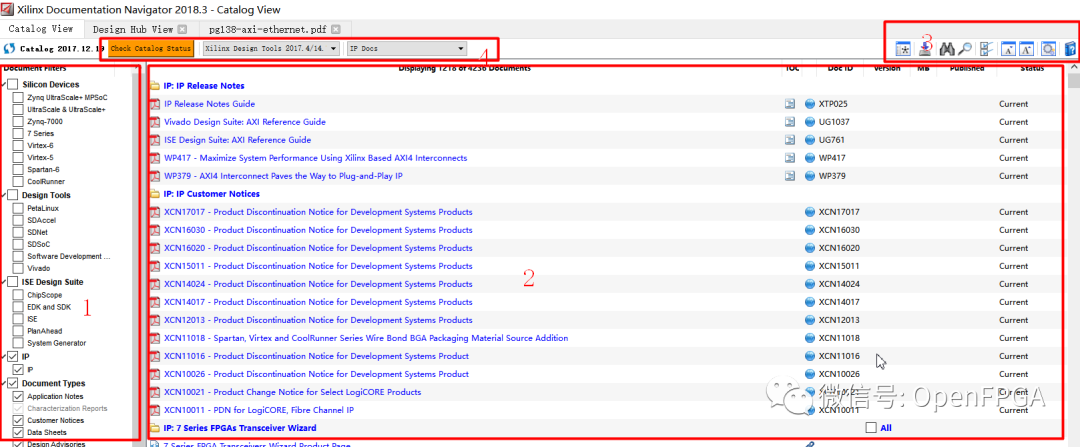

打開后如下:

主要分為:1、分類窗口;2、文件選擇窗口;3、設(shè)置窗口;4、選擇窗口;

可以在3窗口進(jìn)行搜索。

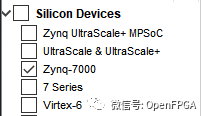

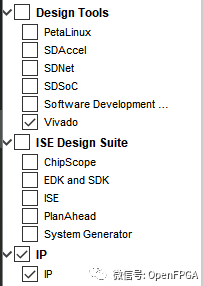

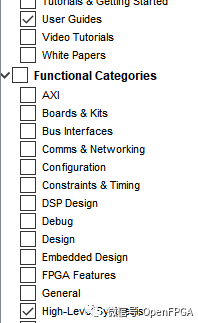

假如現(xiàn)在我需要查找一下7系列FPGA中關(guān)于HLS的使用,那么我可以通過1窗口進(jìn)行分類選擇,如下:

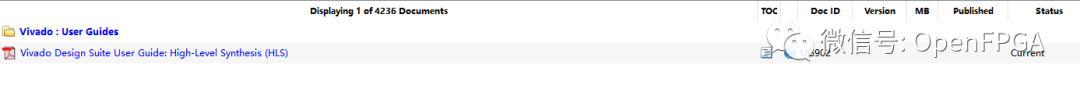

就可以在2窗口得到我想要的文檔:

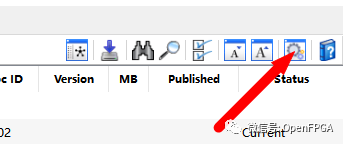

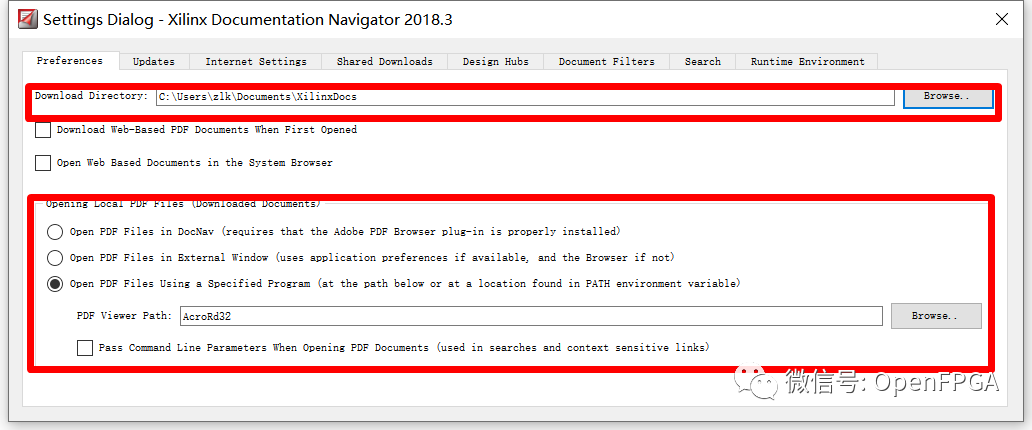

點擊進(jìn)去就可以閱讀,如果想要下載也可以,這里可以進(jìn)行兩種設(shè)置,一是下載路徑設(shè)置二是打開文檔的閱讀器設(shè)置,具體位置如下圖所示:

可以按照自己的需求進(jìn)行設(shè)置。找到了或者已知使用哪種或者哪個IP怎么下載例程

這里提供兩種方式:

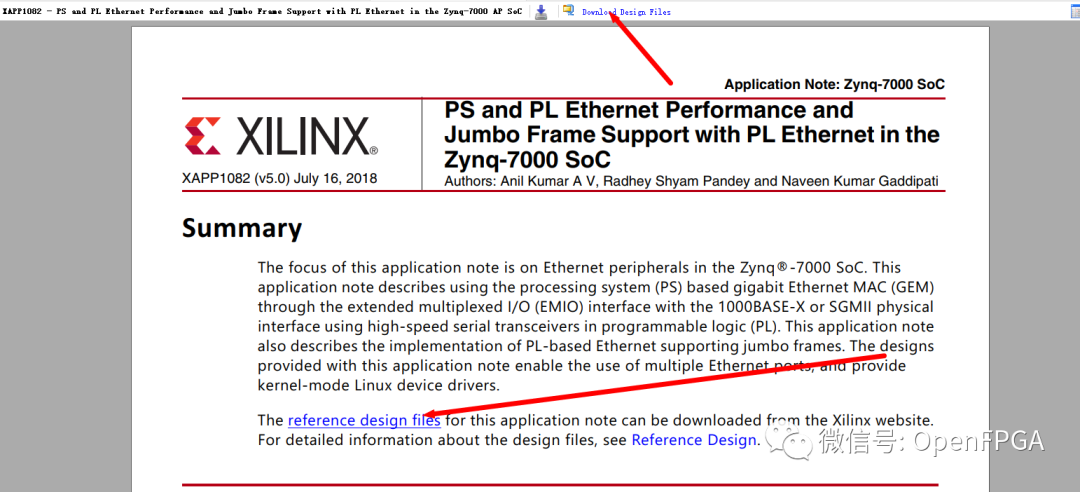

1、使用Xilinx Doc直接搜索相關(guān)的Doc,這里舉例AXI ethernet,相關(guān)的應(yīng)用手冊是xapp1082(還有其他的參考,這里以比較常見的舉例),直接搜索這個文檔,打開后如下圖所示:

這兩個位置可以下載相關(guān)參考例程,直接點擊下載即可,建議該文檔直接使用Chrome打開,點擊鏈接會知道跳轉(zhuǎn),其他PDF閱讀器也可。

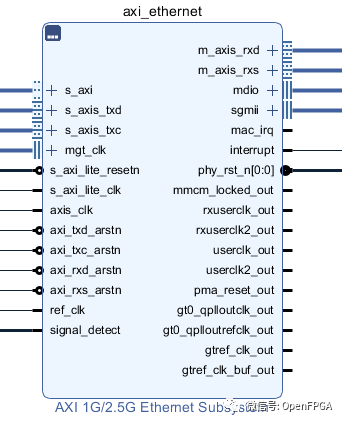

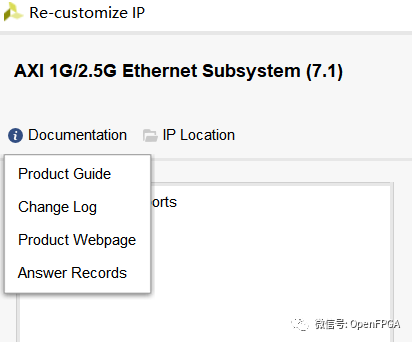

2、在IP管理器里找到該IP

雙擊進(jìn)入

其中左上角的Documentation,有Product Guide等文檔,其中Change Log(修改BUG記錄)、Product Webpage和Answer Records都是比較重要的文檔,對使用好該IP都有很重要的作用,因為與本篇文章不想關(guān),這里就不展開描述了,點擊Product Guide就能通過Xilinx Documentation打開這個文檔,這個文檔相當(dāng)相當(dāng)重要,包括整個IP的使用說明,每個參數(shù)的說明,時序相關(guān),以及一些Debug,仿真相關(guān)說明,如果在使用該IP時出現(xiàn)問題,請仔細(xì)閱讀該文檔,同時該文檔會提供參考示例鏈接(這個IP比較特殊,是兩個IP結(jié)合在一起的,所以沒有refence(瘋狂翻車))。

怎么使用下載下來的參考設(shè)計

目前官網(wǎng)下載下來的參考例程異常“簡單",主要通過TCL腳本提供,對于不熟悉使用該腳本的人可能會比較懵,但是不需要過于擔(dān)心,只需要按照下面的步驟就可以輕松利用該腳本構(gòu)建Vivado工程。

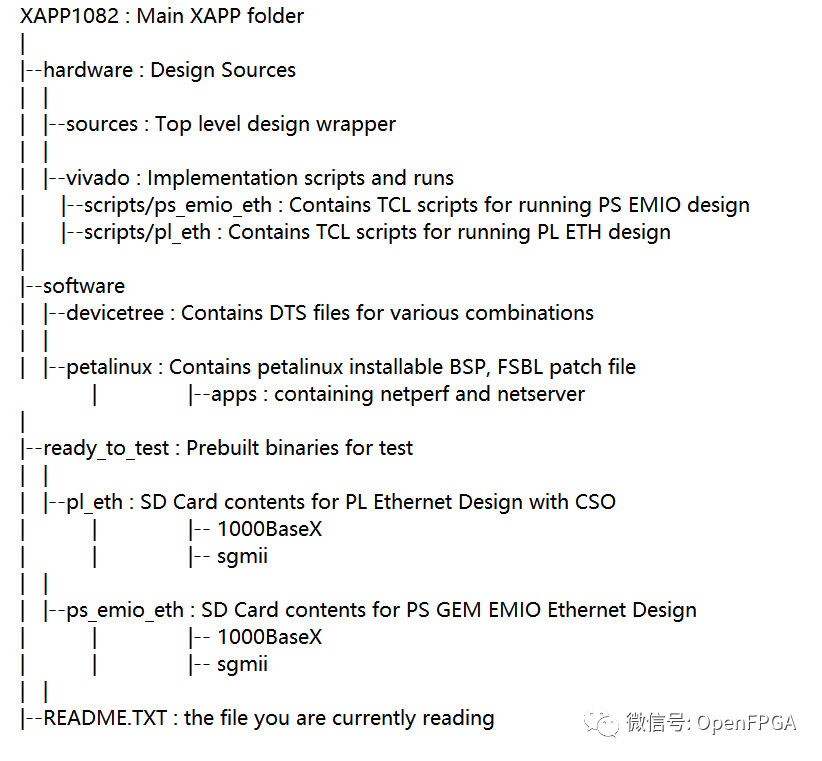

下載下來的參考文件一定要先閱讀readme文件,里面包含了整個例程的作用和文件構(gòu)成,以XAPP1082為例如下:

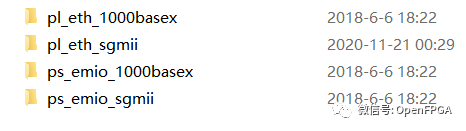

進(jìn)入到xapp1082xapp1082_2017_4hardwarevivadoscripts文件夾下,可以看到四個例程:

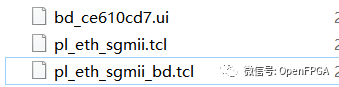

作用就不展開描述了,隨便進(jìn)入一個文件夾下:

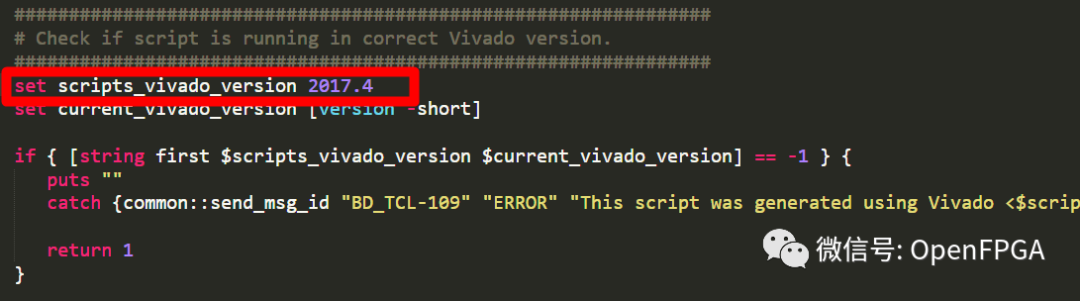

里面只用三個文件,總大小不足100k(要是一個完整的工程,至少要100M左右,所以TCL的作用不言而喻),進(jìn)如這個文件夾主要想要確認(rèn)下導(dǎo)出該腳本的Vivado版本(不確認(rèn)的話,后期運行會報錯),外層文件夾已經(jīng)有相關(guān)的版本說明了(xapp1082_2017_4)打開pl_eth_sgmii_bd.tcl(記事本及相關(guān)文本閱讀器都可以):

如果你的Vivado版本和這個一樣,那么不需要修改,如果不一樣請修改和你的版本一樣,我使用的是Vivado2018.3,修改如下:

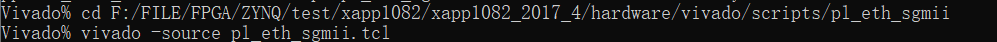

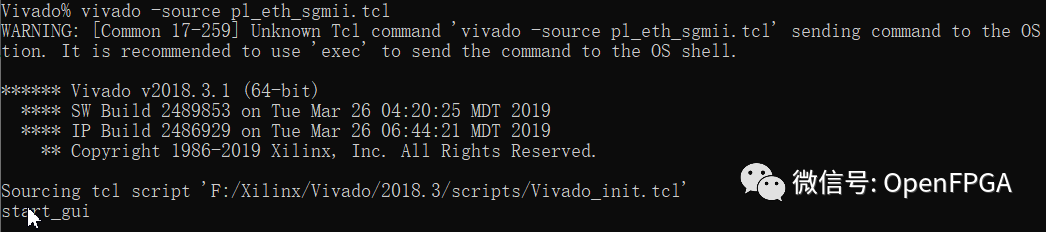

接下來打開Linux terminal or Vivado tcl shell in windows

通過CD命令進(jìn)入歷程所在的文件夾:

注意這里是“/”不是WIN系統(tǒng)常用的“”,之后執(zhí)行:

vivado -source pl_eth_sgmii.tcl

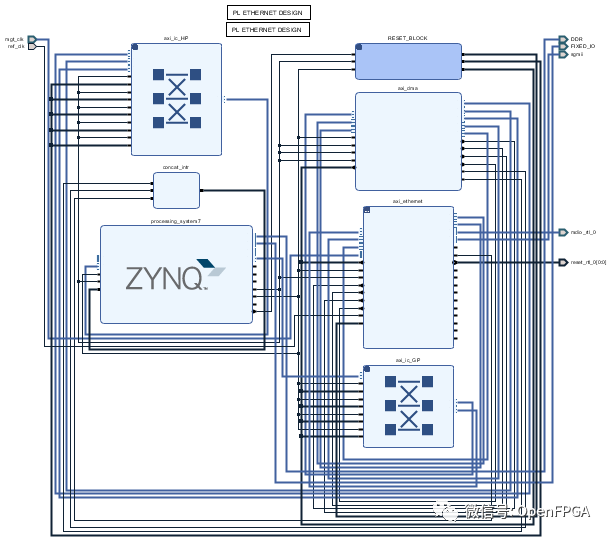

就可以打開Vivado并自動構(gòu)建Demo了:

這里說明一下,我使用的Vivado版本和例程版本不相同所以構(gòu)建完成后會有一些小Bug,按照提示修改即可。

構(gòu)建的工程保存在如下路徑:

責(zé)任編輯:xj

原文標(biāo)題:【Vivado那些事】如何查找官網(wǎng)例程及如何使用官網(wǎng)例程

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

IP

+關(guān)注

關(guān)注

5文章

1863瀏覽量

155843 -

Vivado

+關(guān)注

關(guān)注

19文章

857瀏覽量

71112

原文標(biāo)題:【Vivado那些事】如何查找官網(wǎng)例程及如何使用官網(wǎng)例程

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

利用 NucleiStudio IDE 和 vivado 進(jìn)行軟硬件聯(lián)合仿真

利用vivado實現(xiàn)對e200_opensource 蜂鳥E203一代的仿真

vivado時序分析相關(guān)經(jīng)驗

沒有開發(fā)板的情況,在Vivado上進(jìn)行蜂鳥E203的基礎(chǔ)內(nèi)核的drystone跑分

沒有開發(fā)板的情況下,在Vivado上進(jìn)行蜂鳥E203的基礎(chǔ)內(nèi)核的drystone跑分

vcs和vivado聯(lián)合仿真

如何在vivado上基于二進(jìn)制碼對指令運行狀態(tài)進(jìn)行判斷

在vivado上基于二進(jìn)制碼對指令運行狀態(tài)進(jìn)行判斷

vivado仿真時GSR信號的影響

電子元器件貿(mào)易企業(yè)官網(wǎng)SEO優(yōu)化操作手冊(2025版)

Vivado無法選中開發(fā)板的常見原因及解決方法

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

Vivado HLS設(shè)計流程

怎么利用官網(wǎng)和Vivado的Documention進(jìn)行相關(guān)的操作

怎么利用官網(wǎng)和Vivado的Documention進(jìn)行相關(guān)的操作

評論