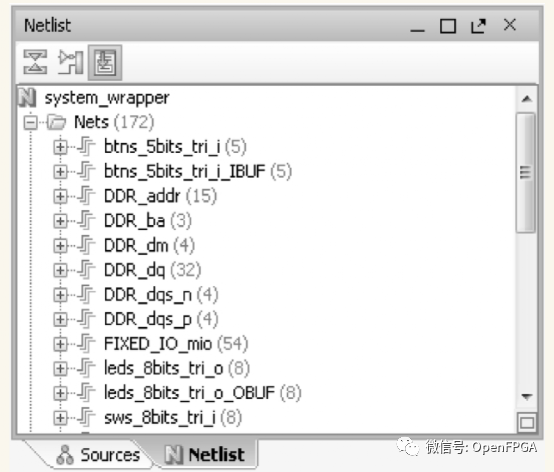

我們都知道FPGA的實現過程分為2步:分析綜合與布局布線后就可以產生目標文件,這兩個步驟中間有個非常重要的文件,那就是-網表。 下圖是Vivado中網表列表示例:

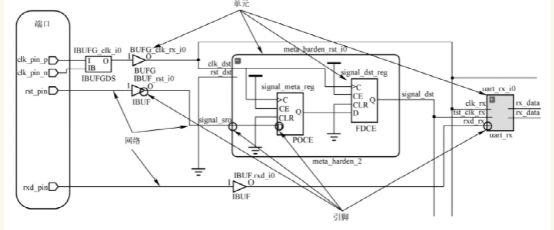

Vivado中網表列表示例 在vivado集成環境中,網表時對設計的描述,如網表由單元(cell)、引腳(pin)、端口(port)和網絡(Net)構成。下圖是一個電路的網表結構:

電路的網表結構

(1)單元是設計單元

1、設計模塊(Verilog HDL)/實體(VHDL)。

2、元件庫中的基本元素(Basic Elements ,BLEs)實例。如LUT、FF、DSP、RAM等。

3、硬件功能的類屬表示。

4、黑盒。

(2)引腳是單元上的連接點

(3)端口是設計的頂層端口

(4)網絡用于實現引腳之間,以及引腳到端口的連接。

編輯:jq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8244瀏覽量

366643 -

RAM

+關注

關注

8文章

1399瀏覽量

120564 -

端口

+關注

關注

4文章

1104瀏覽量

33966

原文標題:【Vivado那些事】Vivado中電路結構的網表描述

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

vivado連接Atry A7-35T死機怎么解決?

時可以順利調用vivado,只是沒有用其他電路板測試過;

3)安裝了digilent的驅動(install_drivers),并拷貝其board file到vivado的board file目錄

發表于 11-07 06:05

Windows系統下用vivado將電路燒寫到MCU200T板載FLASH的方法

在Windows操作系統下使用vivado將設計的電路燒寫到MCU200T開發板上的FLASH中的方法。通過將硬件電路的比特流文件燒寫到板載FLASH內,開發板上電時將自動地從FLAS

發表于 10-29 08:21

在VIVADO中對NICE進行波形仿真的小問題的解決

https://www.rvmcu.com/community-topic-id-386.html

以上鏈接為如何生成.verilog,并在VIVADO中生成波形的例子。我們在實踐過程中,發現了兩個

發表于 10-27 06:41

vcs和vivado聯合仿真

文檔中明確描述vivado2021.2版本對應VCS的版本是2020.12,由于license問題所以選擇vcs2018的版本;雖然目前與官方的版本不匹配,但是不影響正常使用;

使用tcl界面

發表于 10-24 07:28

AMD Vivado ChipScope助力硬件調試

許多硬件問題只有在整個集成系統實時運行的過程中才會顯現出來。AMD Vivado ChipScope 提供了一套完整的調試流程,可在系統運行期間最大限度提升對可編程邏輯的觀測能力,助力設計調試。

Vivado無法選中開發板的常見原因及解決方法

對應的器件信息和約束文件(XDC),大大簡化工程初始化流程。然而,在某些情況下,我們可能會發現 Vivado 的界面中無法選中目標開發板,導致只能手動選擇器件。那么,遇到這種情況該如何處理呢?

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結果(以 Vivado 2024.2 為例)。

Vivado HLS設計流程

為了盡快把新產品推向市場,數字系統的設計者需要考慮如何加速設計開發的周期。設計加速主要可以從“設計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx 推出的 Vivado HLS 工具可以

一文詳解Vivado時序約束

Vivado的時序約束是保存在xdc文件中,添加或創建設計的工程源文件后,需要創建xdc文件設置時序約束。時序約束文件可以直接創建或添加已存在的約束文件,創建約束文件有兩種方式:Constraints Wizard和Edit Timing Constraints,在綜合后

Vivado中電路結構的網表描述

Vivado中電路結構的網表描述

評論