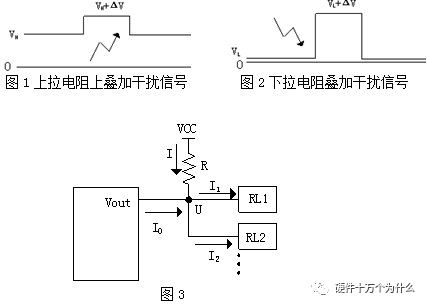

所謂上,就是指高電平;所謂下,是指低電平。上拉,就是通過一個電阻將信號接電源,一般用于時鐘信號數據信號等。下拉,就是通過一個電阻將信號接地,一般用于保護信號。

這是根據電路需要設計的,主要目的是為了防止干擾,增加電路的穩定性。

假如沒有上拉,時鐘和數據信號容易出錯,畢竟,CPU的功率有限,帶很多BUS線的時候,提供高電平信號有些吃力。

而一旦這些信號被負載或者干擾拉下到某個電壓下,CPU無法正確地接收信息和發出指令,只能不斷地復位重啟。

假如沒有下拉,保護電路極易受到外界干擾,使CPU誤以為被保護對象出問題而采取保護動作,導致誤保護。

上拉下拉,要根據電路要求來設置。

上拉電阻一般是一端接電源,一端接芯片管腳的電路中的電阻,下拉電阻一般是指一端接芯片管腳一端接地的電阻。

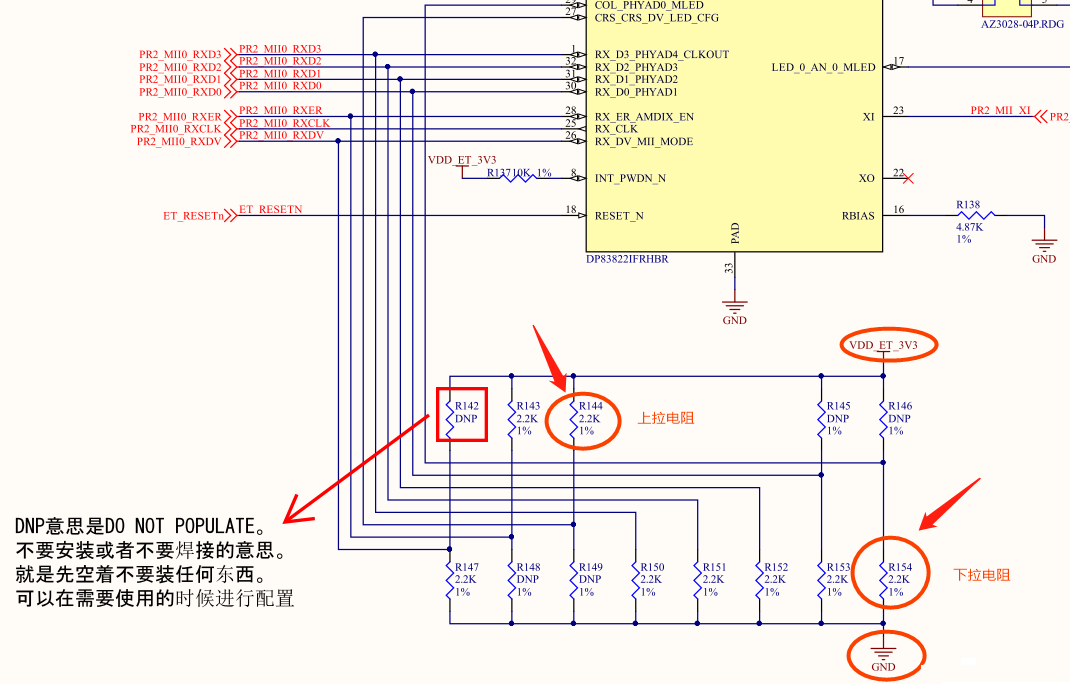

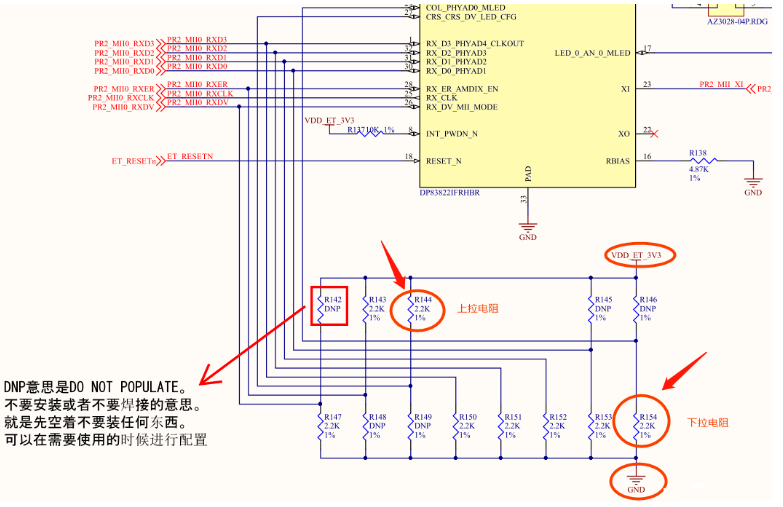

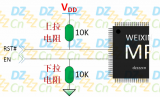

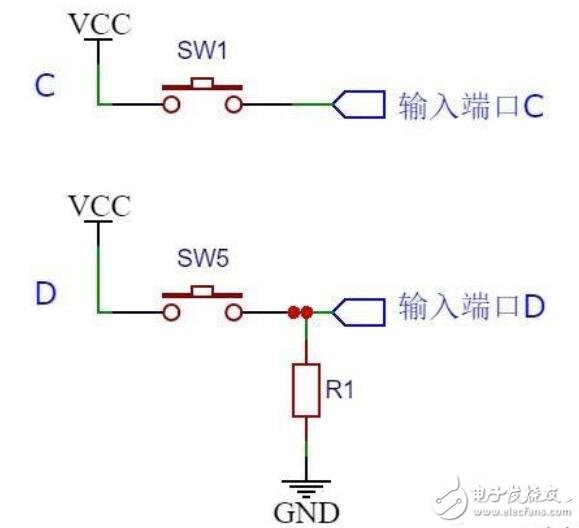

如下圖的兩個Bias Resaitor 電阻就是上拉電阻和下拉電阻。圖中,上部的一個Bias Resaitor 電阻因為是接地,因而叫做下拉電阻,意思是將電路節點A的電平向低方向(地)拉;同樣,圖中,下部的一個Bias Resaitor 電阻因為是電源(正),因而叫做上拉電阻,意思是將電路節點A的電平向高方向(電源正)拉。當然,許多電路中上拉下拉電阻中間的那個12k電阻是沒有的或者看不到的。我找來這個圖是RS-485/RS-422總線上的,可以一下子認識上拉下拉的意思。但許多電路只有一個上拉或下拉電阻,而且實際中,還是上拉電阻的為多。

上拉下拉電阻的主要作用是在電路驅動器關閉時給線路(節點)以一個固定的電平。

1 在RS-485總線中,它們的主要作用就是在線路所有驅動器都釋放總線時讓所有節點的A-B端電壓在200mV或200mV以上(不考慮極性)。不然,如果接收器輸入端A和B間的電平低于±200mV(絕對值小于200mV),接收器輸出的邏輯電平將被當作所傳輸數據的末位而被接收起來,這樣顯然是極容易產生通訊錯誤的。

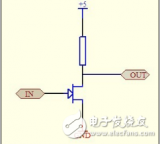

2 最容易見到的上拉電阻應當是NE555電路7腳作為輸出用的時候。實際上,它和一個三極管的C極或MOS管的D極有一個電阻接到電源+上是一樣道理的。它的作用就是:當管子(晶體管或MOS管)輸入關斷電平時,C極或D極有一個高電平(空載時約等于電源電壓);當管子(晶體管或MOS管)輸入導通電平時,C極或D極將與電源地(-)接通,因而有一個低電平。理想的應為0V,但因為管子有導通電阻,因而有一定的電壓,不同的管子可能不一樣,相同的管子也可能因參數差異而小有差別,即便是真正的金屬接觸的電源開關,也是有接觸電阻/導通壓降(雖然不同電流下壓降不同)的;僅僅就導通而言,對于不同系列的集成電路來說,因為應用對象不同,導通后的輸出電壓有不同的規定,典型是TTL電平和CMOS電平的不同。這方面超過了本問題的內容,將日志里另外處理。

3 建議:自己實驗或用仿真軟件看看。

上拉電阻和下拉電阻的區別

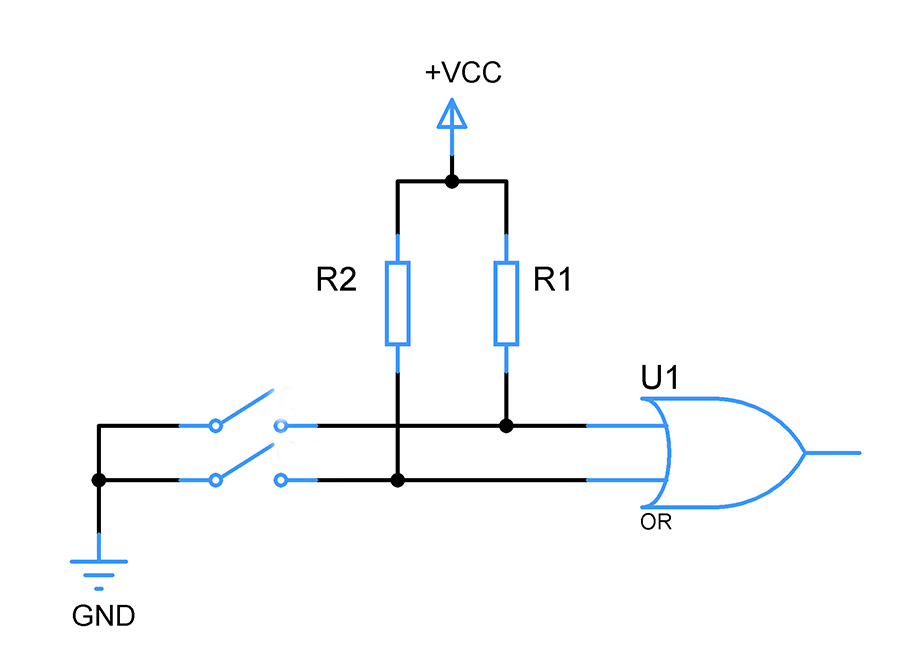

上拉電阻和下拉電阻2者共同的作用是:避免電壓的“懸浮”,造成電路的不穩定;

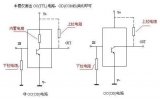

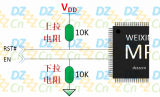

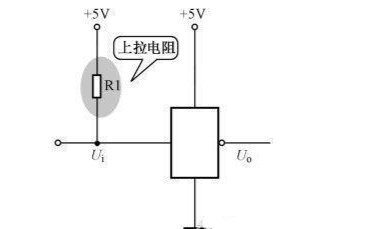

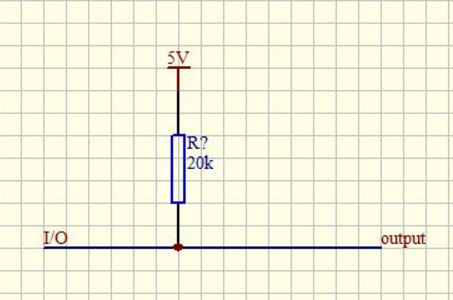

一、上拉電阻如圖所示:

1、概念:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平;

2、上拉是對器件注入電流;灌電流;

3、當一個接有上拉電阻的IO端口設置為輸入狀態時,它的常態為高電平;

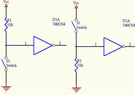

二、下拉電阻如圖所示:

1、 概念:將一個不確定的信號,通過一個電阻與地GND相連,固定在低電平;

2、下拉是從器件輸出電流;拉電流;

3、當一個接有下拉電阻的IO端口設置為輸入狀態時,它的常態為低電平;

上拉電阻很大,提供的驅動電流很小,叫弱上拉;反之叫強上拉。

為什么要使用拉電阻:

上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用,下拉同理。上拉是對器件注入電流,下拉是輸出電流,弱強只是上拉電阻的阻值不同,沒有什么嚴格區分。

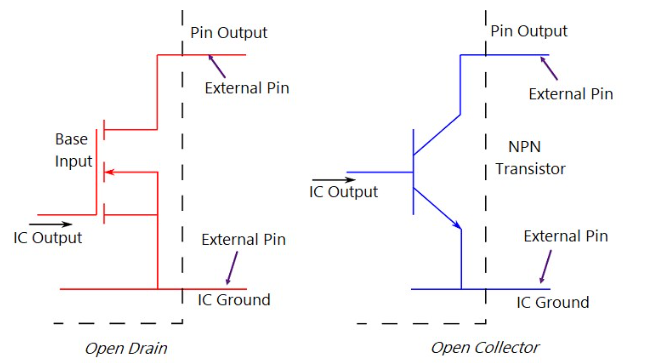

對于非OC、OD輸出型電路提升電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開路輸出型電路輸出電流通道。

上拉電阻的主要應用:

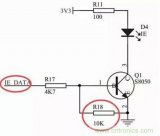

1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

2、OC門電路要輸出“1”時需要加上拉電阻,不加根本就沒有高電平。

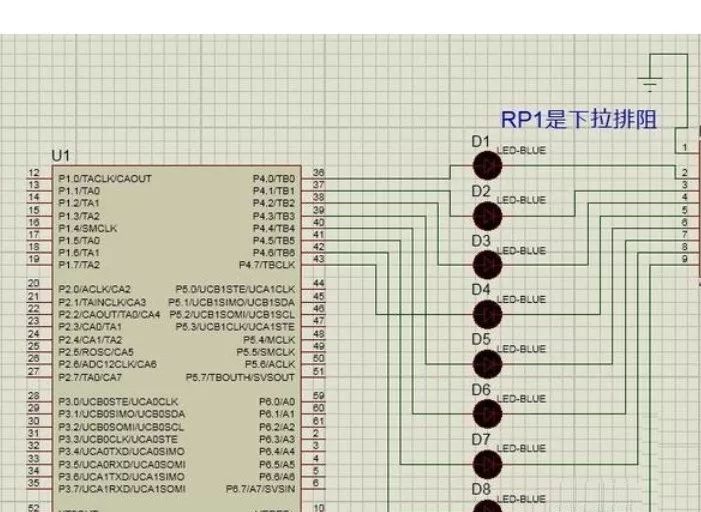

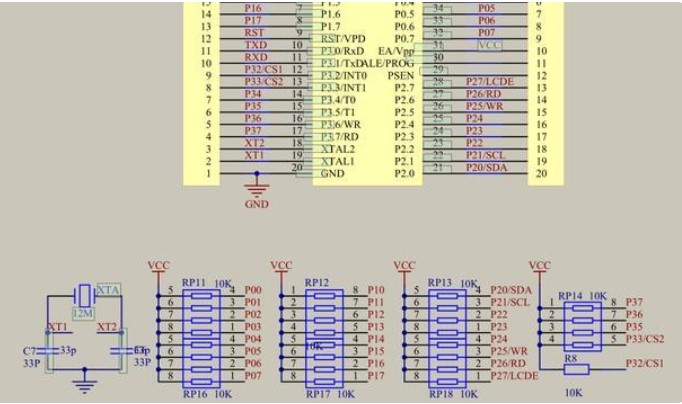

3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻,但在用OC門作驅動(例如:控制一個 LED)灌電流工作時就可以不加上拉電阻。

4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產生降低輸入阻抗,提供泄荷通路。

5、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。

6、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

上拉電阻阻值的選擇原則包括:

1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。

2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。

3、對于高速電路,過大的上拉電阻可能邊沿變平緩。

綜合考慮以上三點,通常在1k到10k之間選取。對下拉電阻也有類似道理。

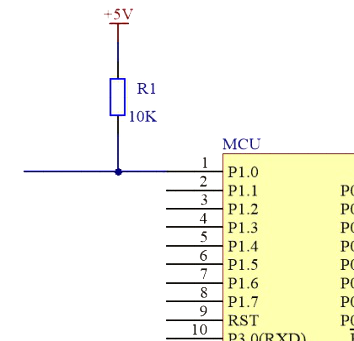

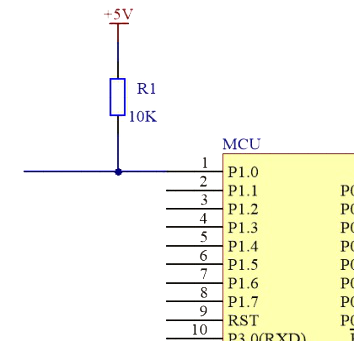

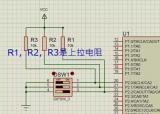

在很多單片機電路中,其I/O管腳檢測信號是以高、低電平來判斷是否有信號變化的,比如5V為高電平;0V為低電平。那么這些管腳如果不接上拉電阻的話,其電平信號就可能是隨機的了,0V~5V之間不一定是什么狀態,這樣的話單片機就不能正確地判斷是不是有信號電平變化了。因此給I/O管腳上接一個上拉電阻使它的檢測信號由不確定電平狀態拉到5V電平,單片機就能準確地判斷是不是有信號變化了。同理,還有下拉電阻,把不確定電平狀態拉到0V,使系統更加穩定。

上拉電阻的作用原理

單片機上拉電阻作用

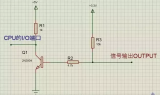

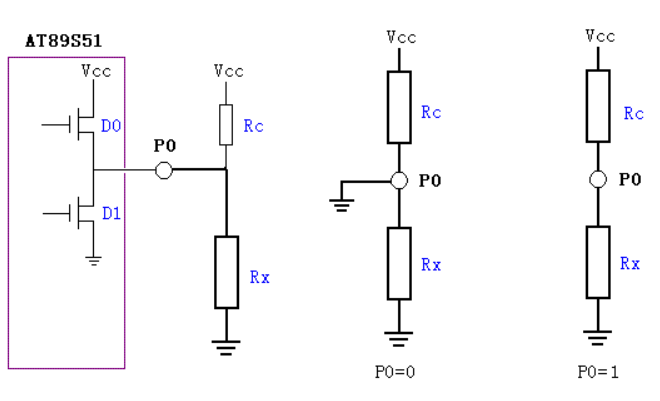

1. 場效應管的漏極開路門電路如下:

圖中上拉電阻作用分析如下:

管子導通或截止可以理解為單片機的軟件時端口置1或0.

(1)如果沒有上拉電阻(10k),將5V電源直接與場效應管相連。

當管子導通時, 管子等效一電阻,大小為1k左右,因此5v電壓全部加在此等效電阻上,輸出端Vout=5v。

當管子截止時,管子等效電阻很高,可以理解為無窮大,因此5v的電壓也全部加在此等效電阻上,Vout=5v。

在這兩種情況下,輸出都為高電平,沒有低電平。

(2)如果有上拉電阻(10k),將5v電源通過此上拉電阻與與場效應管相連。

當管子導通時, 管子等效一電阻,大小為1k左右,與上拉電阻串聯,輸出端電壓為加在此等效電阻上的電壓,其大小為Vout = 5v * 管子等效電阻/(上拉電阻+管子等效電阻)=5v * 1/(10+1) = 低電平。

當管子截止時, 管子等效電阻很高,可以理解為無窮大,其與上拉電阻串聯,輸出端電壓為加在此等效電阻上的電壓,其大小為Vout = 5v * 管子等效電阻/(上拉電阻+管子等效電阻)=5v * 無窮大 /(無窮大+1) = 高電平。

由(1)和(2),可以分析出等效電阻的作用。

電子發燒友App

電子發燒友App

評論