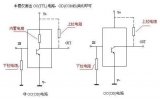

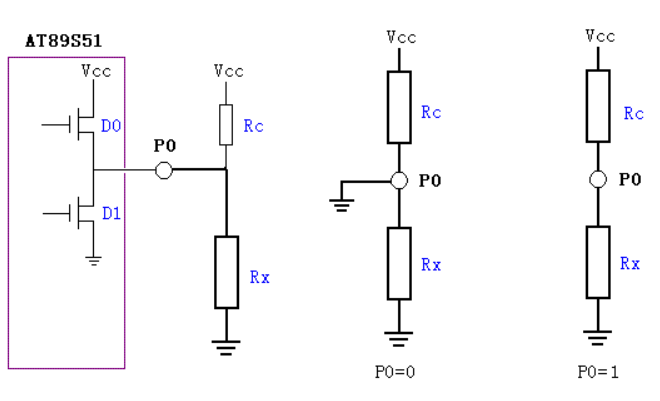

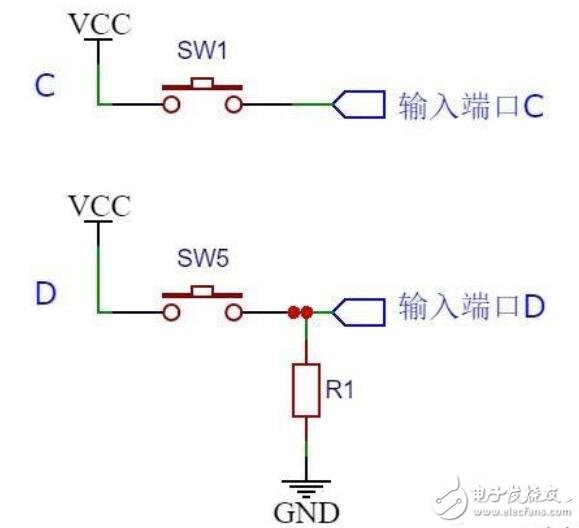

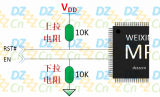

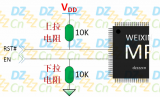

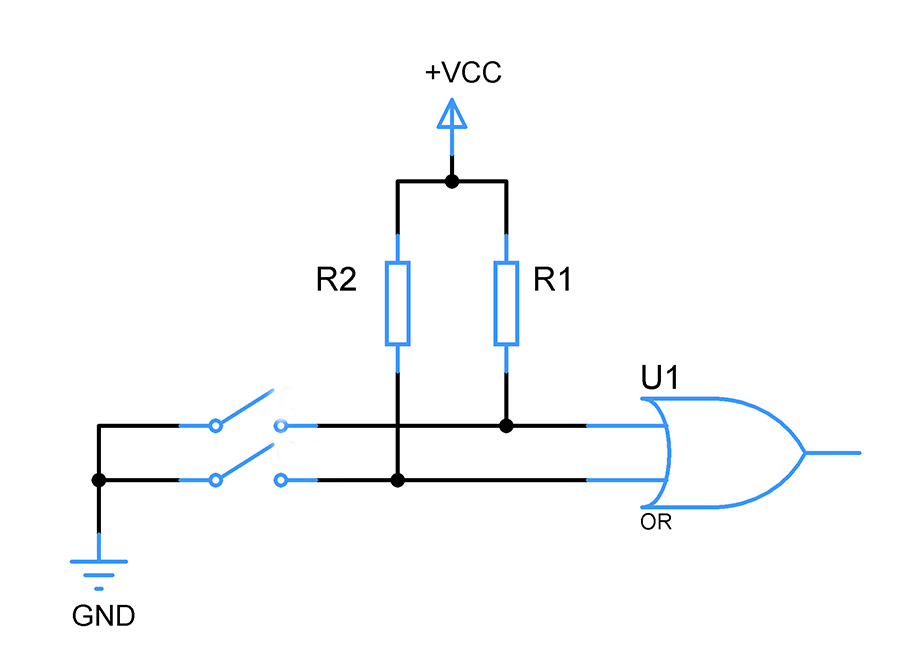

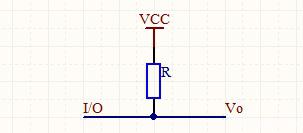

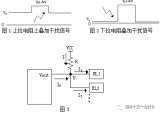

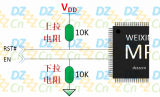

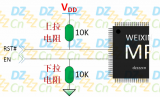

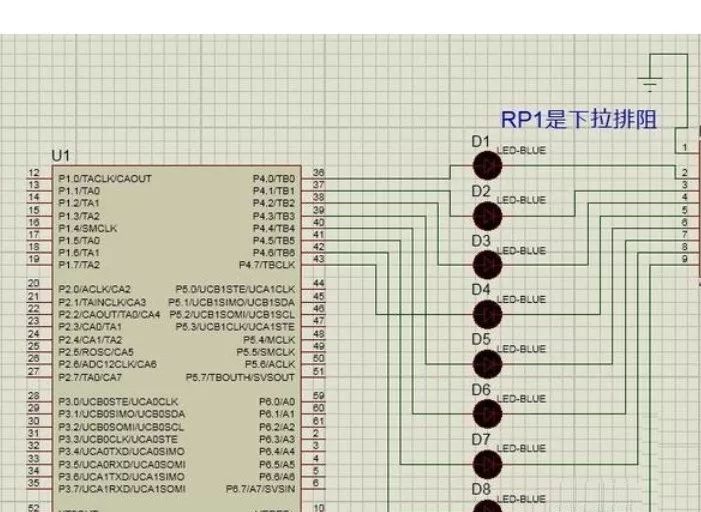

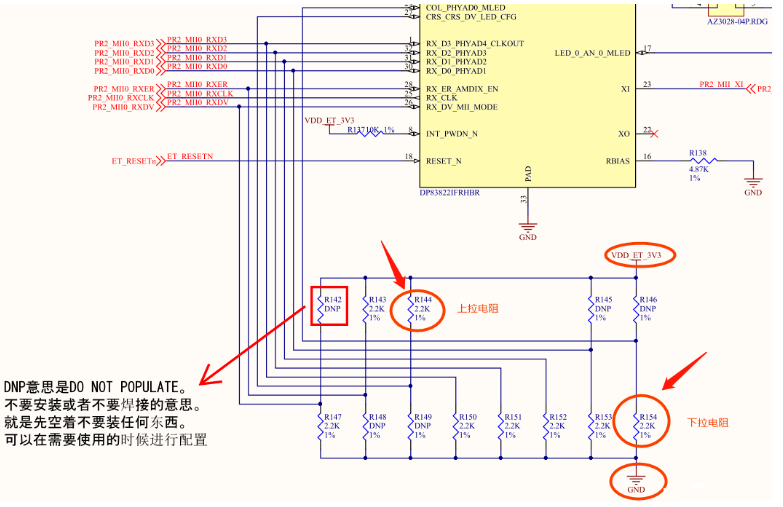

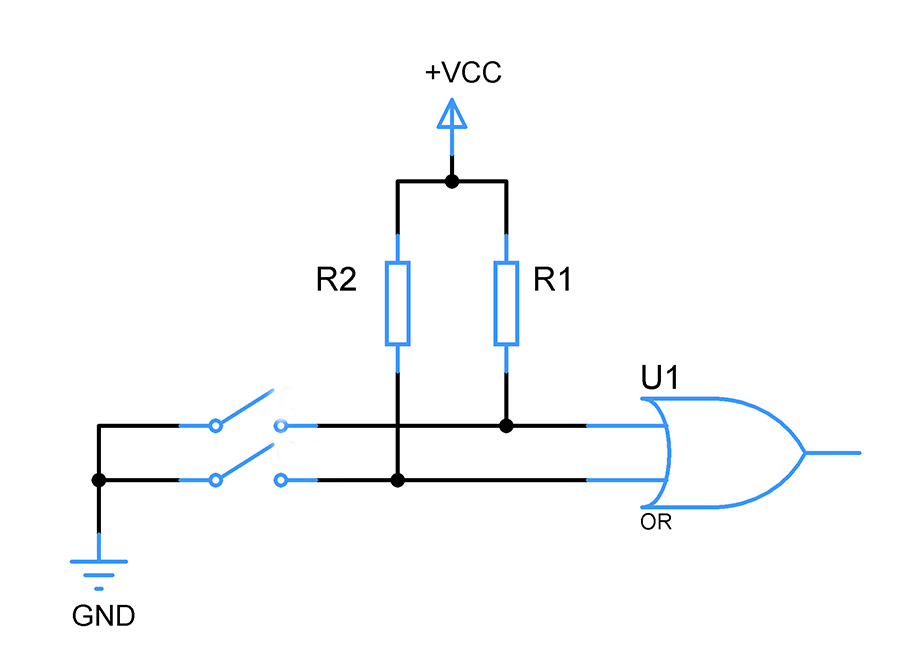

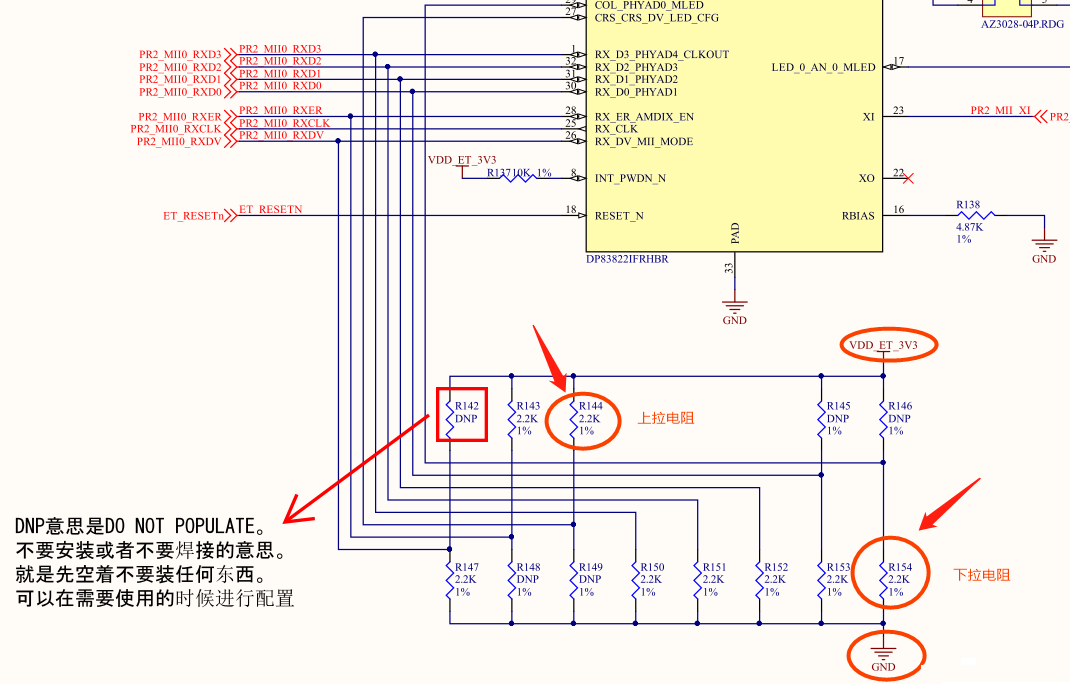

一、上下拉電阻介紹 ??上拉電阻:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平。作用:上拉是對器件注入電流;灌電流;當一個接有上拉電阻的IO端口設置為輸入狀態時,它的常態為高電平

2023-04-21 09:49:34 18737

18737 什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。那么,上拉電阻和下拉電阻的用處和區別分別又是什么呢?

2023-05-26 10:16:01 4487

4487

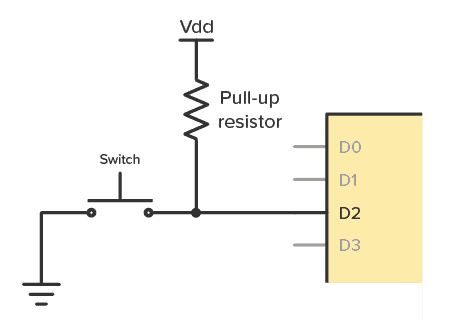

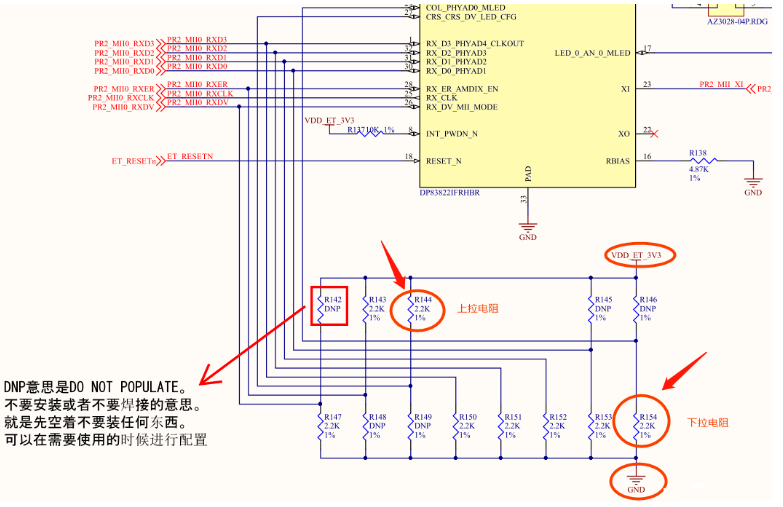

個電阻將其箝位至高電平(上拉)或低電平(下拉),但是無論具體用法如何,這個基本的作用都是相同的,只是在不同應用場合中會對電阻的阻值要求有所不同,下面一起來了解它們吧。

2023-06-07 15:20:05 4302

4302

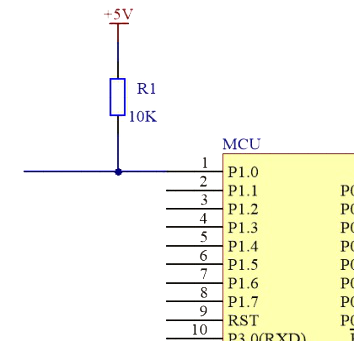

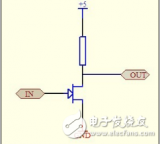

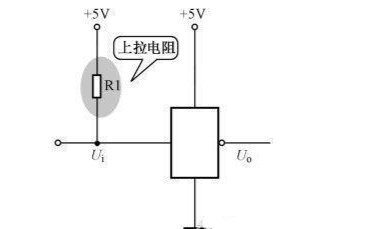

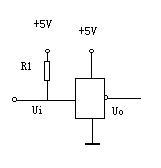

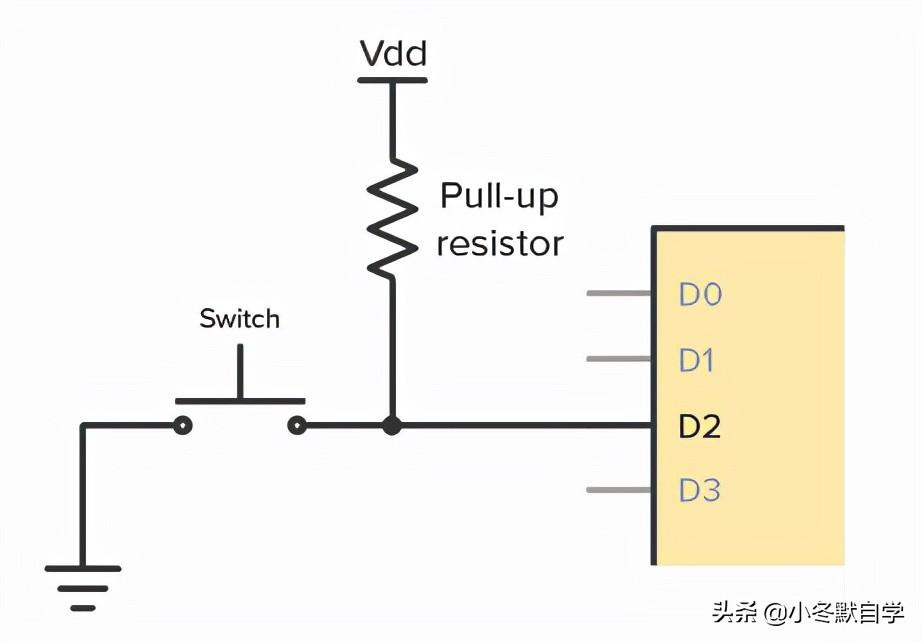

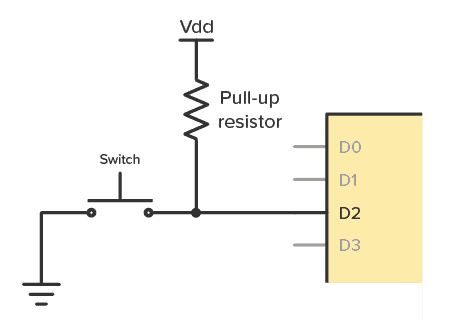

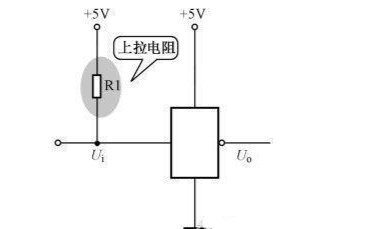

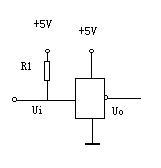

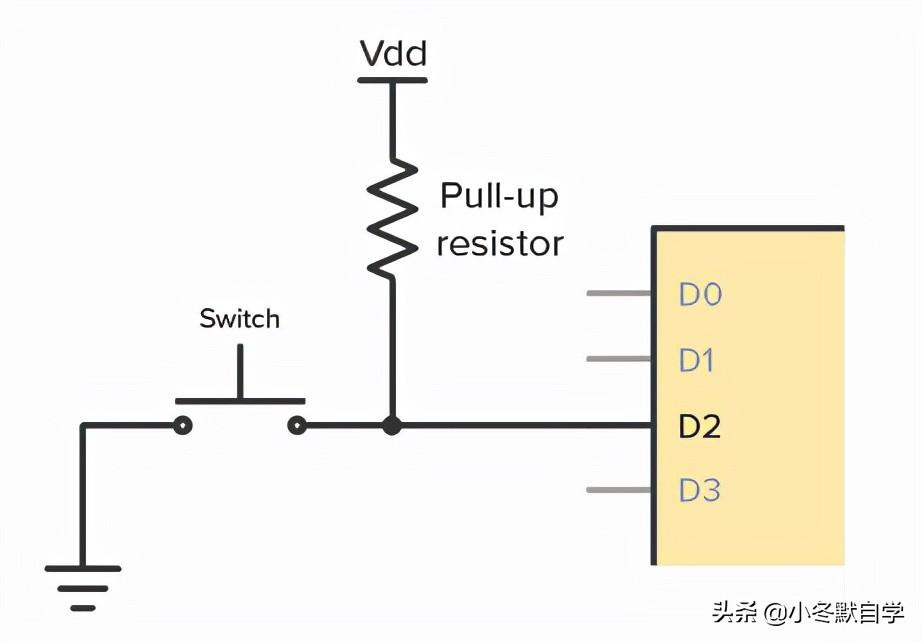

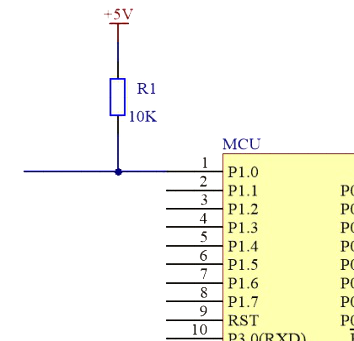

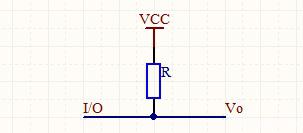

在構建電路時,常會使用到上拉電阻,我們經常在一些數字電路中看到它。它只是一個電阻,從輸入端連接到電路的正電源VDD。

2023-07-06 10:58:01 8751

8751

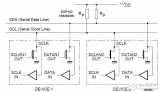

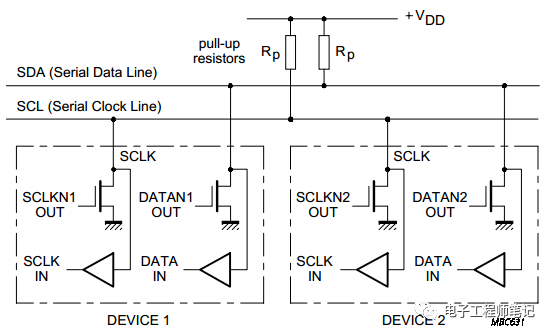

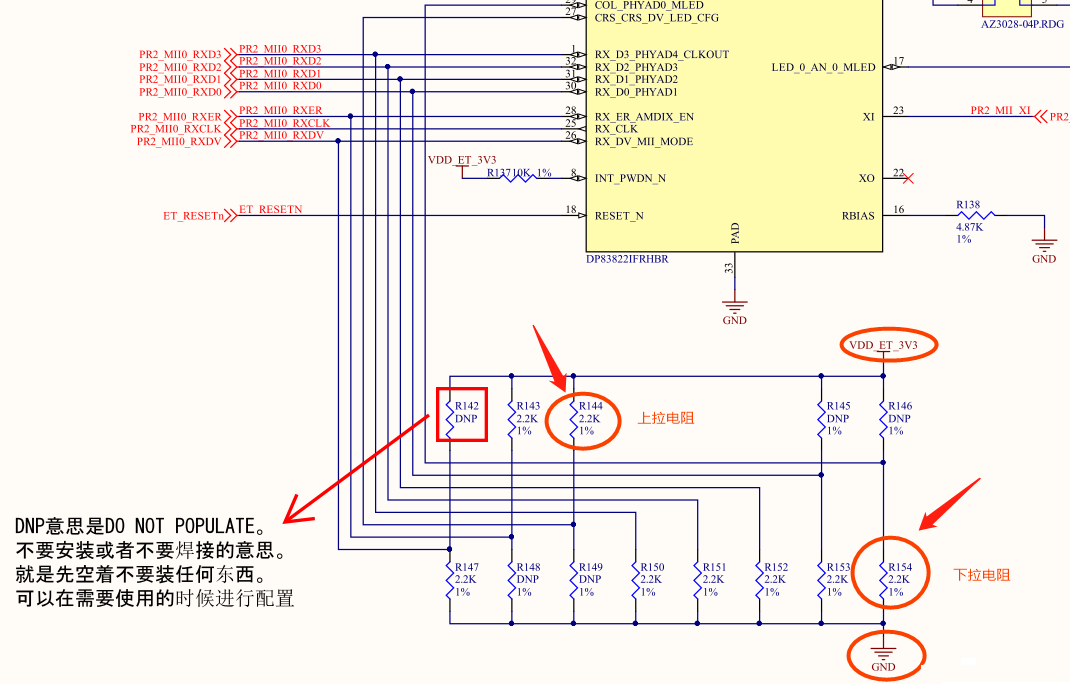

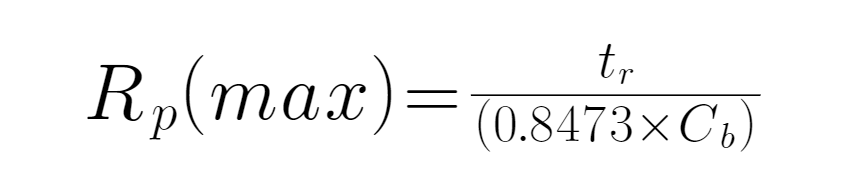

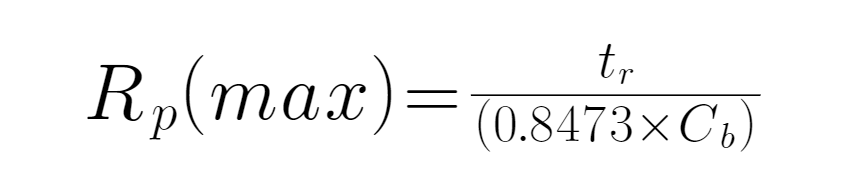

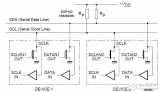

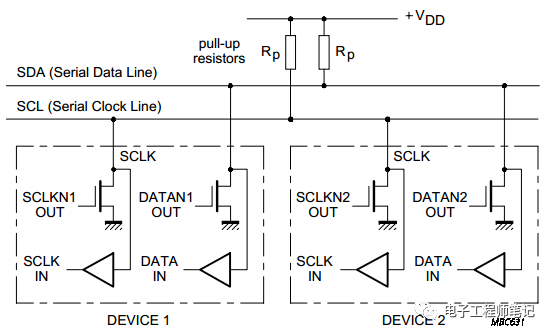

導讀I2C總線在產品設計中被廣泛應用,盡管其結構簡單,但經常發生上拉電阻設計不合理的問題。本文將對I2C上拉電阻的選擇進行簡要分析。一根信號線上,通過電阻連接一個固定的高電平VCC,信號線初始、空閑

2024-12-27 11:34:09 2595

2595

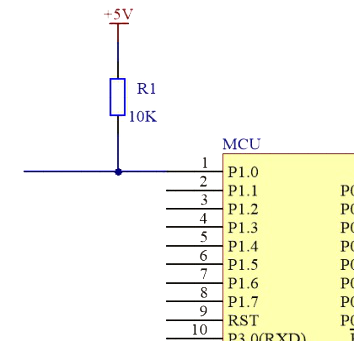

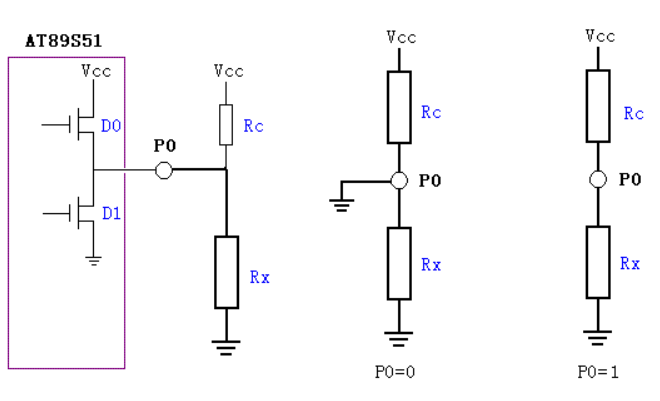

使用外部可調電阻上拉(PORTX為0),管腳電壓隨著外部上拉電阻的阻值的下降而升高,當外部可調電阻的組織大約是40K時,該管腳電壓接近Vcc供電電壓,并且降低電阻,電壓也不再升高。總結出一個規律,如果使用外部上拉電阻,該阻值應該不能超過40K,否則該引腳的電壓將不能到達Vcc的電壓。

2011-11-15 14:10:42

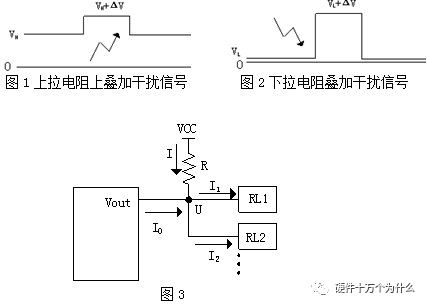

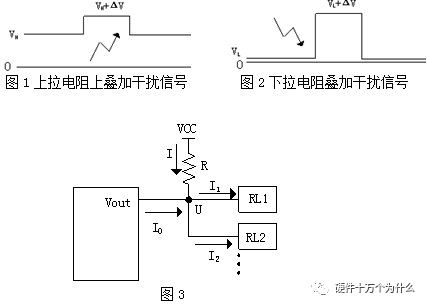

的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、 從節約功耗及芯片

2017-08-28 09:27:18

的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、 從節約功耗及芯片

2017-11-16 17:14:38

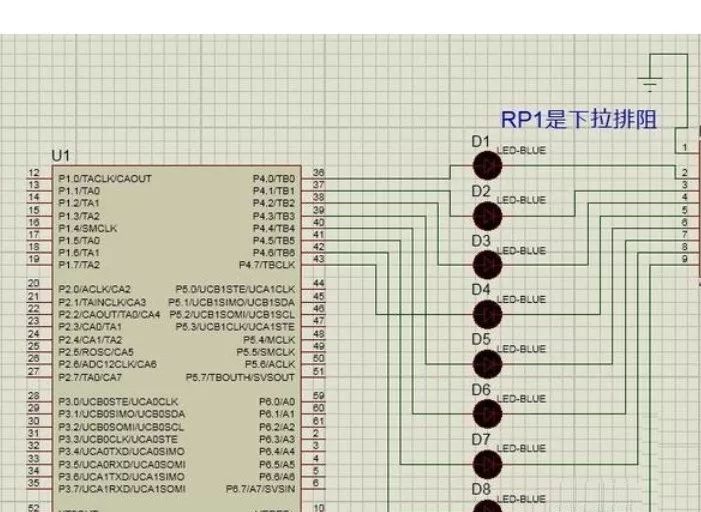

下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速

2011-09-19 08:55:51

下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速

2008-05-22 08:46:35

。 四、上拉電阻阻值選擇原則: 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。 3、對于高速電路,過大的上拉電阻可能

2018-10-19 16:30:19

。 7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 上拉電阻阻值的選擇原則包括: 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2

2019-06-27 05:55:08

高電平。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能邊沿變平緩。

2021-12-01 11:15:35

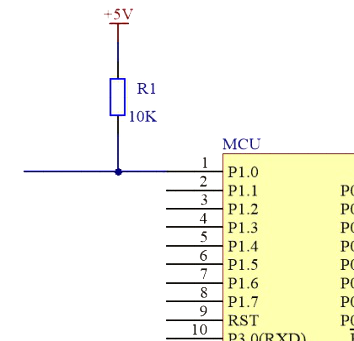

上拉電阻有什么作用?如何去計算上拉電阻的阻值?51型單片機IO口有什么特點?AVR單片機IO口的輸入狀態有哪幾種?

2021-07-07 07:29:25

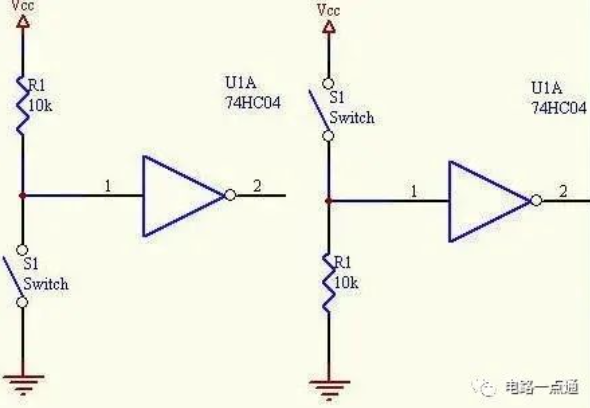

。2、OC 門電路必須加上拉電阻,以提高輸出的搞電平值。3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉...

2021-07-27 06:52:51

引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。(二)上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠

2014-05-12 08:24:37

,有效的抑制反射波干擾。上拉電阻阻值的選擇原則包括:從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。EDA365論壇網站|PCB論壇網|PCB layout論壇|PCB設計論壇|SI仿真技術

2014-11-17 10:24:15

波干擾。 8、在數字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。 四、上拉電阻阻值選擇原則 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2、從確保足夠

2020-12-14 17:21:30

! -------上拉是對器件注入電流,下拉是輸出電流 -------弱強只是上拉電阻的阻值不同,沒有什么嚴格區分 -------對于非集電極(或漏極)開路輸出型電路(如普通門電路)提升電流和電壓的能力是有限

2018-06-28 06:21:54

CYW5557x 上的內部上拉/下拉電阻值是多少?

我想知道的值是帶引腳(GPIO_1 和 GPIO_12)的電阻值,

以及其他 GPIO 較弱的內部上拉/下拉電阻值。

謝謝。

2025-07-17 07:03:30

IO內置上拉電阻的阻值是多少?所有IO都有內置上拉電阻么,阻值是否一樣?

2024-02-21 06:17:58

Quartus II 中管腳上拉電阻(弱上拉)的設置方法:

2015-05-13 17:06:07

Quartus II 中管腳上拉電阻(弱上拉)的設置方法Quartus II 中管腳上拉電阻(弱上拉)的設置方法在使用 Altera 的 FPGA 時候,根據系統設計需要在管腳的內部加上上拉電阻

2012-08-12 16:10:09

我現在遇到一個問題HDC1080 SDA引腳與STM32F031F6 PA7相連,頻率從1k到100K,上拉電阻為1K和10K時,STM32F031F6檢測的數據都是滿偏AD值,在SDA總線上加一個

2018-09-26 17:03:56

。6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。上拉電阻阻值的選擇原則 從灌電流的能力

2018-03-06 14:49:03

上拉下拉電阻的定義以及用法為什么要使用拉電阻上拉電阻阻值的選擇原則

2021-04-06 06:06:42

電阻,以提高輸出高電平的值。2、OC門電路必須使用上拉電阻,以提高輸出的高電平值。3、為增強輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在CMOS芯片上,為了防止靜電造成損壞,不用的管腳

2022-01-14 07:43:57

在選擇上拉電阻值時,要根據系統實際情況在功耗和速度上兼顧。

從IC(MOS工藝)的角度,分別就輸入/輸出引腳做一解釋。

1、對芯片輸入管腳,若在系統板上懸空(未與任何輸出腳或驅動相接)是比較危險

2023-05-18 17:30:56

外界的電磁干擾。7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。8、在數字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。四、上拉電阻阻值選擇原則

2018-11-30 11:55:14

不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 上拉電阻阻值的選擇原則包括: 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2、從確保足夠的驅動電流

2019-09-06 15:19:36

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2020-08-14 06:35:49

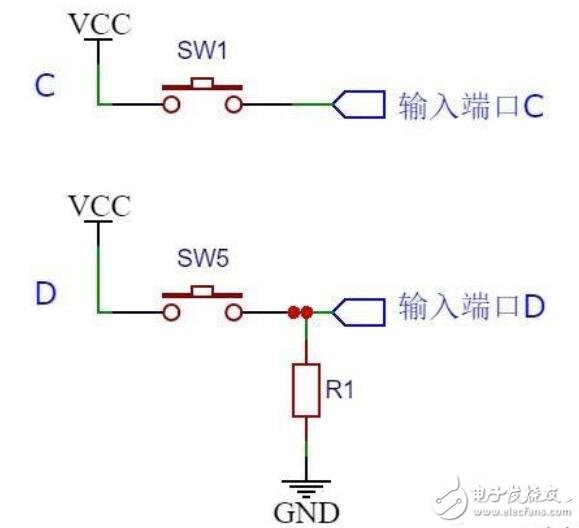

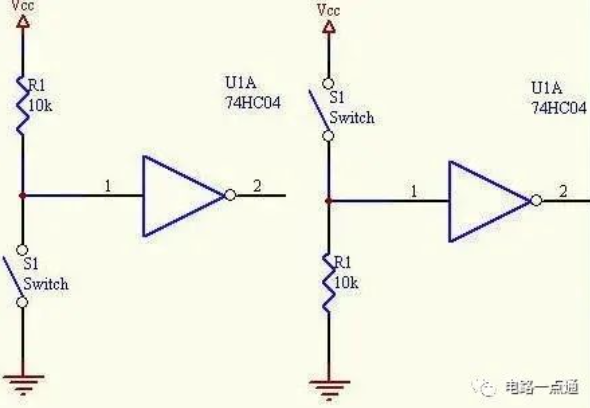

1:僅僅一根線路就可能發生短路(左),一個上拉電阻就可以防止輸入管腳懸空,同時防止不必要短路現象的發生那么我們怎樣選擇合適的電阻呢?正如大多數工程的問題一樣,答案取決于你的應用。首先我們以極端條件0

2018-11-30 09:12:02

上拉電阻和下拉電阻上下拉電阻的出發點在正常工作或單一故障狀態下,管腳均不應出現不定狀態從功耗角度考慮,在長時間的管腳等待狀態下,管腳端口的電阻不應消耗太多電流上下拉的選擇從抗擾角度出發,信號端口優選

2022-01-14 07:42:58

會產生浪涌,特別是火車上的車載電視啊等,電源上要加一些保護裝置,如RClamp0504F 等能將電壓嵌位10、一般RST,CLK 管腳接上拉電阻選擇上拉電阻阻值的原則包括:1、從節約功耗及芯片的灌電流

2014-08-21 09:56:08

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻

2011-06-02 16:03:48

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能

2012-06-10 21:25:15

引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。 另外,上拉電阻阻值的選擇原則包括:1.從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2.從確保足夠的驅動電流考慮應當足夠

2017-05-22 18:49:54

門就具備了輸出高、低電平的功能,而且電平被固定的鉗位在VCC或者GND。

上拉電阻阻值選擇原則:

1、從節約功耗及芯片的灌電流能力考慮應當足夠大:電阻大,電流小。

2、從確保足夠的驅動電流考慮應當足夠

2024-08-22 13:59:35

電路設計的上拉/下拉電阻阻值應該怎樣選?隨便弄一個,如4.k、10k的成嗎?

2023-10-28 07:37:23

我發現一個很奇怪的現象,每當我用萬用表的其中一個表筆去觸碰復位管腳10K的上拉電阻,觸碰端在5V的電源端那邊,單片機就復位。而靠近管腳端卻不會。不知這種現象正不正常。

2024-05-08 06:47:57

請問ADS1278的配置管腳的上拉下拉電阻阻值選擇多少?

上拉到 3.3v

下拉到 gnd

對了 數字地和模擬地可以公用么?

謝謝~

2025-01-23 08:29:43

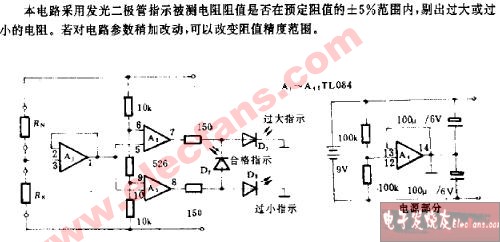

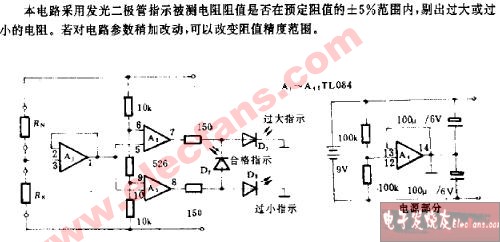

電阻阻值選擇電路

2009-02-06 11:53:40 908

908

上拉電阻在什么情況下使用:

2、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅動能力,有的單片機管腳上

2009-05-24 11:27:15 4812

4812 什么是上拉電阻,什么是下拉電阻?它們的作用是什么?

上拉電阻一般是一端接電源,一端接芯片管腳的電路中的電阻,下拉電阻一般是指一端接芯片管

2009-06-28 10:13:44 112840

112840

上拉電阻和下拉電阻的選型和計算,根據不同情況選擇不同上下拉電阻的方法

2015-11-30 18:20:28 0

0 上拉電阻在電路中的主要作用就是對電流起到限流作用,在一些設計當中經常會用到上拉與下拉電阻,但電源的設計者們往往對這兩種電阻了解的不多,正因如此,在電路出現因為上拉與下拉電阻而導致的問題時,設計者們卻會找不到相應的解決方法。

2016-05-30 13:46:53 3337

3337 上拉電阻和下拉電阻的作用及選擇

2016-12-15 18:39:07 27

27 介紹上拉電阻

2017-02-28 22:08:55 2

2 上拉電阻的作用

2017-03-04 17:53:55 9

9 上拉電阻很大,提供的驅動電流很小,叫弱上拉;反之叫強上拉。為什么要使用拉電阻:上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用,下拉同理。。上拉是對器件注入電流,下拉是輸出電流,弱強只是上拉電阻的阻值不同

2017-10-25 11:17:14 49923

49923

基于Xilinx芯片的FPGA集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM 資源。在FPGA的電路設計中,上電配置電路至關重要。其中,DONE信號上拉電阻阻值的選擇很

2017-11-15 14:41:01 9169

9169

手機原理設計中,上拉電阻常用在中斷,GPIO控制,I2C等信號上,本文希望能通過實例分析加深對上拉電阻的理解。

2017-12-21 17:03:44 5968

5968

上拉電阻的作用及阻值的選擇原則

2018-03-21 11:17:55 2

2 對于驅動TTL集成電路,上拉電阻的阻值要用1~10K之間的,有時候電阻太大的話是拉不起來的,因此用的阻值較小。但是對于CMOS集成電路,上拉電阻的阻值就可以用的很大,一般不小于20K,通常用100K

2018-05-26 09:16:09 25913

25913

管腳的電路中的電阻,下拉電阻一般是指一端接芯片管腳一端接地的電阻。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。

2018-08-30 18:33:16 132794

132794 本文首先介紹了上拉電阻阻值的選擇原則,其次介紹了上拉電阻阻值計算原則。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2018-08-30 18:37:13 21821

21821 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻

2018-10-28 09:32:49 23758

23758

當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

2019-05-09 08:00:00 3

3 在數字電路的應用中,時常會聽到上拉電阻、下拉電阻,上拉電阻、下拉電阻起著穩定電路工作狀態的作用。

2019-08-07 14:30:02 11412

11412

接電源正極的拉電阻稱之為上拉電阻,接電源負極的拉電阻稱之為下拉電阻;在數字電路的世界中只能識別“0”和“1”,加入上拉電阻,可以把未知狀態的電路控制為高電平“1”;加入下拉電阻,可以把未知狀態的電路控制為低電平“0”,可以有效的防止意外發生。

2019-09-07 10:01:44 21234

21234

上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2021-01-02 17:01:00 7334

7334

上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2021-02-20 14:20:15 10694

10694

一定的電壓信號。 ?? 上拉電阻原理 ???????? 在上拉電阻所連接的導線上,如果外部組件未啟用,上拉電阻將“微弱地”將輸入電壓信號“拉高”。當外部組件未連接時,對輸入端來說,外部“看上去”就是高阻抗的。這時,通過上拉電阻可以將輸入端

2021-12-01 14:52:22 3011

3011

經常看到芯片設計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-07 13:51:03 27

27 1、介紹使用微控制器(MCUs) 或任何數字邏輯設備時,上拉電阻器非常常見。本教程將解釋何時何地使用上拉電阻器,然后我們將做一個簡單的計算,以顯示為什么上拉很重要。2、上拉電阻是什么?假...

2021-12-05 18:36:04 17

17 電阻,以提高輸出高電平的值。2、OC門電路必須使用上拉電阻,以提高輸出的高電平值。3、為增強輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在CMOS芯片上,為了防止靜電造成損壞,不用的管腳

2022-01-14 13:58:34 3

3 上拉電阻和下拉電阻的區別及案列分析上拉電阻在一個信號未過來之前、默認(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 14:02:34 26

26 上拉電阻和下拉電阻的選型和計算上下拉電阻的出發點在正常工作或單一故障狀態下,管腳均不應出現不定狀態從功耗角度考慮,在長時間的管腳等待狀態下,管腳端口的電阻不應消耗太多電流上下拉的選擇從抗擾角度出發

2022-01-14 14:06:35 34

34 前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉

2022-01-14 14:07:36 22

22 一些單片機型號內部設置上拉電阻,因此有些上拉能力夠,可以不加上拉電阻,有些不夠,主要看所使用的單片機是否使用標準的IIC接口,若使用標準IIC接口,在使能引腳時即將進入漏極開路模式,可不用外部上拉

2022-01-14 14:16:37 6

6 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2022-02-11 10:50:27 29

29 把一個信號通過一個電阻接到高電平,叫作上拉,這個電阻充當的作用就是上拉電阻。

2022-03-29 14:16:51 4

4 如果上拉阻值過小,VDD灌入端口的電流將較大,功耗會很大,導致端口輸出的低電平值增大(I2C協議規定,端口輸出低電平的最高允許值為0.4V)。

2023-02-06 10:53:18 2407

2407 下拉就是接地,上拉就相當于升壓,提高驅動能力或者穩定性。 上拉電阻是用來解決總線驅動能力不足時提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收電流(抵抗干擾)。 上拉是將電壓拉高,下拉

2023-02-23 16:20:02 3420

3420 電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經常提到也是經常用到的電阻。在每個系統的設計中都用到了大量的上拉電阻和下拉電阻。

2023-03-17 15:51:07 7443

7443

上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理

2、上拉是對器件注入電流,下拉是輸出電流

3、弱強只是上拉電阻的阻值不同,沒有什么嚴格區分

4、對于非集電極

2023-03-17 15:57:32 3948

3948

I2C總線是微電子通信控制領域中常用的一種總線標準,具備接線少,控制簡單,速率高等優點。在I2C電路中常見的上拉電阻有1k、1.5k、2.2k、4.7k、5.1k、10k等等,但是應該如何根據開發要求選擇合適的阻值呢?下圖為I2C內部結構

2023-05-10 16:17:05 9283

9283

上拉電阻器非常普遍,您會一直在數字電路中看到它。它只是一個電阻器,從輸入端連接到Vdd,電路的正電源。

2023-05-18 16:04:01 7768

7768

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2023-05-31 13:57:02 4053

4053

個電阻將其箝位至高電平(上拉)或低電平(下拉),但是無論具體用法如何,這個基本的作用都是相同的,只是在不同應用場合中會對電阻的阻值要求有所不同,下面一起來了解它們吧:

2023-06-10 14:17:53 5266

5266

上拉和下拉電阻是許多數字電路的組成部分。了解什么是上拉電阻或下拉電阻很重要?為什么將其用于數字電路?以及如何選擇這些的價值?本文將回答這三個問題,并讓您更好地了解它。

2023-06-18 15:25:17 8234

8234

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號

2023-06-29 17:04:31 14290

14290

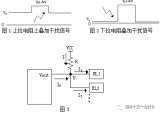

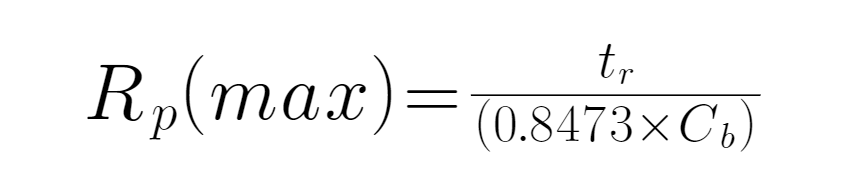

上拉電阻計算 1、上拉電阻過小,電流大,端口低電平 level 增大。 2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。 因此計算出一個精確的上拉電阻阻值是非常重要的。計算上拉電阻的阻值,有

2023-07-25 10:03:23 2809

2809

上拉電阻是一個電阻,它通常被連接到電路中的高電平值,以提供一個上拉電壓。這個電阻的作用是限制電流的流動,同時為電路提供高電平值。

2023-09-06 09:16:32 3322

3322

上拉電阻計算 1、上拉電阻過小,總線上電流增大,端口輸出低電平增大。 2、上拉電阻過大,上升沿時間增大,方波可能會變成三角波。 因此計算出一個精確的上拉電阻阻值是非常重要的。 計算上拉電阻的阻值

2023-09-28 14:29:36 4300

4300

上拉電阻主要用于為信號線或GPIO引腳提供默認狀態。通常選擇幾K或幾十K阻值的電阻。阻值較大的電阻確保不會通過電阻不斷地將過多的電流引入到信號線上(5V Vdd / 10KΩ = 0.5mA 電流)。在常見的MCU中有大約幾十K的電阻可以通過代碼啟用的上拉電阻將 GPIO 引腳預設為邏輯高電平狀態。

2023-10-12 09:19:38 9369

9369

本篇說明了在內置上拉電阻、下拉電阻的IC中,如果沒有規定上拉電阻、下拉電阻的電阻值時的計算方法。

2023-10-18 09:27:45 4957

4957 這次簡單說說上拉電阻,那問題來了,什么是上拉電阻?上拉電阻從概念上理解就是一個電阻一端接到電源正極,一端接到輸出端。

2023-11-13 15:33:06 4781

4781

上拉電阻和下拉電阻的用處和區別? 上拉電阻和下拉電阻是電子電路中常用的兩種電阻配置方式,它們在電路中起到了關鍵的作用。下面將詳細介紹它們的用途和區別。 首先我們來介紹上拉電阻。上拉電阻是指將一個電路

2023-11-22 18:26:09 3115

3115 ,是電阻的重要參數之一。 電阻的阻值通常用歐姆(Ω)來表示,它標示了電阻器對電流的抵抗能力。電阻值越大,表示電阻器對電流的阻礙能力越強,反之亦然。因此,通過電阻上的數字,我們可以很方便地識別出電阻的阻值,從而選擇

2023-12-07 13:53:59 8318

8318 從器件輸出端流出電流。所謂的強上拉和弱上拉指的是上拉電阻的不同阻值選擇,而不是有嚴格界限的概念。對于非集電極(或漏極)開路輸出型的電路,例如普通的門電路,它們提供電流和電壓的能力是有限的。上拉電阻的主要功能

2024-05-02 14:51:00 5542

5542

上拉電阻有助于降低系統的總功耗,同時保持電路的功能性和穩定性。那么上拉電阻如何實現低功耗設計呢? 以下是上拉電阻實現低功耗設計的幾種方法: 選擇合適的上拉電阻值: 功耗與電阻值成反比關系,一個較大

2024-05-02 15:00:00 2181

2181 在選擇貼片電阻的阻值時,需要考慮多個因素以確保電阻器能夠滿足電路的設計需求和工作條件。以下是一些關鍵的選擇步驟和注意事項: ? 1. 明確電路設計需求 所需阻值:首先,需要明確電路設計中所需的電阻值

2024-08-30 14:59:18 1113

1113 在電子電路設計中,上拉電阻是一種常用的元件,它的阻值選擇至關重要,需要綜合考慮多個因素來確定合適的阻值。 一、功耗因素 功耗是選擇上拉電阻阻值時需要考慮的一個重要方面。當電阻兩端有電壓時,就會產生

2025-02-05 17:25:00 1424

1424 上拉電阻、下拉電阻在電子元器件間中,并不存在上拉電阻和下拉電阻這兩種實體的電阻,之所以這樣稱呼,原因是根據電阻不同使用的場景來定義的,其本質還是電阻。上拉電阻的定義:在某信號線上,通過電阻與一個固定

2025-05-22 11:45:23 1821

1821

電子發燒友App

電子發燒友App

評論