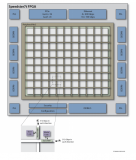

針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 14294

14294

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 7150

7150

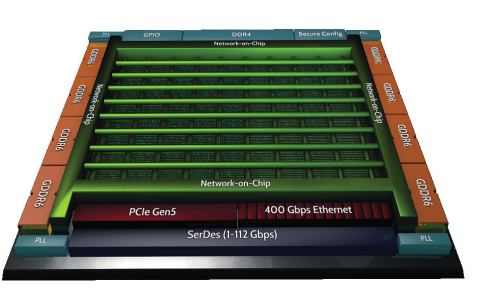

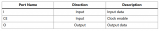

Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-02-27 17:08:41 2288

2288 在多時鐘設計中可能需要進行時鐘的切換。由于時鐘之間可能存在相位、頻率等差異,直接切換時鐘可能導致產生glitch。

2020-09-24 11:20:38 6410

6410

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期 T,則

2020-11-23 13:08:24 4644

4644

EFX_GBUFCE既可以讓GPIO走全局時鐘網絡也可以用于為時鐘添加使能控制,當并不是隨時需要該時鐘時可以把時鐘禁止以節省功耗。

2023-05-12 09:53:38 1407

1407

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。

2023-12-22 09:04:46 2675

2675

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

與HBM DRAM堆疊裸片之間對高帶寬連接的需求。本文將深入探討UCIe支持的不同接口,以實現片上網絡(NoC)互連。

2025-08-04 15:17:24 2452

2452 2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了超高帶寬。

2021-11-11 14:20:14 3561

3561

FPGA 時鐘分配網絡設計技術

2012-08-20 17:15:27

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA多時鐘設計

2017-10-21 20:28:45

大型設計中FPGA 的多時鐘設計策略Tim Behne 軟件與信號處理部經理 Microwave Networks 公司Email: timothyb@microwavenetworks.com利用

2012-10-26 17:26:43

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線?

2019-08-30 08:31:41

FPGA的多時鐘系統設計 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

,拜托大家了!

FPGA系統設計中,如果用兩個FPGA工作,應該如何設計兩片之間的通信?從片的配置和時鐘輸入與主片有何不同

2023-04-23 11:31:45

FPGA系統設計中,如果用兩個FPGA工作,應該如何設計兩片之間的通信?從片的配置和時鐘輸入與主片有何不同?一個做主片用于數據處理和控制,一個做從片用于IO擴展。硬件和軟件上應該如何設計兩片之間

2023-05-08 17:18:25

采用FPGA來設計一款廣泛應用于計算機、Modem、數據終端以及許多其他數字設備之間的數據傳輸的專用異步并行通信接口芯片,實現了某一時鐘域(如66 MHz)的8位并行數據到另一低時鐘域(如40 MHz)16

2011-09-07 09:16:40

片上網絡的研究才剛剛起步,還沒有在商業產品中廣泛應用。片上網絡的標準化可以增加組件的互連性,但會造成性能的損失,而對特定的片上系統,性能是片上系統的一個關鍵因素。

2019-09-19 09:10:34

網絡基礎集(解決上網常見問題)

2009-06-11 15:37:25

利用 FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘 FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系

2012-03-05 14:42:09

跨越時鐘域FPGA設計中可以使用多個時鐘。每個時鐘形成一個FPGA內部時鐘域“,如果需要在另一個時鐘域的時鐘域產生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標志第3部分:穿越

2012-03-19 15:16:20

求關于片上網絡各個ip核之間的熱阻和功耗對io核溫度的影響,最好具體到公式表達

2017-04-30 00:16:32

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

【作者】:李曉輝;曹陽;王力緯;陳晨;【來源】:《華中科技大學學報(自然科學版)》2010年03期【摘要】:針對虛通道技術導致片上網絡(NoC)面積增加的問題,提出了一種基于遺傳算法的NoC虛通道

2010-04-22 11:34:25

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設計中FPGA的多時鐘設計策略 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重

2012-05-23 19:59:34

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中

2015-05-22 17:19:26

NoC為FPGA設計提供了哪些優勢?NoC在FPGA內部邏輯互連中發揮的作用是什么?如何利用片上高速網絡創新地實現FPGA內部超高帶寬邏輯互連?

2021-06-17 11:35:28

對多時鐘系統的同步問題進行了討論?提出了亞穩態的概念及其產生機理和危害;敘述了控制信號和數據通路在多時鐘域之間的傳遞?討論了控制信號的輸出次序對同步技術的不同要求,重點論述了常用的數據通路同步技術----用FIFO實現同步的原理及其實現思路

2012-05-23 19:54:32

AD怎么讓走線帶上網絡呢?

2019-09-11 05:36:36

采用片上網絡(NoC)的新型FPGA數據架構賦能5G網絡和數據中心智能網卡(SmartNIC)設計方案

2021-02-22 08:01:25

大型設計中FPGA的多時鐘設計策略利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘

2020-04-26 07:00:00

1、高級FPGA設計技巧 有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口

2022-10-14 15:43:00

與FPGA中的普通路由相比,使用片上網絡來互連DSP48A會降低性能嗎?以上來自于谷歌翻譯以下為原文Will the use of network on chip to interconnect

2019-06-28 09:39:03

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2023-06-02 14:26:23

Multiple Clock System Design PLD設計技巧—多時鐘系統設計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 網絡基礎集+解決上網常見問題:

2009-06-11 15:15:47 25

25 一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 半導體技術的飛速發展推動了片上系統設計進入到片上網絡階段。為了進一步研究其結構及不同工藝對其的影響,文章分析了片上網絡對于片上系統的優越性,并針對其重要組成

2009-08-21 09:03:08 12

12 該文建立了一種面向應用設計的片上網絡的性能分析模型,并在此基礎上提出了片上緩存優化策略和分配算法。在硬件實現平臺上的仿真表明,該文建立的片上網絡分析模型能很好

2009-11-18 15:20:06 9

9 隨著芯片上晶體管數量發展到10億數量級,功耗逐漸成為芯片設計的首要制約因素。本文分別從CMOS電路和網絡通訊兩個層面上來分析片上網絡(NoC)的功耗,并給出了相應的功耗

2009-12-14 09:51:17 6

6 本文參照傳統的OSI(Open Systems Interconnection)模型與TCP/IP 模型對片上網絡系統模型層次結構進行了按照片上網絡特點進行的劃分。文中還對片上網絡的網絡層設計中的各種拓撲結

2009-12-14 09:54:49 8

8 半導體技術的快速發展以及芯片上系統應用復雜度的不斷增長,使得片上互連結構的吞吐量、功耗、延遲以及時鐘同步等問題更加復雜,出現了將通信機制與計算資源分離的片上網絡。

2010-02-24 11:55:49 17

17 半導體技術的飛速發展推動了片上系統設計進入到片上網絡階段。為了進一步研究其結構及不同工藝對其的影響,文章分析了片上網絡對于片上系統的優越性,并針對其重要組成部

2010-07-17 16:53:50 19

19 半導體技術的快速發展以及芯片上系統應用復雜度的不斷增長,使得片上互連結構的吞吐量、功耗、延遲以及時鐘同步等問題更加復雜,出現了將通信機制與計算資源分離的片上網絡。

2010-07-17 16:56:32 33

33 針對片上網絡的死鎖問題,提出一種片上網絡自適應路由算法——虛擬網絡(VN)路由算法,該算法根據報文源地址和目的地址將網絡分成4個虛擬網絡。一旦報文在某個給定的虛擬

2010-07-21 16:09:40 13

13 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

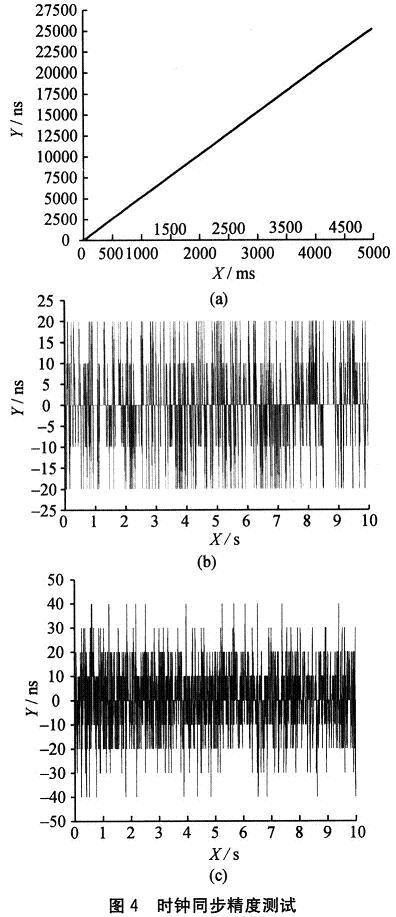

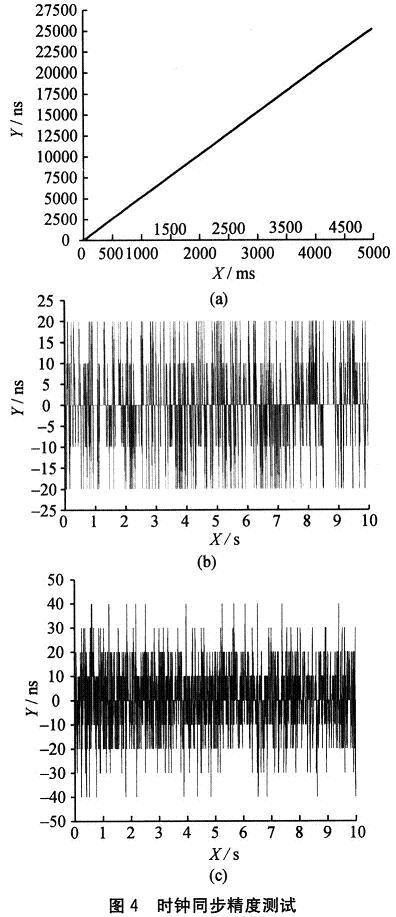

FPGA的時鐘頻率同步設計

網絡化運動控制是未來運動控制的發展趨勢,隨著高速加工技術的發展,對網絡節點間的時間同步精度提出了更高的要求。如造紙機械,運行速

2010-01-04 09:54:32 3161

3161

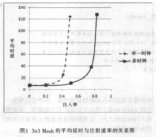

1 多時鐘片上網絡架構的分析

片上網絡結構包含了拓撲結構、流量控制、路由、緩沖以及仲裁。選擇合適網絡架構方面的元素,將對片上網絡的性能產生重大影響[2]

2010-09-02 09:43:47 1061

1061

為提高芯片驗證與測試的可靠性,針對片上網絡核心芯片的結構特點,設計出一種基于宿主機/目標機通信模式的測試系統。重點描述了測試系統軟硬件的設計與實現,并采用Stratix系列FPGA芯片進行原型測試和驗證。實驗結果表明,該系統可對芯片的復位、實現功能及

2011-01-15 15:46:29 31

31 本文將探討FPGA時鐘分配控制方面的挑戰,協助開發團隊改變他們的設計方法,并針對正在考慮如何通過縮小其時鐘分配網絡的規模來擁有更多的FPGA I/O,或提高時鐘網絡性能的設計者們

2011-03-30 17:16:32 1241

1241

本內容介紹了分級環片上網絡互連

2011-05-19 15:37:33 21

21 從建立功耗模型出發, 在集成電路不同的設計層次、片上網絡通訊功耗以及NoC 映射問題等方面來討論NoC 的低功耗設計, 綜合了現有功耗解決的最新方案, 對NoC 的功耗研究做了一個比

2011-06-30 09:32:17 1471

1471 在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 4131

4131

世界頭號片上通信IP供應商Sonics公司(R)今天面向高級并發應用處理和系統級設計推出了業內首款GHz級片上網絡(NOC)SonicsGN(TM)(SGN)。

2011-09-22 18:09:17 2000

2000 基于AD9540產生多時鐘輸出

2011-11-25 00:02:00 31

31 麻省理工學院(MIT)的研究人員指出,今天我們都在使用片上總線和環狀拓樸,但它們所帶來的麻煩可能要比它們能貢獻的價值還要多,這也推動了片上網狀網絡(on-chip mesh networ

2012-04-18 08:39:53 605

605 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1591

1591

通過分析流水線結構和單周期結構的片上網絡路由器,提出了一種低延時片上網絡路由器的設計,并在SMIC 0.13um Mixed-signal/RF 1.2V/3.3V工藝進行流片驗證。芯片測試結果表明,該路由器可以

2013-06-25 16:25:01 40

40 為了實現軟硬件協同設計和提高仿真速度的需求,采用SystemC語言的建模方法,通過對片上網絡體系結構的研究,提出了一種片上網絡的建模方案,并對一個mesh結構完成了SystemC的建模設

2013-07-30 11:46:44 42

42 FPGA學習資料,有興趣的同學可以下載看看。

2016-04-07 16:33:47 0

0 多核密碼處理器中的片上網絡互連結構研究_杜怡然

2017-01-03 18:00:37 0

0 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 當Xilinx 7Series FPGA中,存在3種主要的時鐘網絡:BUFG,BUFR,BUFIO以及他們所衍生出的各種變種。那么他們有什么主要特點和區別呢? BUFIO是IO時鐘網絡,顧名思義,它

2017-02-08 05:31:40 3409

3409

片上網絡Network-on-chip (NoC) 是一種應用于大規模集成電路(VLSI)系統中的,一種新的片上系統(System-on-chip)的設計方法。

2017-02-11 06:39:13 1952

1952

在一個SOC設計中,存在多個、獨立的時鐘,這已經是一件很平常的事情了。大多數的SOC器件都具有很多個接口,各個接口標準都可能會使用完全不同的時鐘頻率。

2017-02-11 15:07:11 1522

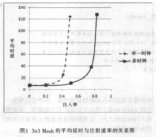

1522 網絡拓撲:在設計中,選擇Mesh拓撲結構。Mesh結構擁有最小的面積開銷以及低功耗的特點。此外,Mesh的線性區的節點數量規模大以及通道較寬。同時,Mesh也能很好地映射到FPGA下的底層路由結構,降低了FPGA 邏輯擁塞和路由器的功耗。

2018-07-22 09:44:00 2593

2593

很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統能夠包括上述四種時鐘類型的任意組合。

2017-11-25 09:16:01 5020

5020

上的設備在通信時對總線的獨占性以及單一系統總線對同步時鐘的要求,使得在片上IP核越來越多的芯片中,不可避免地存在通信效率低下、全局同步時鐘開銷大等問題。 片上網絡NoC(Network on Chip)的提出有效地解決了上述問題。該系統借鑒了計算機網絡中分組交換的通

2017-11-30 07:57:21 718

718

針對將計算任務合理地映射到三維片上網絡( NoC)的問題,提出了一種基于遺傳算法(GA)的改進算法。GA具有快速隨機的搜索能力,Prim算法可在加權連通圖內得到最小生成樹,改進算法結合了兩種算法

2017-12-07 14:40:49 0

0 根據計算趨近數據的原則,提出面向MPI集合操作的定制化片上網絡設計方法,通過增強現有片上路由器的硬件功能實現MPI集合操作在網絡層的加速。設計MPI歸約操作,將其擴展至多種集合操作,并與一種針對

2018-02-02 15:46:50 0

0 在CPU-GPU異構系統架構中,由于GPU程序的多線程特點,大多數GPU程序會壟斷系統中的共享資源,例如片上網絡。這將給CPU程序的性能造成很大的損失。我們發現有一些GPU程序性能對網絡延遲表現

2018-04-26 16:33:13 1

1 跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘域的數量急劇增加。通常不止數百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 3895

3895 移動網絡上網與WiFi連接上網,是移動設備上的兩大高手。一個主室外, 一個主室內。WiFi上網是移動網絡的室內覆蓋補充。WiFi遲早將被淘汰的言論層出不窮。下面我們從耗電、速度、經濟、安全等方面來說說。

2020-03-21 15:06:04 16654

16654 有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。

2020-09-24 10:20:00 3603

3603

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

3695 利用 FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線,本文將對這些設計策略深入闡述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540產生多時鐘輸出

2021-03-18 23:03:12 2

2 引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。這些網絡被設計成具有低偏移和低占空比失真、低功耗和改進的抖動容限。它們也被設計成

2021-03-22 10:09:58 14973

14973

半導體制造工藝的快速發展使得片上可以集成更大規模的硬件資源,片上網絡的研究試圖解決芯片中全局通信問題,

2021-03-24 16:49:15 3700

3700 半導體制造工藝的快速發展使得片上可以集成更大規模的硬件資源,片上網絡的研究試圖解決芯片中全局通信問題,

2021-03-24 16:41:57 4779

4779 有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2021-05-10 16:51:39 4652

4652

三維片上網絡是解決片上網絡通訊瓶頸的重要途徑,拓撲結構是三維片上網絡研究中的關鍵問題。針對高維超立方拓撲結構節點度迅速増加,岀現通訊瓶頸的問題,提岀一種髙維超立方裂變拓撲結構,該拓撲在同等網絡規模下

2021-05-11 17:00:54 9

9 三維混合無線片上網絡架構及路由算法

2021-06-03 14:28:36 7

7 有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2021-09-23 16:39:54 3632

3632 1. 概述 Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。2D NoC如同在FPGA

2021-11-12 09:21:22 2972

2972

?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 1249

1249

假如給定FPGA內的時鐘沒有正確運行,那么我們多片FPGA系統的整體將不能同時啟動,這將有可能是致命的。

2023-05-22 09:21:24 621

621

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2023-08-23 16:10:01 1372

1372 FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

電子發燒友App

電子發燒友App

評論