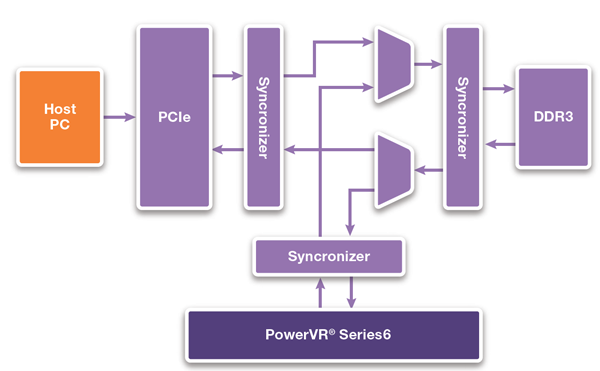

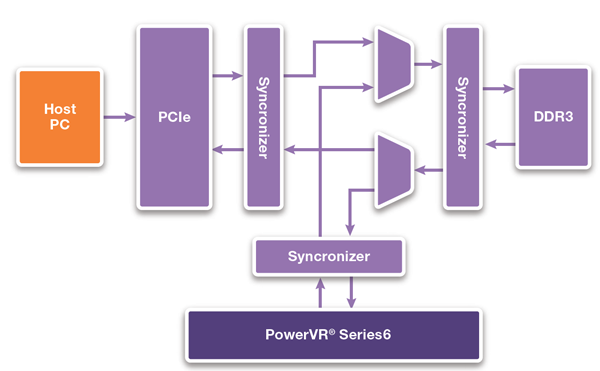

Synopsys所做的第一步是啟動一個概念驗證項目。這個項目為Imagination的PowerVR Series6 GPU展示了基于FPGA的原型設計。

2015-06-24 09:47:00 2022

2022

什么是FPGA原型?? FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能

2022-07-19 16:27:29 2400

2400 FPGA原型在數字芯片設計中非常重要,因為相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發者來進行底層軟件的開發。這一流片前的軟硬件的協同開發,是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

多片FPGA之間的互連,經常提到多路復用的概念,也經常提到TDM的概念,正確理解多路復用在多片FPGA原型驗證系統中的機理,尤其是時序機制,對于我們正確看待和理解多片FPGA原型系統的性能有很好的促進作用。下圖是一個使用多路復用器后接采樣FF的多路復用解決方案的示例。

2023-06-06 10:04:35 2286

2286

16片ADS54J54多片如何同步,才能保證每個通道采集同一個目標的數據一一對應

2025-01-10 16:27:50

Tape Out并回片后都可以進行驅動和應用的開發。目前ASIC的設計變得越來越大,越來越復雜,單片FPGA已不能滿足原型驗證要求,多片FPGA驗證應運而生。本文我就將與大家探討FPGA原型驗證的幾個經典挑戰性場景,(具體應對的辦法,請戳原文。)容量限制和性能要求

2020-08-21 05:00:12

OpenFlow。研究人員可以在全國范圍內在國家級測試平臺上,比如美國的GENI和歐盟的FIRE上試驗新型網絡架構。 研究人員還越來越多地將NetFPGA開發板用于新理念的硬件原型設計,諸如新的轉發模式、調度

2011-07-19 15:51:05

上面介紹的是整個 FPGA 固件系統的實現方法,為了驗證設計的正確性,還需要編寫一個測試平臺對整個系統進行仿真。由于實際情況下 FPGA 是和 PDIUSBD12 進行通信,所以在測試平臺中需要虛擬

2018-11-28 15:22:56

各位專家好:

??????? 關于多片C6678的同步調試問題想咨詢下:

?????? 我打算做兩個板子,每個板子上集成兩片C6678的芯片,板間通信打算用光傳輸,現在想咨詢的問題是在用CCS進行調試的時候,這個能不能實現同步調試,比如在某個時間一起停下來,去看看各自寄存器或者變量的值。謝謝。

2018-06-21 02:37:42

Hi,ADI我們現在在做一個5.8GHz的多通道接收機系統,需要多片AD9361之間載波相位同步我在AD9361的userguide UG570 page19,發現ad9361的external LO只能支持70MHz至4GHz?我的理解是否正確如果我希望使用5.8GHz的本振同步,有方法實現嗎?

2018-10-08 10:51:27

多片AD9680如何同步?需要注意什么問題?

2023-12-08 08:02:57

用FPGA控制兩片AD9739(以下簡稱A和B),其中A的SYNC_OUT接到了B的SYNC_IN,而A的SYNC_IN和B的SYNC_OUT接到了FPGA中。

現在配置0x10寄存器,采用無同步

2023-11-27 14:45:26

用4片AD9910,各種模式輸出單片的調試都沒有問題。現在要調多片同步,按照數據手冊上的要求進行各個寄存器的配置,25M參考時鐘輸入,內部用鎖相環陪頻到1G,就是多片同步不了,12腳一直為高,檢測

2018-11-20 09:11:33

用4片AD9910,各種模式輸出單片的調試都沒有問題。

現在要調多片同步,按照數據手冊上的要求進行各個寄存器的配置,25M參考時鐘輸入,內部用鎖相環陪頻到1G,就是多片同步不了,12腳一直為高,檢測不到有效地SYNC_IN信號,不知道原因,請技術支持幫助

2023-11-27 06:00:09

多片AFE5818的輸入ADC時鐘為同步時鐘,不同的芯片上LVDS串行數據時鐘(DCLKP、DCLKM)和幀時鐘(FCLKP、FCLKM)是否是同步的

2024-11-18 07:29:50

筆者在多通道無源雷達信號處理機的設計中,采用了DSP芯片TMS320VC5409控制4片DDC芯片HSP50214B的接口電路,研究了同步控制多片HSP50214B等關鍵技術。DDC芯片

2019-06-04 05:00:17

官方應用筆記an605介紹了如何同步多片DDS9854, 上圖是在倍頻至300M時的需滿足的時序圖,要求EXT I/O UPDATE CLK的上升沿發生在REFCLK上升沿的前0.3ns和后

2018-09-29 15:36:31

實現通用的原型開發環境。功能包括:開發平臺展示了跨轉換器IC和跨板的多通道同步。在客戶面前先在評估板環境中驗證多通道性能,而不是僅僅為了同時測試多個通道而致力于生產設計。一定程度的集成和功能性,可以

2020-08-21 14:24:29

我有一個應用打算使用4片ADC3853進行4通道的信號同步采集,采樣率為64Msps,我希望這4片ADC3583能在同一時刻采集信號(即采樣同步),然后將采集到的原始數據(即不抽取)送給FPGA

2024-11-18 06:17:07

ADS131如何實現多片同步采集呢

2024-11-26 06:14:23

十、Kubernetes平臺中日志收集

2019-11-04 09:19:30

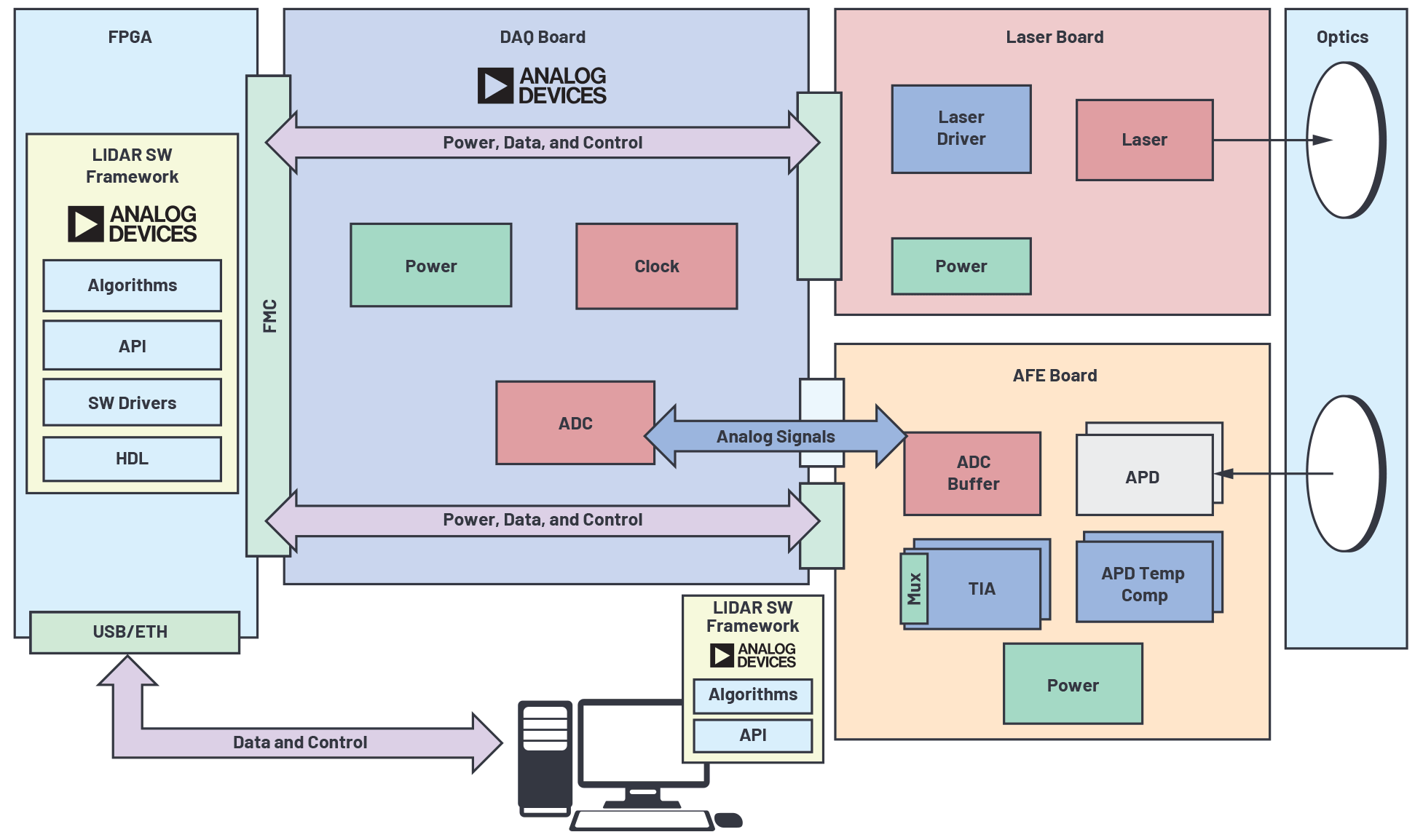

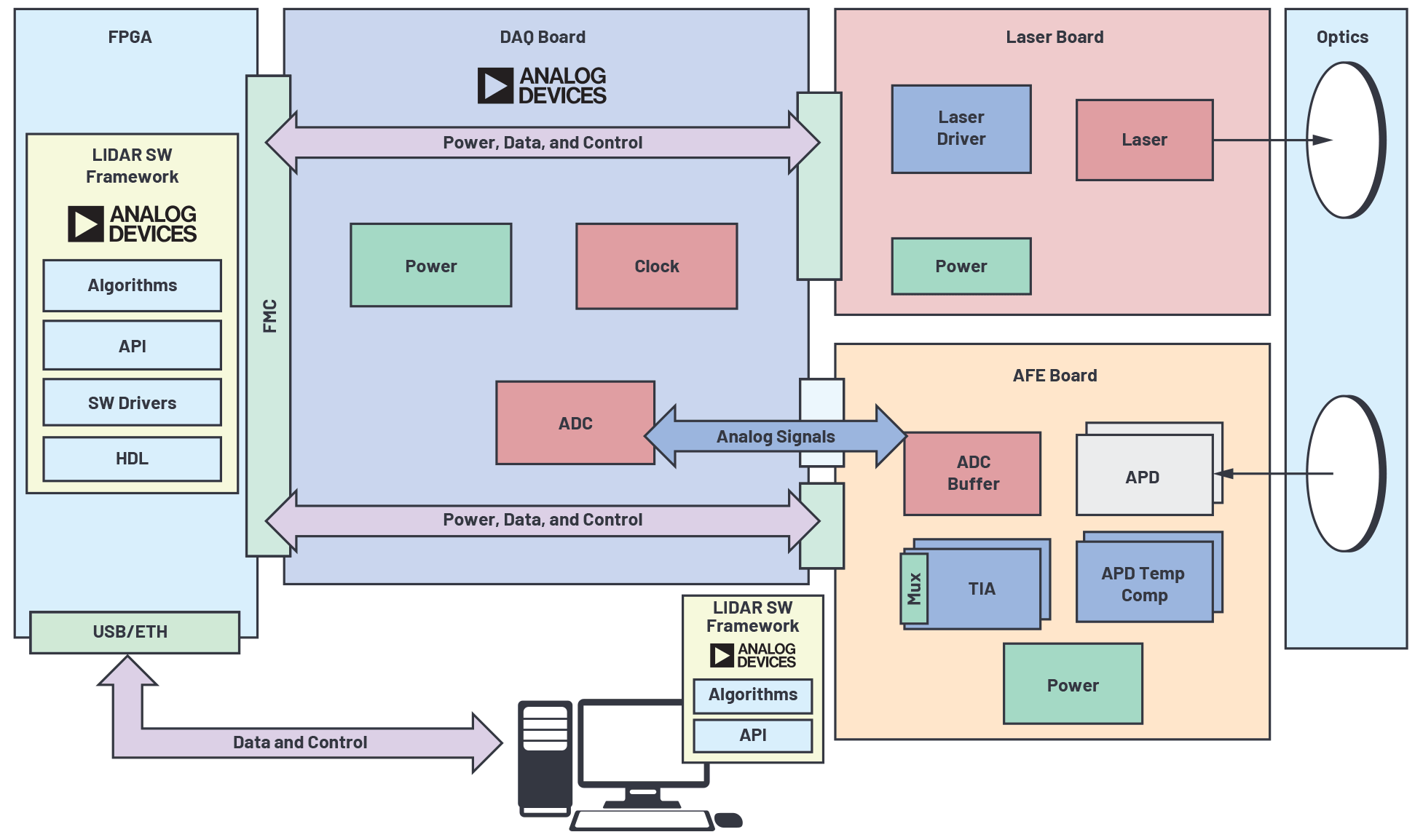

本文探討ADI公司新推出且擁有廣泛市場的LIDAR原型制作平臺,以及它如何通過提供完整的硬件和軟件解決方案,使得用戶能夠建立其算法和自定義硬件解決方案的原型,從而幫助客戶縮短產品開發時間;詳細介紹

2021-06-17 09:08:54

Thingy:91 X 為開發人員提供了一個經過全球認證的、多傳感器、電池供電的蜂窩物聯網原型平臺

全球領先的低功耗無線連接解決方案提供商Nordic Semiconductor推出了其最新的物聯網

2025-12-15 10:39:32

分割到24顆FPGA內。 此外, 實時運行功能還可以通過網絡對多塊基于FPGA的原型平臺進行控制和監測。我非常高興我們可以向客戶提供這種新的能力。”

2019-07-02 06:23:44

斯坦福大學與賽靈思研究實驗室(Xilinx Research Labs)聯手開發專門面向研究社群的第二代高速網絡設計平臺 NetFPGA-10G。該新型平臺采用最先進的技術,能夠幫助研究人員迅速構建

2019-08-27 08:30:57

和使用SYSREF(AC-coupled)來進行同步,但兩種方法都沒能完成兩片ADC之間的同步。

同一片ADC上2個通道的NCO是同步的。

在我的FPGA里面,我將給SYNC信號進行了與操作之后再分發到了兩片ADC

2024-11-28 07:01:29

如果系統中使用多片功放芯片,如何實現時鐘同步(例如TAS5622A)?

ST的芯片(如TDA7498)可以支持: Master芯片提供時鐘給Slave芯片,從而實現多芯片同步。

2024-10-21 08:06:54

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。

2021-05-06 07:20:48

的設計和驗證的復雜性需求。隨著原型技術在設計分割以及多 FPGA 聯 合調試領域的進步,基于FPGA 的原型系統不僅可以滿足百萬門級的設計需求,還可以實現設計規模高達15 億門。基 于FPGA

2018-08-07 09:41:23

多片fpga組成jtag鏈的時候如何加載?

2023-08-11 09:10:26

求大神詳細介紹一下基于FPGA的電子穩像平臺的研究

2021-05-07 06:02:47

直線電機在平臺中有哪些應用?

2021-10-29 06:39:19

評估新類別的元件。SDP連接至FPGA評估與原型制作平臺,可以輕松創建并演示采用ADI元件通信的定制FPGA嵌入式設計。用戶可以迅速建立定制評估與原型制作系統,還可以重復使用各種平臺元件,演示各種豐富

2018-10-24 10:24:31

500MSPS的采樣,但是沒有提到任何多片同步的機制?有沒有具體的實現多片ADCs(8路數據,最少4片)的同步實現操作?

2019-01-11 08:06:29

請教一下論壇里的諸位大牛; 我需要用多片AD9361接收5.8GHz的射頻信號,如何保證多片AD9361的相位同步?因為AD9361的external LO只能支持70MHz至4GHz,不能滿足

2019-02-15 14:55:35

如何將多片AD9361芯片進行相位同步,技術文檔有說通過sync管腳進行MCS同步,但是僅僅只針對數據時鐘完成同步。個人理解數據相位主要由RF混頻處理以及后續數字處理決定,通過sync管教能夠完成

2018-12-25 11:42:25

如何實現多片AD9361接收同步?每次上電周期的相位補償是否可以通過軟件自動補償?

2019-02-18 07:58:53

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。

2019-06-18 07:43:00

。基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經成為ASIC芯片設計中重要的驗證方法。本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結果。1、RFID芯片的FPGA

2019-05-29 08:03:31

設計一種基于FPGA的多通道同步數據采集存儲系統,分為多通道同步數據采集模塊和數據存儲模塊。系統設計采用多通道數據的同步實時采集以及壞塊檢測技術。多通道同步數據采集

2010-12-27 15:31:33 70

70 《 FPGA的原型開發方法手冊》(FPMM),這是一本介紹如何使用 FPGA 作為平臺進行片上系統(SoC)開發的實用指南。FPMM 收錄了眾多公司的設計團隊在設計和驗證方面的寶貴經驗,

2011-03-14 09:06:50 1099

1099 介紹了一種基于SRAM技術的FPGA可編程邏輯器件的編程方法,能在系統復位或上電時自動對器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問題,針對當前系統規模的日益增大,本文提出了一種用單片機對多片FPGA自動加載配置的解決方案.

2011-03-15 16:41:22 21

21 基于模糊PID多軸同步控制技術研究-2010。

2016-04-05 16:26:42 9

9 基于模糊PID控制的多電機同步控制研究-2009。

2016-04-05 16:36:48 22

22 自升式海洋平臺多樁腿同步控制的研究_齊繼陽

2017-01-16 14:04:30 0

0 如今,設計人員使用兩種相對獨立的方法進行 SoC 原型驗證:以事務級模型為基礎的虛擬原型驗證和基于 FPGA 的原型驗證。 虛擬原型驗證執行快速的 TLM,并可提供更高效的調試和分析方案,非常適合

2017-02-08 14:32:11 572

572 完整原型設計平臺便是當之無愧的大方案,該平臺由現有的一些設備組成: Prodigy邏輯模塊:基于FPGA的原型開發板。如,基于XilinxVirtex-72000T 3D FPGAs的TAI 邏輯模塊

2017-02-09 03:49:04 917

917 效率。Protium S1與Cadence? Palladium? Z1企業級仿真平臺前端一致,初始設計啟動速度較傳統FPGA原型平臺提升80%。

2017-03-02 11:13:11 3210

3210 基于FPGA的MSK同步調諧研究_金國慶

2017-03-18 08:00:00 0

0 在校園信息化平臺中研究與實現MVC2x框架_姚煉

2017-03-20 09:24:02 1

1 為了能在GPS接收端獲取正確導航電文,研究了CJPS接收機位同步、幀同步的基本原理和實現方式。提出一種采用FPGA來實現位同步、幀同步系統的設計方案。使用Xilinx開發軟件,通過Verilog代碼

2017-11-07 17:13:39 12

12 利用Xilinx的FPGA設計了一個FPGA原型驗證平臺,用于無源高頻電子標簽芯片的功能驗證。主要描述了驗證平臺的硬件設計,解決了由分立元件實現模擬射頻前端電路時存在的問題,提出了FPGA器件選型

2017-11-18 08:42:22 4347

4347

門陣列(FPGA)做為安謀國際核心測試芯片,進而建構SoC原型制作平臺。 驗證SoC設計 FPGA原型最穩當 FPGA原型制作是在FPGA上實作SoC或特定應用集成電路(ASIC)設計的方法,并進行硬件驗證和早期軟件開發。

2018-05-11 09:07:00 3069

3069

隨著新型SoC(片上系統)設計的成本和復雜性的不斷提高,現場可編程門陣列(FPGA)原型技術正日益成為SoC新項目的重要組成部分,甚至是至關重要的組成部分。通過提供一種更快到達硬件的方法,FPGA

2019-06-25 08:00:00 2

2 Microchip啟動了PolarFire片上系統(SoC)現場可編程門陣列(FPGA)早期使用計劃(EAP)。

2019-12-16 15:16:21 1053

1053 Microchip啟動了PolarFire片上系統(SoC)現場可編程門陣列(FPGA)早期使用計劃(EAP)。

2019-12-26 15:39:03 1460

1460 FACE-VUP:大規模FPGA原型驗證平臺 FACE-VUP大規模FPGA原型驗證平臺是FACE系列的最新產品。FACE-VUP同時搭載16nm工藝的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 3371

3371 其次,部分FPGA開發板也被用在IP和小型芯片設計的開發驗證場景。這部分開發板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應開發驗證場景,一般由用戶自己負責手工實現從設計到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

3563 從系統的特性上看,FPGA 原型系統支持多FPGA、自動分割;性能較高的情況下運行系統軟件;仿真加速器的超大容量可以放全芯片的設計,進行全芯片的系統功能/性能/功耗驗證。

2022-05-25 09:35:13 10849

10849 Corundum是一個基于FPGA的開源原型平臺,用于高達100Gbps及更高的網絡接口開發。Corundum平臺包括一些用于實現實時,高線速操作的核心功能,包括:高性能數據路徑,10G/ 25G

2022-11-03 10:02:14 3126

3126 本文討論ADI公司新的廣闊市場LIDAR原型設計平臺,以及該平臺如何通過提供完整的硬件和軟件解決方案來幫助縮短客戶的產品開發時間,客戶可以使用該解決方案對其算法和定制硬件解決方案進行原型設計。它詳細介紹了模塊化硬件設計的細節,包括光接收和發射信號鏈、FPGA 接口和用于遠距離檢測的光學器件。

2022-12-20 14:49:02 3352

3352

FPGA原型驗證在數字SoC系統項目當中已經非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統顯的格外重要

2023-04-03 09:46:45 2074

2074 FPGA原型平臺的性能估計與應用過程的資源利用率以及FPGA性能參數密切相關,甚至FPGA的制程也是一個因素。

2023-04-04 09:49:04 3145

3145 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:03 1543

1543 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:37 936

936 FPGA與FPGA之間互連對信號延遲的影響,兩片FPGA的IO之間每一個額外的過渡,例如連接器、焊點甚至板內通孔,都會增加一些阻抗,從而降低信號質量,并增加信號之間串擾的概率。然而,經過仔細分析,發現這并不是一個想象中的大問題。主要矛盾是FPGA互連線的影響。

2023-04-16 10:21:51 1333

1333 FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 1953

1953 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 1331

1331

多片FPGA原型驗證系統的拓撲連接方式各不相同,理想的多片FPGA原型驗證系統應該可以靈活配置,可以使用其相應的EDA工具

2023-05-08 11:51:40 891

891

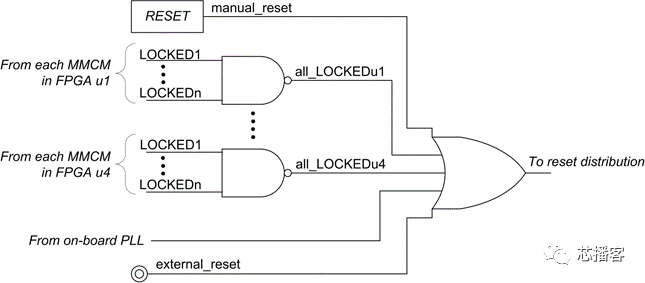

當SoC的規模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統。

2023-05-10 10:15:16 689

689 當SoC的規模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統。

2023-05-23 15:31:10 1015

1015 FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 1109

1109

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制,通常只有1000個左右的用戶IO引腳。

2023-05-23 17:12:35 2189

2189

多片FPGA之間的互連,經常提到多路復用的概念,也經常提到TDM的概念

2023-06-06 10:07:37 852

852

綜合工具的任務是將SoC設計映射到可用的FPGA資源中。自動化程度越高,構建基于FPGA的原型的過程就越容易、越快。

2023-06-13 09:27:06 879

879

當SoC系統的規模很大的時候,單片FPGA驗證平臺已經無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-06-19 15:42:08 1081

1081 所有形式的原型都為驗證硬件設計和驗證軟件提供了強大的方法,模型或多或少地模仿了目標環境。基于FPGA的原型設計在項目的關鍵后期階段尤其有益。用戶有幾個原型設計選項根據他們的主要需求,可以選擇各種基于軟件和硬件的技術來原型他們的設計。

2023-10-11 12:39:41 1808

1808

FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現在叫西門子EDA。

2024-01-22 09:21:01 3230

3230

FPGA原型驗證平臺與硬件仿真器在芯片設計和驗證過程中各自發揮著獨特的作用,它們之間存在明顯的區別。

2024-03-15 15:07:03 2340

2340 電子發燒友網站提供《實現多軸電機驅動系統內的多片C2000 PWM同步.pdf》資料免費下載

2024-09-03 09:25:17 2

2

? ? ?

? ? ? 電子發燒友App

電子發燒友App

評論