片上網絡Network-on-chip (NoC) 是一種應用于大規模集成電路(VLSI)系統中的,一種新的片上系統(System-on-chip)的設計方法。在一個片上網絡系統中,處理器核心(processor core),存儲器和專用的知識產權核(Intellectual Property cores)通過網絡,而不是通過當前常見的基于共享總線的方式相互連接。一個片上網絡系統由若干數據鏈路(data links)構成。這些數據鏈路通過片上網絡路由器相互連接而構成網絡。各種模塊通過網絡接口(NIC)接入網絡中。由于路由器可以進行路由決策與消息的暫存和轉發,那么信息就可以從任何源模塊經過若干數據連接傳輸和路由器的轉發到達任何目的模塊。由此可以看出,片上網絡系統將我們日常使用的宏觀通信網絡的概念引入到芯片上的(on-chip),模塊之間(inter-module)的通信中。兩者都是在復用的數據鏈路傳送信息。

????? 采用片上網絡的設計方法可以突破很多傳統集成電路設計方法的技術瓶頸。傳統的集成電路設計方法在兩個模塊之間采用點對點的獨享連接線(dedicated wires)連接。當集成電路的規模擴大到一定的程度(例如集成的晶體管達到10億級),傳統設計方法的弊端和局限逐漸凸顯出來。首先,模塊之間連接線將占據大量的芯片面積。其次,傳統的設計方法采用全局統一時鐘,隨著芯片規模的增大,速度的增加,龐大的時鐘樹將無法保證的全局時鐘的統一,并且時鐘樹本身將會產生大量的能耗。此外,為了應對不斷增加的對于芯片的的多功能、并行性需求,大規模的集成電路中的模塊數量的會進一步增加,傳統的集成電路設計方法在布線,可重用性,可擴展性等問題面臨了更加嚴峻的挑戰。

????? 由于采用了復用的數據鏈路以及分組交換的通信結構,片上網絡的設計方法可以比較好的解決上述問題。各芯片中的模塊如同Internet中的主機一樣,通過標準化的網絡接口(NIC)接入網絡,使用共享的網絡資源與目的模塊進行通信。這樣并行性和可擴展性得到充分保障。其次,片上網絡方法的一個重要特性是采用了GALS(Globally Asynchronous Local Synchronous, 全局異步局部同步)的設計構想,避免產生龐大的時鐘樹,同步問題得到解決。另外,由于片上網絡方法實現了芯片中的計算資源(各個處理,計算,存儲模塊)和通信資源(網絡)的分離,通信網絡對于單一的模塊是透明的,并且模塊之間設計也是相互獨立的,這在很大程度上順應了集成電路設計中的模塊化趨勢。

????? 在過去幾年里,一些研究機構提出了對NoC不同抽象層次的驗證方法的研究,一般的NoC驗證是基于軟件的仿真與建模,如用C、C++、Systemc進行系統級建模仿真,這樣驗證很靈活,但是在仿真時間上開銷很大,由于不能運行實際應用,所以不能對整個NoC系統進行驗證(如IP核的驗證)只能對NoC的互連網絡進行驗證。同時軟件驗證都是使用的合成的流量發生器,盡管它能在不同的網絡參數下對NoC的功耗與性能進行靈活的驗證,但是它過多的依賴于許多近似與假設影響了結果的精確性;另一方面,軟件仿真依賴于簡單的流量發生器,使得它們的驗證結果不能提供實際價值,因為網絡的性能與功耗嚴重依賴于網絡上實際運行的業務的通信流量特性。而盡管一些應用也可以用軟件驗證的高級抽象模型來描述,但是這只適合少數情況。因此為了得到有意義的結果,在實際應用下的原型驗證是非常有必要的。

????? 而在FPGA上進行原型驗證能滿足上述要求,它能提供更快的速度和更高的精確度。NoC作為一種芯片上的應用技術,最終是需要在硬件上具體實現的,軟件驗證并不能考慮到硬件的物理特性(如門延時)而是理論上周期精確,有可能導致理論上正確的結果在實際硬件上不能運行,而FPGA原型驗證不存在這些問題。FPGA原型讓一個設計師設計的各個方面進行評估的,說明的主要思想,并提供有關產品實施最終現實的預測,如作出準確的面積估計可行,以及各組成部分實際的硬件開銷估計和能源消耗的測量。

????? 隨著FPGA步入市場,它逐漸取代了ASIC。FPGA設計周期短,同時NRE費用少,加上它的可快速重配置,所以FPGA使用非常普遍。FPGA的可充配置性能根據系統需求的變化而一次由一次的進行微調,因此它能提供一個非常通用的平臺。而NoC又具有模塊化特性,因此能根據應用需求的變化而進行微小的修改而重復使用,所以在FPGA上對NoC進行原型驗證非常合適。

?

片上網絡概述與FPGA研究(連載1)

- FPGA(632043)

- 存儲器(171173)

- 片上網絡(12092)

相關推薦

熱點推薦

基于FPGA的多時鐘片上網絡設計

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1784

1784

1784

1784

利用片上高速網絡(2D NoC)創新地實現FPGA內部超高帶寬邏輯互連

Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-02-27 17:08:41 2288

2288

2288

2288新思科技UCIe IP解決方案實現片上網絡互連

與HBM DRAM堆疊裸片之間對高帶寬連接的需求。本文將深入探討UCIe支持的不同接口,以實現片上網絡(NoC)互連。

2025-08-04 15:17:24 2452

2452

2452

2452FPGA片內FIFO的功能概述和模塊劃分

1 功能概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內FIFO

2019-04-08 09:34:42

FPGA研究設計平臺為網絡發展加速

斯坦福大學與賽靈思研究實驗室(Xilinx Research Labs)聯手開發專門面向研究社群的第二代高速網絡設計平臺 NetFPGA-10G。該新型平臺采用最先進的技術,能夠幫助研究人員迅速構建

2011-07-19 15:51:05

FPGA基本開發流程概述

配置文件,接著完成下載并進行板級調試驗證。圖5.16 FPGA/CPLD設計簡易流程 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http://pan.baidu.com/s/1bndF0bt Xilinx FPGA入門連載

2019-01-28 02:29:05

片上網絡有什么優缺點?

片上網絡的研究才剛剛起步,還沒有在商業產品中廣泛應用。片上網絡的標準化可以增加組件的互連性,但會造成性能的損失,而對特定的片上系統,性能是片上系統的一個關鍵因素。

2019-09-19 09:10:34

Arm CoreLink NI-710AE片上網絡互連技術參考手冊

Arm?CoreLink? NI?710AE片上網絡互連是一種高度可配置的AMBA?兼容系統級互連,可實現汽車和工業應用的功能安全。使用NI?710AE,您可以創建一個非相干互連,該互連針對SoC

2023-08-08 06:24:43

Xilinx FPGA片內ROM FIFO RAM聯合實例之功能概述

1 功能概述該工程實例內部系統功能框圖如圖所示。我們通過IP核分別例化了ROM、FIFO和RAM,ROM有預存儲的數據可供讀取,將其放入FIFO中,隨后再讀出送到RAM供讀取。通過ISE集成的在線

2019-01-10 09:46:06

Xilinx FPGA入門連載38:SRAM讀寫測試之設計概述

`Xilinx FPGA入門連載40:SRAM讀寫測試之設計概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示,本

2015-12-18 12:57:01

Xilinx FPGA入門連載43:FPGA片內ROM實例之功能概述

Xilinx FPGA入門連載43:FPGA片內ROM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-06 12:22:53

Xilinx FPGA入門連載44:FPGA片內ROM實例之ROM配置

`Xilinx FPGA入門連載44:FPGA片內ROM實例之ROM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2016-01-08 13:12:44

Xilinx FPGA入門連載45:FPGA片內ROM實例之功能仿真

Xilinx FPGA入門連載45:FPGA片內ROM實例之功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫

2016-01-11 12:17:28

Xilinx FPGA入門連載46:FPGA片內ROM實例之chipscope在線調試

`Xilinx FPGA入門連載46:FPGA片內ROM實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1

2016-01-18 12:30:14

Xilinx FPGA入門連載47:FPGA片內RAM實例之功能概述

Xilinx FPGA入門連載47:FPGA片內RAM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-20 12:28:28

Xilinx FPGA入門連載48:FPGA片內RAM實例之RAM配置

`Xilinx FPGA入門連載48:FPGA片內RAM實例之RAM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打開

2016-01-22 13:39:24

Xilinx FPGA入門連載49:FPGA片內RAM實例之功能仿真

`Xilinx FPGA入門連載49:FPGA片內RAM實例之功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫

2016-01-25 12:55:23

Xilinx FPGA入門連載50:FPGA片內RAM實例之chipscope在線調試

Xilinx FPGA入門連載50:FPGA片內RAM實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

Xilinx FPGA入門連載51:FPGA片內FIFO實例之功能概述

Xilinx FPGA入門連載51:FPGA片內FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-02-26 10:26:05

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

Xilinx FPGA入門連載53:FPGA片內FIFO實例之功能仿真

`Xilinx FPGA入門連載53:FPGA片內FIFO實例之功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx

2016-03-02 12:30:57

Xilinx FPGA入門連載54:FPGA 片內FIFO實例之chipscope在線調試

`Xilinx FPGA入門連載54:FPGA 片內FIFO實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-04 13:13:12

Xilinx FPGA入門連載55:FPGA 片內異步FIFO實例之功能概述

`Xilinx FPGA入門連載55:FPGA 片內異步FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

Xilinx FPGA入門連載57:FPGA 片內異步FIFO實例之功能仿真

`Xilinx FPGA入門連載57:FPGA 片內異步FIFO實例之功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-03-16 11:32:11

Xilinx FPGA入門連載58:FPGA 片內異步FIFO實例之chipscope在線調試

`Xilinx FPGA入門連載58:FPGA 片內異步FIFO實例之chipscope在線調試特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:13:05

Xilinx FPGA入門連載59:FPGA 片內ROM FIFO RAM聯合實例之功能概述

`Xilinx FPGA入門連載59:FPGA 片內ROM FIFO RAM聯合實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:43:36

Xilinx FPGA入門連載60:FPGA 片內ROM FIFO RAM聯合實例之功能仿真

`Xilinx FPGA入門連載60:FPGA 片內ROM FIFO RAM聯合實例之功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-18 09:20:25

Xilinx FPGA入門連載82:LCD字符顯示驅動之實驗概述

Xilinx FPGA入門連載82:LCD字符顯示驅動之實驗概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示

2016-06-15 17:50:38

Xilinx FPGA入門連載82:LCD字符顯示驅動之實驗概述

`Xilinx FPGA入門連載82:LCD字符顯示驅動之實驗概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示

2016-06-15 17:50:37

【連載視頻教程(十四)】小梅哥FPGA設計思想與驗證方法視頻教程之1搭建串口收發與存取雙口RAM簡易應用系統

本帖最后由 小梅哥 于 2016-1-18 12:58 編輯

大家好,今天,小梅哥繼續連載本人精心錄制和編輯的FPGA學習系列教程——《小梅哥FPGA設計思想與驗證方法視頻教程》。教程充分考慮

2015-10-23 13:01:50

例說FPGA連載30:PLL例化配置與LED之功能概述

`例說FPGA連載30:PLL例化配置與LED之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例使用Quartus II

2016-09-09 18:29:24

例說FPGA連載36:DDR控制器集成與讀寫測試之功能概述

`例說FPGA連載36:DDR控制器集成與讀寫測試之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例對Altera提供

2016-10-08 17:05:55

例說FPGA連載37:DDR控制器集成與讀寫測試之FPGA片內存儲器概述

`例說FPGA連載37:DDR控制器集成與讀寫測試之FPGA片內存儲器概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 片內存儲器

2016-10-10 17:08:22

例說FPGA連載38:DDR控制器集成與讀寫測試之FPGA片內RAM概述

`例說FPGA連載38:DDR控制器集成與讀寫測試之FPGA片內RAM概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 我們所

2016-10-12 17:18:25

例說FPGA連載46:Qsys系統搭建與軟件開發之功能概述

例說FPGA連載46:Qsys系統搭建與軟件開發之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖5.1所示,本實例

2016-11-14 16:00:53

例說FPGA連載66:AV視頻采集之In-System Sources and Probes概述

`例說FPGA連載66:AV視頻采集之In-SystemSources and Probes概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2017-01-09 16:03:46

例說FPGA連載67:AV視頻采集之移位寄存器概述

例說FPGA連載67:AV視頻采集之移位寄存器概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 在很多涉及迭代運算的應用中,常常需要用

2017-01-15 17:13:42

例說FPGA連載72:FX2 bulkloop實例之功能概述

`例說FPGA連載72:FX2 bulkloop實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FX2(CY7C68013

2017-02-13 13:16:19

例說FPGA連載75:FX2與FPGA之SignalTap II與功能概述

`例說FPGA連載75:FX2與FPGA之SignalTap II與功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FPGA

2017-02-19 20:28:01

例說FPGA連載80:TXT文本閱讀器設計之功能概述

`例說FPGA連載80:TXT文本閱讀器設計之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例是在工程實例8的基礎上,完善

2017-03-16 15:40:28

例說FPGA連載83:工業現場實時監控界面設計之功能概述

`例說FPGA連載83:工業現場實時監控界面設計之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例在之前幾個案例的基礎上

2017-03-23 22:30:51

例說FPGA連載99:雙攝像頭圖像采集之功能概述

`例說FPGA連載99:雙攝像頭圖像采集之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例功能框圖20.1如下所示。攝像頭

2017-05-11 21:26:52

勇敢的芯伴你玩轉Altera FPGA連載51:Altera FPGA配置方式概述

```勇敢的芯伴你玩轉Altera FPGA連載51:Altera FPGA配置方式概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1

2018-03-04 22:12:49

勇敢的芯伴你玩轉Altera FPGA連載61:PLL概述

`勇敢的芯伴你玩轉Altera FPGA連載61:PLL概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD PLL(Phase

2018-04-10 21:57:51

勇敢的芯伴你玩轉Altera FPGA連載78:FPGA片內ROM實例之功能概述

`勇敢的芯伴你玩轉Altera FPGA連載78:FPGA片內ROM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 該工程

2018-06-16 19:39:24

勇敢的芯伴你玩轉Altera FPGA連載83:FPGA片內RAM實例之功能概述

`勇敢的芯伴你玩轉Altera FPGA連載83:FPGA片內RAM實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 該

2018-06-30 17:16:32

勇敢的芯伴你玩轉Altera FPGA連載85:FPGA片內RAM實例之RAM配置

`勇敢的芯伴你玩轉Altera FPGA連載85:FPGA片內RAM實例之RAM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 在

2018-07-17 22:15:28

勇敢的芯伴你玩轉Altera FPGA連載90:FPGA片內ROM FIFO RAM聯合實例

`勇敢的芯伴你玩轉Altera FPGA連載90:FPGA片內ROM FIFO RAM聯合實例特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-09-07 22:16:37

基于FPGA的多時鐘片上網絡該怎么設計?

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

基于遺傳算法的片上網絡虛通道分配算法

】:CNKI:SUN:HZLG.0.2010-03-010【正文快照】:為解決蟲孔交換機制下的隊列頭阻塞問題,大多數片上網絡(NoC)[1~3]采用了虛通道技術[4,5],利用該技術能減少隊列頭阻塞的次數

2010-04-22 11:34:25

如何利用FPGA研究設計平臺為網絡發展加速?

斯坦福大學與賽靈思研究實驗室(Xilinx Research Labs)聯手開發專門面向研究社群的第二代高速網絡設計平臺 NetFPGA-10G。該新型平臺采用最先進的技術,能夠幫助研究人員迅速構建

2019-08-27 08:30:57

如何利用片上高速網絡創新地實現FPGA內部超高帶寬邏輯互連?

NoC為FPGA設計提供了哪些優勢?NoC在FPGA內部邏輯互連中發揮的作用是什么?如何利用片上高速網絡創新地實現FPGA內部超高帶寬邏輯互連?

2021-06-17 11:35:28

請問使用片上網絡來互連DSP48A會降低性能嗎?

與FPGA中的普通路由相比,使用片上網絡來互連DSP48A會降低性能嗎?以上來自于谷歌翻譯以下為原文Will the use of network on chip to interconnect

2019-06-28 09:39:03

一種用于片上網絡的交換開關結構

半導體技術的飛速發展推動了片上系統設計進入到片上網絡階段。為了進一步研究其結構及不同工藝對其的影響,文章分析了片上網絡對于片上系統的優越性,并針對其重要組成

2009-08-21 09:03:08 12

12

12

12片上網絡通信性能分析建模與緩存分配優化算法

該文建立了一種面向應用設計的片上網絡的性能分析模型,并在此基礎上提出了片上緩存優化策略和分配算法。在硬件實現平臺上的仿真表明,該文建立的片上網絡分析模型能很好

2009-11-18 15:20:06 9

9

9

9片上網絡的功耗研究

隨著芯片上晶體管數量發展到10億數量級,功耗逐漸成為芯片設計的首要制約因素。本文分別從CMOS電路和網絡通訊兩個層面上來分析片上網絡(NoC)的功耗,并給出了相應的功耗

2009-12-14 09:51:17 6

6

6

6片上網絡系統網絡層設計與研究

本文參照傳統的OSI(Open Systems Interconnection)模型與TCP/IP 模型對片上網絡系統模型層次結構進行了按照片上網絡特點進行的劃分。文中還對片上網絡的網絡層設計中的各種拓撲結

2009-12-14 09:54:49 8

8

8

8片上網絡關鍵技術研究

半導體技術的快速發展以及芯片上系統應用復雜度的不斷增長,使得片上互連結構的吞吐量、功耗、延遲以及時鐘同步等問題更加復雜,出現了將通信機制與計算資源分離的片上網絡。

2010-02-24 11:55:49 17

17

17

17一種用于片上網絡的交換開關結構

半導體技術的飛速發展推動了片上系統設計進入到片上網絡階段。為了進一步研究其結構及不同工藝對其的影響,文章分析了片上網絡對于片上系統的優越性,并針對其重要組成部

2010-07-17 16:53:50 19

19

19

19片上網絡關鍵技術研究

半導體技術的快速發展以及芯片上系統應用復雜度的不斷增長,使得片上互連結構的吞吐量、功耗、延遲以及時鐘同步等問題更加復雜,出現了將通信機制與計算資源分離的片上網絡。

2010-07-17 16:56:32 33

33

33

33一種片上網絡自適應路由算法仿真與驗證

針對片上網絡的死鎖問題,提出一種片上網絡自適應路由算法——虛擬網絡(VN)路由算法,該算法根據報文源地址和目的地址將網絡分成4個虛擬網絡。一旦報文在某個給定的虛擬

2010-07-21 16:09:40 13

13

13

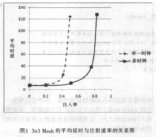

13基于FPGA 的高效率多時鐘的虛擬直通路由器

1 多時鐘片上網絡架構的分析

片上網絡結構包含了拓撲結構、流量控制、路由、緩沖以及仲裁。選擇合適網絡架構方面的元素,將對片上網絡的性能產生重大影響[2]

2010-09-02 09:43:47 1061

1061

1061

1061

片上網絡核心芯片的驗證

為提高芯片驗證與測試的可靠性,針對片上網絡核心芯片的結構特點,設計出一種基于宿主機/目標機通信模式的測試系統。重點描述了測試系統軟硬件的設計與實現,并采用Stratix系列FPGA芯片進行原型測試和驗證。實驗結果表明,該系統可對芯片的復位、實現功能及

2011-01-15 15:46:29 31

31

31

31對片上網絡低功耗的分析

從建立功耗模型出發, 在集成電路不同的設計層次、片上網絡通訊功耗以及NoC 映射問題等方面來討論NoC 的低功耗設計, 綜合了現有功耗解決的最新方案, 對NoC 的功耗研究做了一個比

2011-06-30 09:32:17 1471

1471

1471

1471Sonics推出業內首款GHz級片上網絡

世界頭號片上通信IP供應商Sonics公司(R)今天面向高級并發應用處理和系統級設計推出了業內首款GHz級片上網絡(NOC)SonicsGN(TM)(SGN)。

2011-09-22 18:09:17 2000

2000

2000

2000片上網狀網絡成大規模并行處理器首選架構

麻省理工學院(MIT)的研究人員指出,今天我們都在使用片上總線和環狀拓樸,但它們所帶來的麻煩可能要比它們能貢獻的價值還要多,這也推動了片上網狀網絡(on-chip mesh networ

2012-04-18 08:39:53 605

605

605

605一種低延時片上網絡路由器的設計與實現

通過分析流水線結構和單周期結構的片上網絡路由器,提出了一種低延時片上網絡路由器的設計,并在SMIC 0.13um Mixed-signal/RF 1.2V/3.3V工藝進行流片驗證。芯片測試結果表明,該路由器可以

2013-06-25 16:25:01 40

40

40

40片上網絡的SystemC建模研究

為了實現軟硬件協同設計和提高仿真速度的需求,采用SystemC語言的建模方法,通過對片上網絡體系結構的研究,提出了一種片上網絡的建模方案,并對一個mesh結構完成了SystemC的建模設

2013-07-30 11:46:44 42

42

42

42基于FPGA的多時鐘片上網絡虛擬直通路由器設計

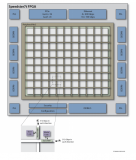

網絡拓撲:在設計中,選擇Mesh拓撲結構。Mesh結構擁有最小的面積開銷以及低功耗的特點。此外,Mesh的線性區的節點數量規模大以及通道較寬。同時,Mesh也能很好地映射到FPGA下的底層路由結構,降低了FPGA 邏輯擁塞和路由器的功耗。

2018-07-22 09:44:00 2593

2593

2593

2593

基于FPGA和ARM9的片上網絡系統硬件平臺

上的設備在通信時對總線的獨占性以及單一系統總線對同步時鐘的要求,使得在片上IP核越來越多的芯片中,不可避免地存在通信效率低下、全局同步時鐘開銷大等問題。 片上網絡NoC(Network on Chip)的提出有效地解決了上述問題。該系統借鑒了計算機網絡中分組交換的通

2017-11-30 07:57:21 718

718

718

718

基于Prim初始種群選取優化遺傳算法的三維片上網絡低功耗映射

針對將計算任務合理地映射到三維片上網絡( NoC)的問題,提出了一種基于遺傳算法(GA)的改進算法。GA具有快速隨機的搜索能力,Prim算法可在加權連通圖內得到最小生成樹,改進算法結合了兩種算法

2017-12-07 14:40:49 0

0

0

0MPI集合操作的定制化片上網絡設計

根據計算趨近數據的原則,提出面向MPI集合操作的定制化片上網絡設計方法,通過增強現有片上路由器的硬件功能實現MPI集合操作在網絡層的加速。設計MPI歸約操作,將其擴展至多種集合操作,并與一種針對

2018-02-02 15:46:50 0

0

0

0CPU-GPU異構系統下的片上網絡仲裁機制研究

在CPU-GPU異構系統架構中,由于GPU程序的多線程特點,大多數GPU程序會壟斷系統中的共享資源,例如片上網絡。這將給CPU程序的性能造成很大的損失。我們發現有一些GPU程序性能對網絡延遲表現

2018-04-26 16:33:13 1

1

1

1手機移動網絡上網和WIFI上網的對比

移動網絡上網與WiFi連接上網,是移動設備上的兩大高手。一個主室外, 一個主室內。WiFi上網是移動網絡的室內覆蓋補充。WiFi遲早將被淘汰的言論層出不窮。下面我們從耗電、速度、經濟、安全等方面來說說。

2020-03-21 15:06:04 16654

16654

16654

16654三維片上網絡高維超立方裂變拓撲結構

三維片上網絡是解決片上網絡通訊瓶頸的重要途徑,拓撲結構是三維片上網絡研究中的關鍵問題。針對高維超立方拓撲結構節點度迅速増加,岀現通訊瓶頸的問題,提岀一種髙維超立方裂變拓撲結構,該拓撲在同等網絡規模下

2021-05-11 17:00:54 9

9

9

9淺析可視化的片上網絡(NoC)性能

1. 概述 Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。2D NoC如同在FPGA

2021-11-12 09:21:22 2972

2972

2972

2972

【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第三章 硬件資源詳解 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-11-21 14:06:03 19

19

19

19【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-11-24 14:36:07 13

13

13

13【正點原子FPGA連載】第九章按鍵控制LED燈實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第九章按鍵控制LED燈實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-12-04 13:06:13 14

14

14

14【正點原子FPGA連載】第三十七章雙路高速AD實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第三十七章雙路高速AD實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-12-04 15:06:05 11

11

11

11【正點原子FPGA連載】第三十五章高速AD/DA實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第三十五章高速AD/DA實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-12-04 15:06:06 12

12

12

12【正點原子FPGA連載】第十五章 窗口門狗(WWDG)實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

【正點原子FPGA連載】第十五章 窗口門狗(WWDG)實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

2021-12-05 11:21:06 12

12

12

12 電子發燒友App

電子發燒友App

評論