晶心科技今天宣布推出AndesCore? 27系列處理器核心,成為RISC-V指令集架構中領先支持向量擴展架構(RISC-V V-extension)的處理器。

2020-01-03 14:56:38 3521

3521 領先的嵌入式分析技術開發商UltraSoC日前宣布:其RISC-V處理器跟蹤解決方案開始全面供貨,這是業界首款商用RISC-V處理器跟蹤IP產品,也是RISC-V生態系統中關鍵的推動性技術。該跟蹤功能的加入意味著UltraSoC可以提供最全面的RISC-V商業化調試解決方案。

2018-02-09 10:26:25 8281

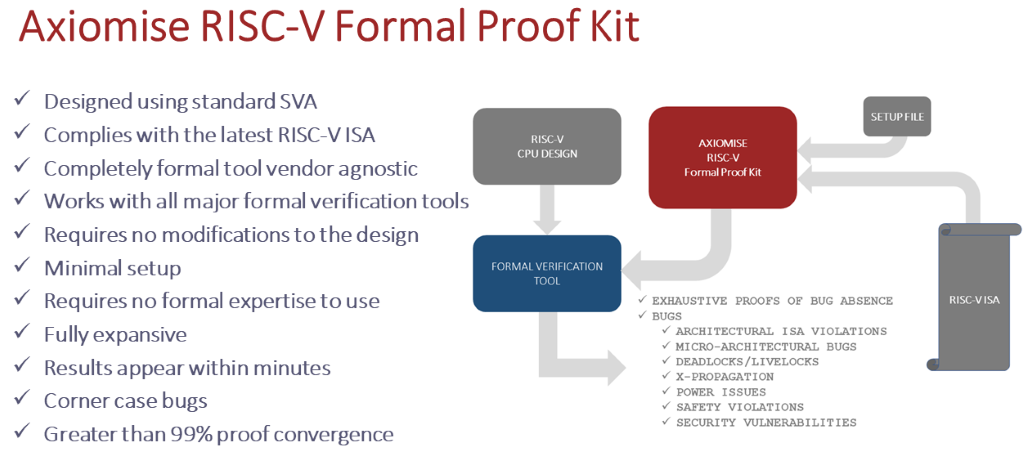

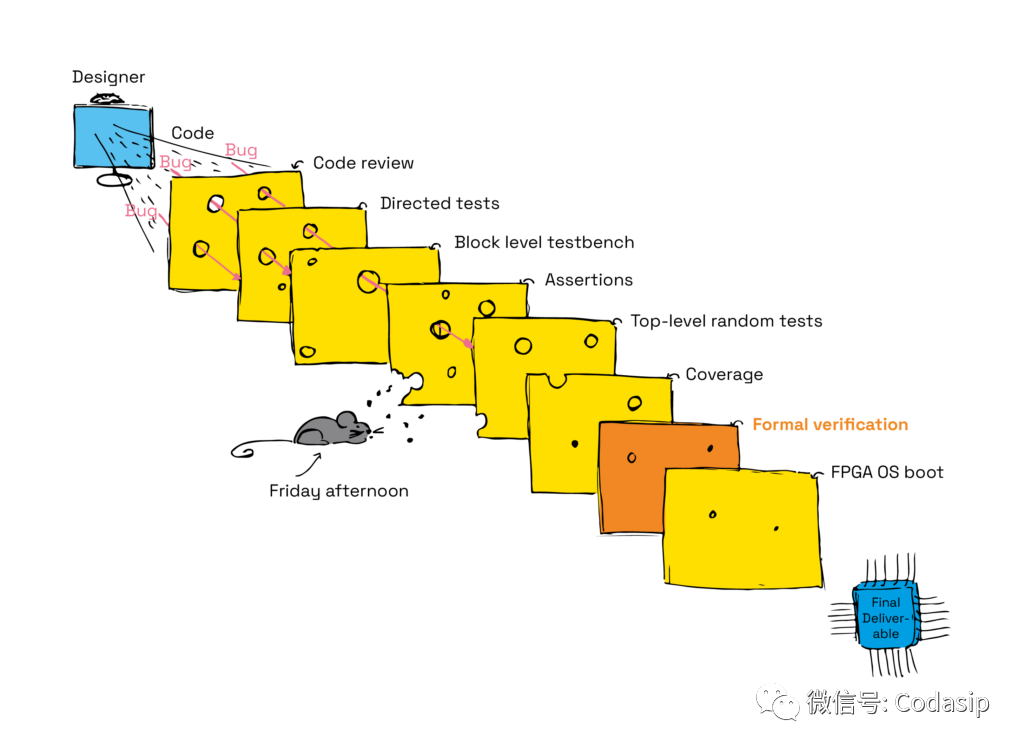

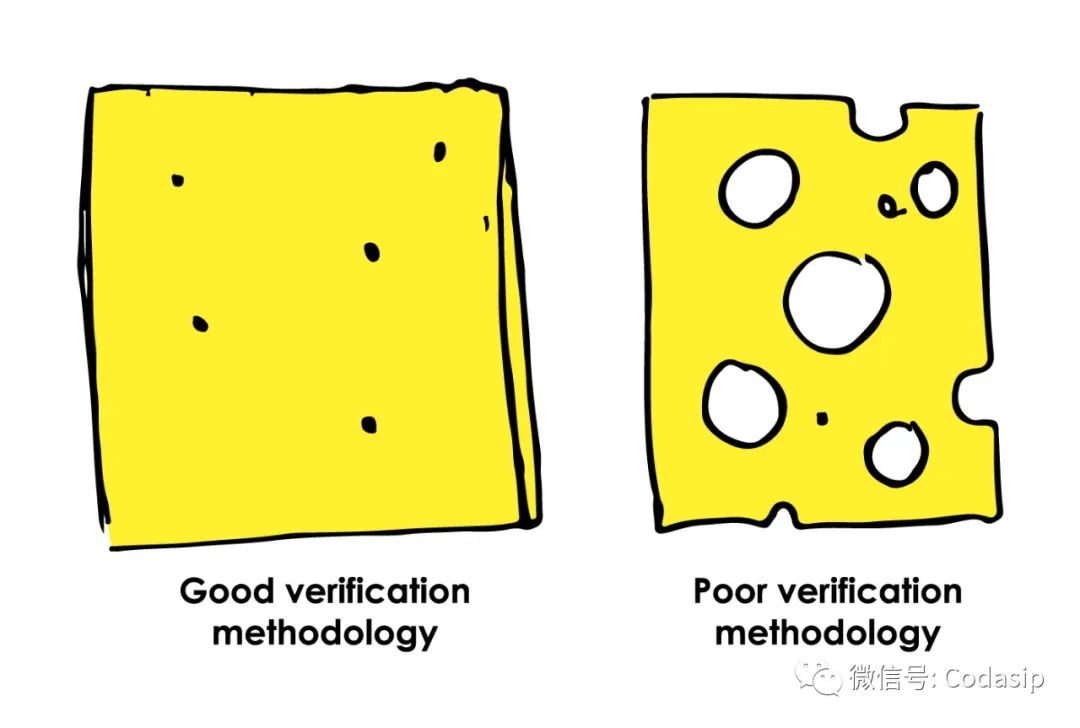

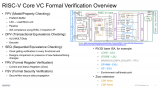

8281 進行全面和徹底的處理器測試。Codasip不斷在處理器驗證方面投入巨資,以再接再厲為業界提供最高質量的RISC-V處理器半導體知識產權(IP)。 Siemens EDA的OneSpin工具提供了一個先進

2022-05-07 13:55:42 7148

7148

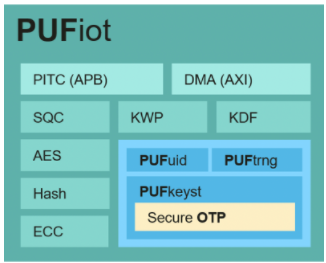

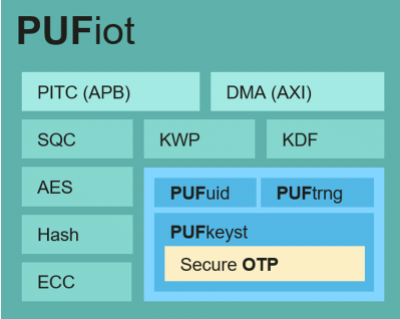

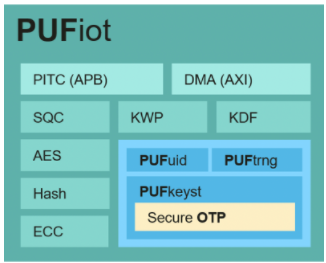

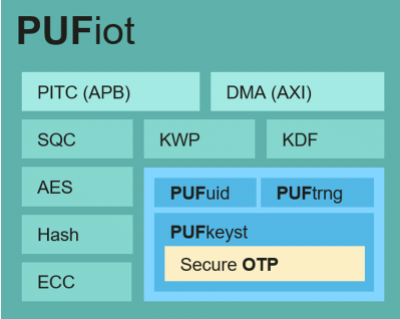

為了保護 IoT 應用程序,PUFsecurity 利用芯片指紋技術來強化信任根,并開發了 PUFiot,這是一種具有廣泛安全邊界的安全協處理器,可以輕松地集成到安全的 RISC-V 系統中。

2022-08-16 09:31:11 2189

2189

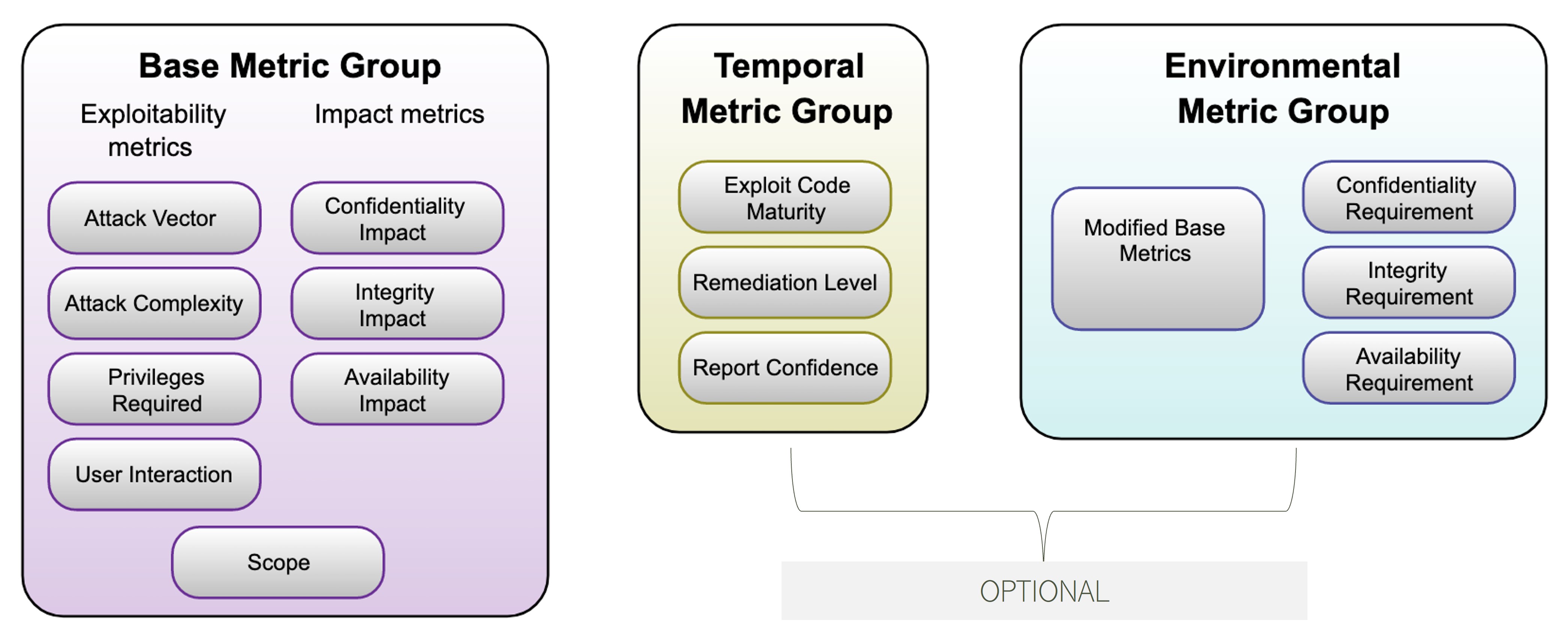

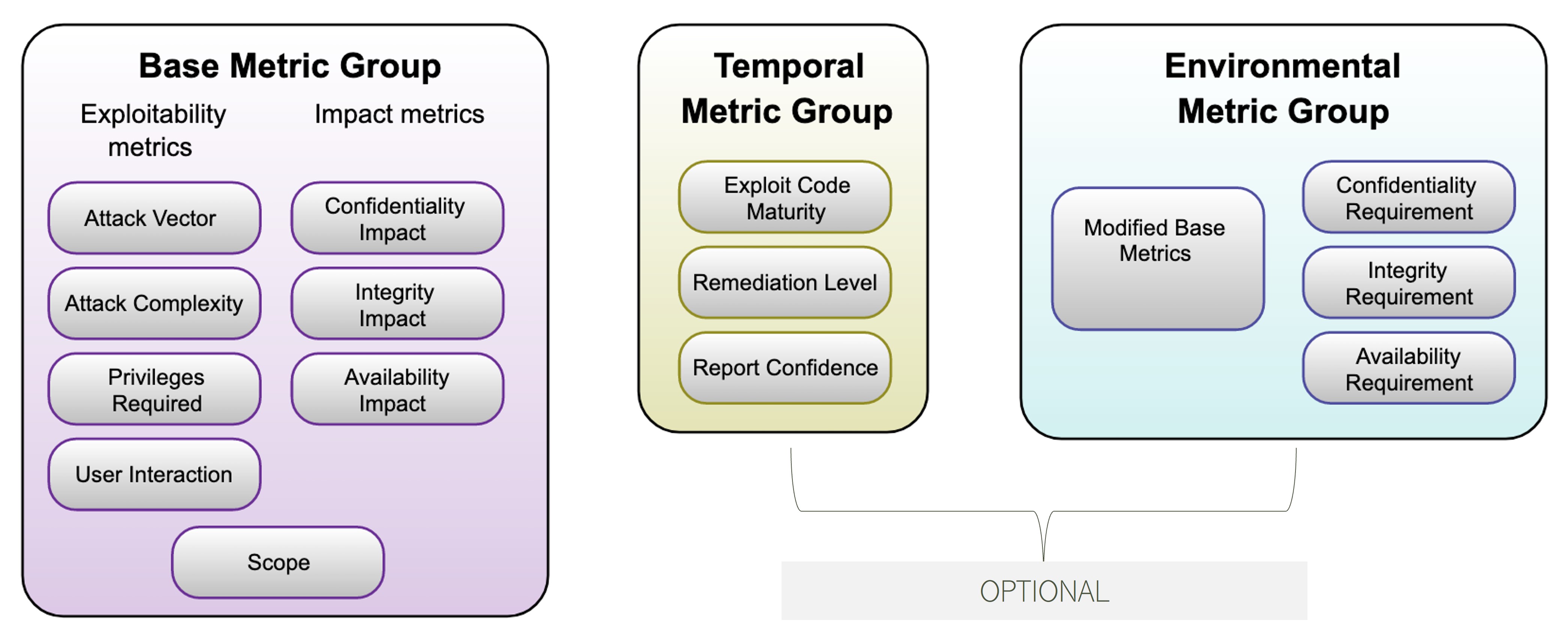

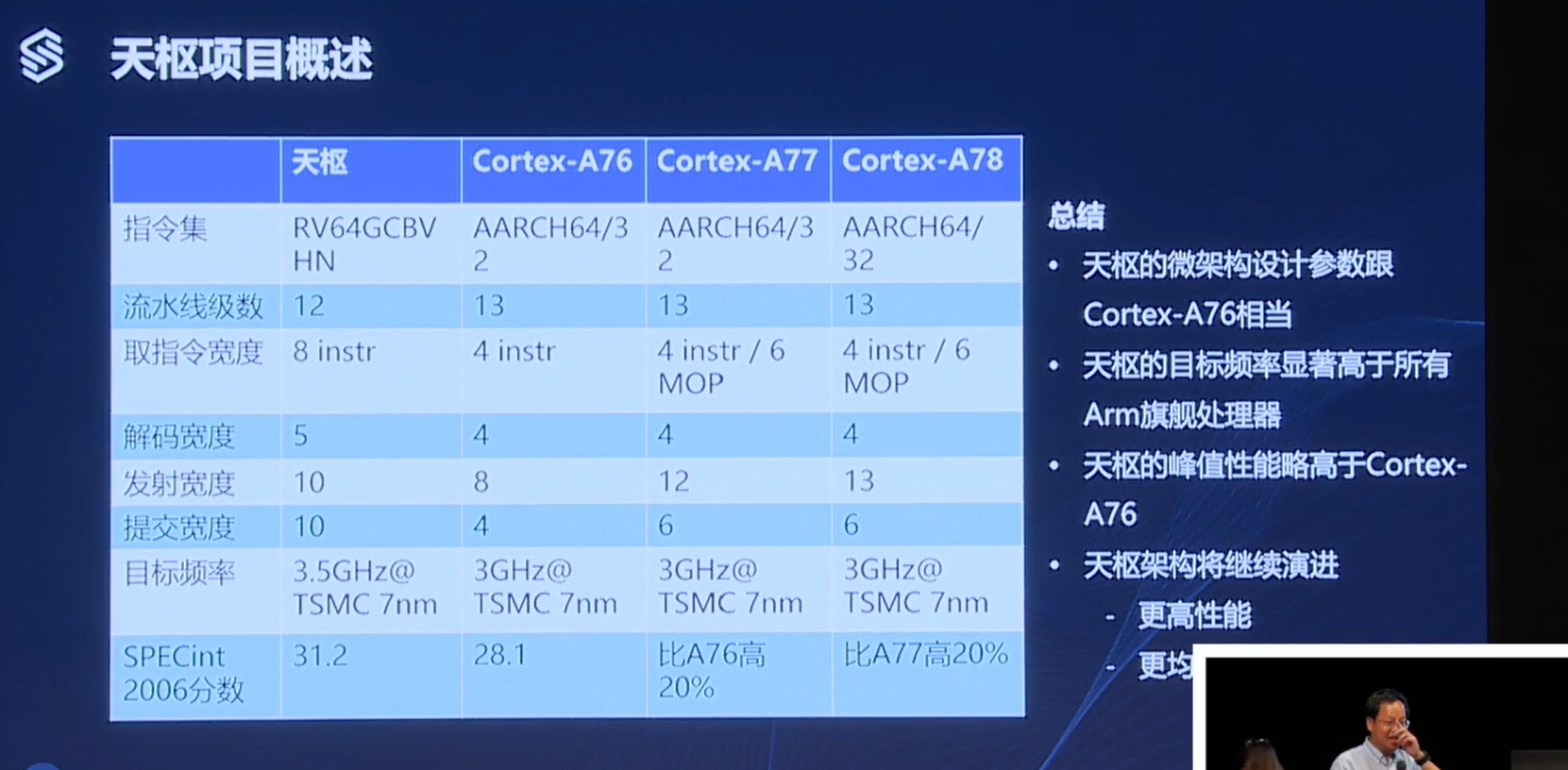

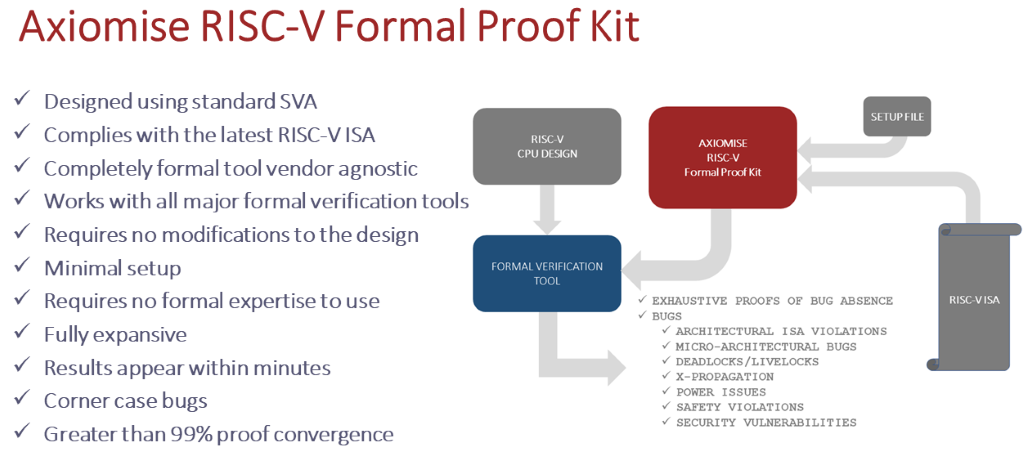

。 本文討論了與硬件安全驗證相關的一些挑戰,并介紹了一種基于形式的方法來解決。實現流行的RISC-V指令集架構(ISA)的設計示例展示了這種方法的強大功能。 安全驗證概述 對處理器進行全面有效的驗證是電子開發人員面臨的最大挑戰

2023-03-16 10:47:01 10765

10765

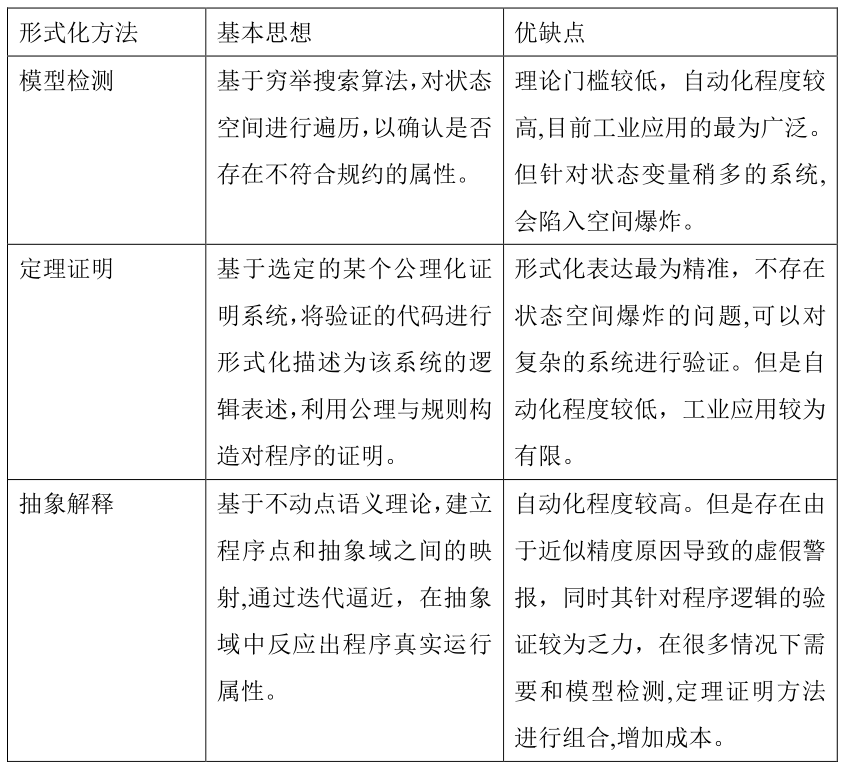

形式化工程方法,是以軟件形式化方法理論為基礎,以系統化的工程方法引導工業界工程人員構建高質量的軟件模型,用以引導后續的代碼編寫和相關測試分析。并選取了工業實際場景中的某操作系統的調度系統的形式化驗證

2023-03-24 11:01:26 2508

2508

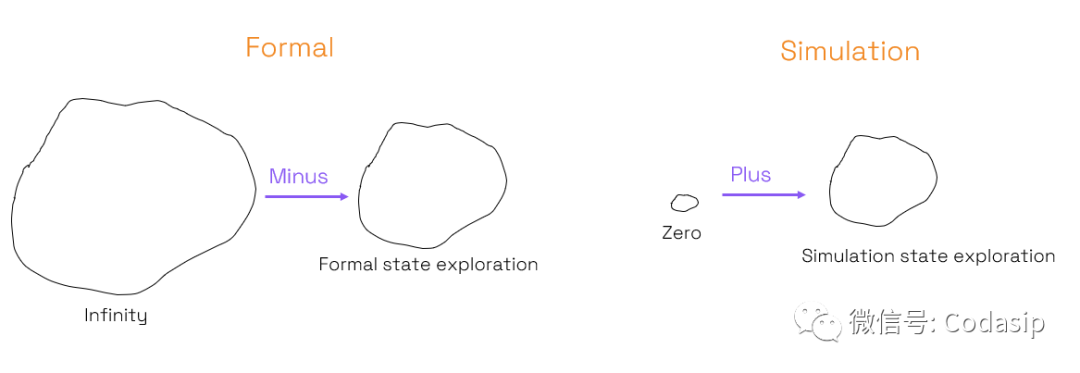

“在未來五年內仿真將逐漸被淘汰,僅用于子系統和系統級驗證。與此同時,形式化驗證方法已經開始處理一些系統級任務。隨著技術發展,更多Formal相關的商業標準化會推出。” Intel?fellow

2023-09-01 09:10:04 2183

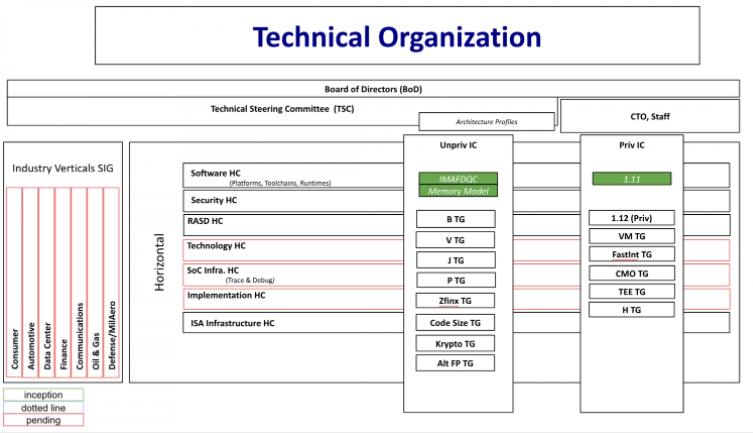

2183 芯片設計工作中必不可少的就是IP核,為此不少企業推出了自己的RISC-V處理器IP。但單靠IP并不足以支撐龐大的RISC-V生態,為了實現生態發展與統一,許多專注于RISC-V處理器IP的公司也各自發布了自己的對策。

2020-10-08 00:09:50 12504

12504 無論是x86、Arm還是新秀RISC-V,大家談及基于這些架構的處理器時,除了對比性能、功耗以外,不免會說到造就當下處理器差異化的另一大因素,那就是制造工藝。臺積電、中芯國際、三星還有英特爾,隨著

2022-06-24 09:40:58 4505

4505 的寬度):32位,64位,128位指令集模塊:標識該處理器支持的指令集模塊集合基本整數(Integer)指令集: RISC-V唯一強制要求實現的基礎指令集,其他指令集都 是可選的擴展模塊。擴展模塊指令集: RISC-V允許在實現中以可選的形式實現其他 標準化和非標準化的指令集擴展。特定組合“IMA

2021-12-09 06:31:44

RISC-V處理器是開源的,那開發環境需要廠商自己開發還是沿用傳統的開發環境呢?比如keil

2024-01-13 19:18:35

RISC-V和開源處理器之間是什么關系?

2023-03-09 10:06:52

為自動駕駛汽車等應用開發新的RISC-V芯片設計;GreenWaves推出了基于RISC-V的低功率AI物聯網(IoT)應用處理器;晶晨半導體推出具有RISC-V安全內核的SoC芯片;華米發布了用于生物識別

2021-06-18 20:57:35

本期文章目錄一個小型RISC-V開源處理器核介紹!#SOC#FPGA#RISC-V點擊閱讀數字積木從零開始寫RISC-V處理器(超詳細)#RISC-V點擊閱讀數字積木為什么說模擬工程...

2021-07-23 09:42:00

RISC-V是什么?有哪些特點?如何去設計RISC-V處理器?

2021-06-18 09:24:03

回顧過去幾年的集成電路產業里,RISC-V是一個繞不過去的熱詞。作為一項以“開源”為賣點的技術,RISC-V自面世以來,就在相對古板的處理器設計領域激起了不小的浪花。由于RISC-V的開源特性造就了

2020-06-22 16:55:03

模塊化設計提高了RISC-V的適應性和靈活性。

簡潔的指令集:RISC-V的設計簡潔,指令數量相對較少,這有助于提高處理器的執行速度和降低功耗。

強大的社區支持:RISC-V擁有龐大的社區支持,包括學術界

2024-04-28 09:03:24

。這種模塊化設計提高了RISC-V的適應性和靈活性。

簡潔的指令集 :RISC-V的設計簡潔,指令數量相對較少,這有助于提高處理器的執行速度和降低功耗。

強大的社區支持 :RISC-V擁有龐大的社區支持

2024-04-28 08:51:42

RISC-V架構秉承簡單的設計哲學。體現為:在處理器領域,主流的架構為x86與ARM架構。x86與ARM架構的發展的過程也伴隨了現代處理器架構技術的不斷發展成熟,但作為商用的架構,為了能夠保持架構的向后兼容性

2021-06-18 19:41:21

10 月 19 日,2021 云棲大會上,平頭哥開源了玄鐵RISC-V系列處理器,并開放了工具及系統軟件。這次的開源對國內的RISC-V生態圈具有非常重要的意義。關注了一下這次開源發布的東...

2022-02-28 08:15:04

Performance系列高性能應用處理器;Ventana開發了面向數據中心的多核 RISC-V小芯片Veyron V1;以及MIPS公司宣稱放棄自研架構而押注RISC-V,目前MIPS正在利用其經過硅

2023-05-30 14:11:59

得RISC-V多核芯片能夠更好地適應AI算法的不同需求,包括深度學習、神經網絡等,從而提高芯片的性能和效率,降低成本,使AI邊緣計算晶片更具競爭力。

再者,RISC-V的多核設計可以進一步提高處理器

2024-04-28 09:20:06

RISC-V是一個開源的指令集架構,它屬于一個開放的、非營利性質的基金會,而基金會將謹慎地發展和維護這個開源的指令集架構。 計算機體系結構的傳統方法是增量ISA,新處理器不僅必須實現新的ISA擴展,還必須實現

2023-03-30 16:40:41

:編譯器如何優化生成的機器代碼也會影響Drystone的得分。優化的編譯器能夠生成更高效的機器代碼,從而提高性能。

提高 RISC-V 在 Drystone 測試中得分的方法主要有:

優化處理器

2025-10-21 13:58:40

重磅推薦|ACRN 之InterruptWindow功能正確性形式化驗證

2020-06-18 16:04:42

HPM5E31IGN單核 32 位 RISC-V 處理器在當今嵌入式系統領域,RISC-V架構正以開源、靈活和高性價比的優勢快速崛起。HPM5E31IGN作為先楫半導體的一款單核32位RISC-V

2025-05-29 09:23:16

MIPS Technologies不再設計MIPS處理器。相反,它加入了RISC-V陣營,放棄了具有悠久歷史和技術聯系的同名架構。此舉顯然預示著MIPS作為CPU系列的終結,并進一步減少了可用處理器

2021-03-09 19:30:07

由歐洲航天局支持,由蘇黎世聯邦理工學院和博洛尼亞大學的工程師開發的 Occamy 處理器現已流片。它使用了兩個 216 個 32 位 RISC-V 內核的 chiplet 小芯片、未知數量的 64

2023-05-13 08:44:36

的處理器指令集,是構建芯片生態和發展芯片技術的核心部分,其重要性不言而喻。在此背景下,RISC-V有望成為新的選擇。盡管具有通用、開放與免費的先期優勢,但相比已經成熟的Arm和Intel x86,國內

2020-11-14 09:26:41

,創建實現自有加速器算法的自定義異構集群。RISC-V作為一種ISA,我們一開始是在處理器內核中采用吸引人的通用構建塊,然后在此基礎上進行構建,同時還利用最好的商業工具增強使用者的信心。所以,IP

2024-11-26 20:20:35

siFive搞RISC-V

賽昉搞RISC-V

香山搞RISC-V

到底什么是RISC-V?

先不問有什么用,RISC-V目前的能力來說,工業有沒有可能?

2024-02-02 10:41:21

CPU設計領域里的門外漢,再加上很少業余時間,為此一度猶豫不決。但是直覺告訴我已近不能再等了,我決定開始自學verilog和FPGA,用簡單易懂的方式寫一個RISC-V處理器并且把它開源出來,在提高自身

2022-08-22 18:25:55

都是跨平臺、輕量級的工具。iverilog用來編譯verilog代碼,gtkwave用來查看波形。驗證一個處理器,首先是能跑通各個指令,RISC-V官方提供了指令兼容性測試程序,這些程序是用匯

2022-08-23 15:05:44

免費的接口規范,并不會受美國管制的影響。但是,基于RISC-V開發的處理器是以商品形式存在的,故而美國企業研制的RISC-V處理器會受到美國出口管制。而美國以外的企業(包括歐洲、中國等)自主研制

2020-06-22 16:47:55

RISC-V指令集體系結構(ISA)易于擴展,并且沒有指定關于特定RISC-V微控制器或片上系統(SoC)實現的所有內容。因此,FreeRTOS RISC-V移植也是可擴展的-它提供了一個處理所有

2019-11-29 15:54:41

RISC-V架構的開源處理器與SoC。1 RISC-V簡介1.1 RISC-V的基本設計RISC-V是一個典型三操作數、加載-存儲形式的RISC架構,包括三個基本指令集和6個擴展指令集,如表1所示,其中

2020-07-27 18:09:27

開發出商用的RISC-V處理器還需要哪些開發工具和環境?

處理器是軟硬件的交匯點,所以必須有完善的編譯器、開發工具和軟件開發環境(IDE),處理器內核才能夠被用戶順利使用起來。目前RISC-V具有

2023-11-18 06:05:15

協處理器進行gpio操作,執行完成后 ULP RISC-V 協處理器退出,等待下一個ULP喚醒周期。可當在主MCU程序中使能 esp_sleep_enable_ulp_wakeup() 函數后,每當

2023-02-09 06:52:26

, 64位Linux兼容版U2,U7處理器。并著手于簡化芯片設計領域的技術鴻溝,提供云端的模塊化設計和驗證程序。SIFIVE目前也是RISC-V領域產品系列最全,技術相對領先的公司。其它芯片設計公司

2020-08-02 11:50:33

我非常想了解如果想設計一個類似risc-v的處理器,整個開發流程是怎樣的?

2023-12-09 18:39:01

如題,現在risc-v發展的如此迅猛,不知道這些處理器主要應用在哪些行業比較多呢?

2023-12-09 18:37:01

我在ULP RISC-V協處理器的例程中,沒有發現有對ADC的操作,請問RISC-V協處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數據。

2023-02-13 06:34:36

我在ULP RISC-V協處理器的例程中,沒有發現有對ADC的操作,請問RISC-V協處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數據。

2023-03-06 06:33:44

是由美國伯克利大學的 Krest 教授及其研究團隊提出的,當時提出的初衷是為了計算機/電子類方向的學生做課程實踐服務的。由于這是伯克利大學研究并流片的第五代RISC架構處理器,因此就命名為RISC-V

2023-09-28 11:58:35

本帖最后由 余一yui 于 2023-4-26 10:44 編輯

《玄鐵RISC-V處理器入門與實戰》是一本介紹開源ISA(指令集架構)RISC-V的電子書。RISC-V是由加州大學伯克利分校

2023-04-12 11:16:58

10月19日,在2021云棲大會上,阿里云智能總裁張建鋒宣布,平頭哥開源玄鐵RISC-V系列處理器,并開放系列工具及系統軟件。這是系列處理器與基礎軟件的首次全棧開源,將推動RISC-V架構走向成熟

2021-10-20 14:09:00

https://github.com/JiaoXianjun/XiangShan談到RISC-V,應該都會想到香山處理器。其經歷了幾代的演進,性能越來越高。采用Chisel Rocketchip框架,能夠方便的定制屬于你的RISC-V處理器。對此,你有什么看法?

2023-04-14 15:51:59

香山是什么2019 年,在中國科學院支持下,由 中國科學院計算技術研究所 牽頭發起 “香山” 高性能開源 RISC-V 處理器項目,研發出目前國際上性能最高的開源高性能 RISC-V 處理器核

2022-04-07 14:20:44

自從UltraSoC去年發布其RISC-V跟蹤解決方案后,吸引了更多的處理器供應商,在眾多企業的合作下,各方面的系統都有了很大的進展。據報道,近日UltraSoC宣布界首款RISC-V處理器跟蹤IP產品開始全面供貨。

2018-02-03 11:01:06 1216

1216 日前消息 目前全新的RISC-V處理器架構已經得到了更多廠商的支持

2018-04-03 14:23:01 6909

6909 VaaS形式化驗證平臺,采用了多種形式化驗證方法,具有驗證效率高、自動化程度高、人工參與度低、易于使用、支持多個合約開發語言、可支持大容量區塊鏈底層平臺的形式化驗證等優點。

2018-12-14 10:18:25 1555

1555 晶心科技今天在其共同主持的RISC-V臺灣地區研討會上首度公開其32位A25MP和64位AX25MP RISC-V多核心處理器。

2019-05-23 09:25:20 3251

3251 領先的嵌入式分析技術開發商UltraSoC日前宣布:其RISC-V處理器跟蹤解決方案開始全面供貨,這是業界首款商用RISC-V處理器跟蹤IP產品,也是RISC-V生態系統中關鍵的推動性技術。

2019-12-05 14:24:31 1120

1120 大型技術公司已開始涉足RISC-V,該技術以免費標準代替了芯片設計過程中的關鍵專有技術。盡管RISC-V還處于初期階段,但利用RISC-V卻可能會創造出一批新的處理器,這些處理器可以與英特爾的產品進行競爭,還可以削弱Arm的授權業務。

2020-02-20 16:57:29 3615

3615 「我們非常興奮 SylixOS 在晶心科技 RISC-V 處理器平臺上的支持。」晶心科技技術長暨執行副總經理蘇泓萌博士表示,「結合翼輝信息在特定領域的經驗, 攜手推動晶心科技高質量 RISC-V 處理器往特定工業、航天、通信與軌道交通等領域邁進。」

2020-08-12 15:12:22 2241

2241 隨著這些年的發展,RISC-V的受重視程度與與日俱增。這主要因為它是免費的、靈活的,并且速度很快。這使RISC-V成為許多開發人員的安全便捷選擇。但是您會認為RISC-V是通用RISC處理器還是定制的隨心所欲處理器?

2020-11-17 16:11:56 4207

4207 近兩年,開源開放的RISC-V指令集架構成為行業新寵,諸多科技巨頭紛紛研發自己的RISC-V架構處理器。現在,硬盤巨頭希捷公布了基于RISC-V架構設計的兩款全新處理器,可加快數據中心和邊緣的實時

2020-12-09 15:11:13 2976

2976 對x86處理器來說,開源的RISC-V處理器威脅越來越大,它不僅能實現5GHz的超高頻率,現在多核并行上也甩開了x86,Esperanto公司已經實現了1000多核RISC-V處理器。

2020-12-10 09:23:12 2881

2881 對x86處理器來說,開源的RISC-V處理器威脅越來越大,它不僅能實現5GHz的超高頻率,現在多核并行上也甩開了x86,Esperanto公司已經實現了1000多核RISC-V處理器。

2020-12-10 14:12:32 1352

1352 晶心科技宣布全球業界首款RISC-V向量處理器核心AndesCore? NX27V升級支持最新RISC-V向量(RVV)擴展指令1.0版以及支持更多的配置以滿足不同市場的需求。

2021-04-12 10:01:58 3248

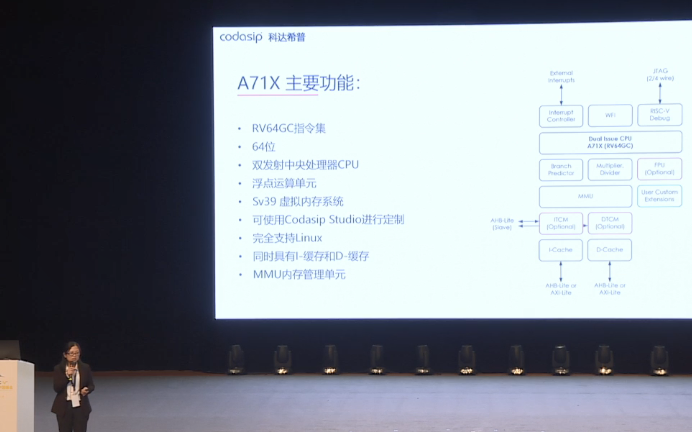

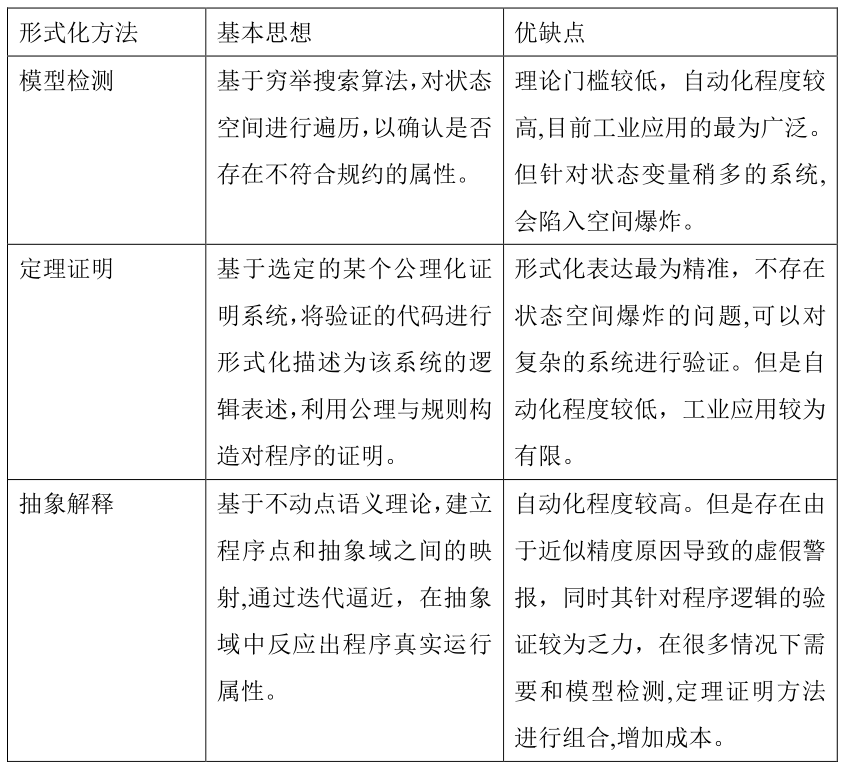

3248 在今天的第一屆RISC-V中國峰會上,科達希普在第一屆RISC-V中國峰會上發布RISC-V A71X應用處理器;并且與德國SEGGAR正式宣布圍繞RISC-V架構展開合作。

2021-06-22 11:29:02 1364

1364

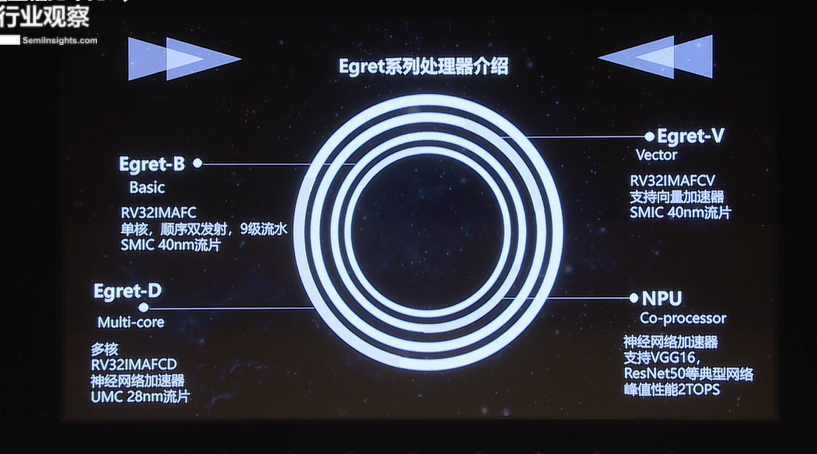

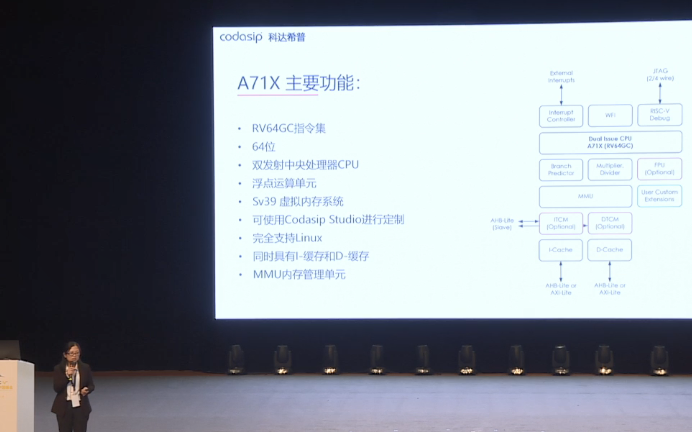

在risc-v峰會上由廈門半導體投資集團有限公司的王旭給我們介紹了基于RISC-V指令集的Egret系列處理器,分別從特性、應用場景、優勢等幾個方面對這個系列的處理器進行了詳細的展現。

2021-06-22 15:36:14 2699

2699

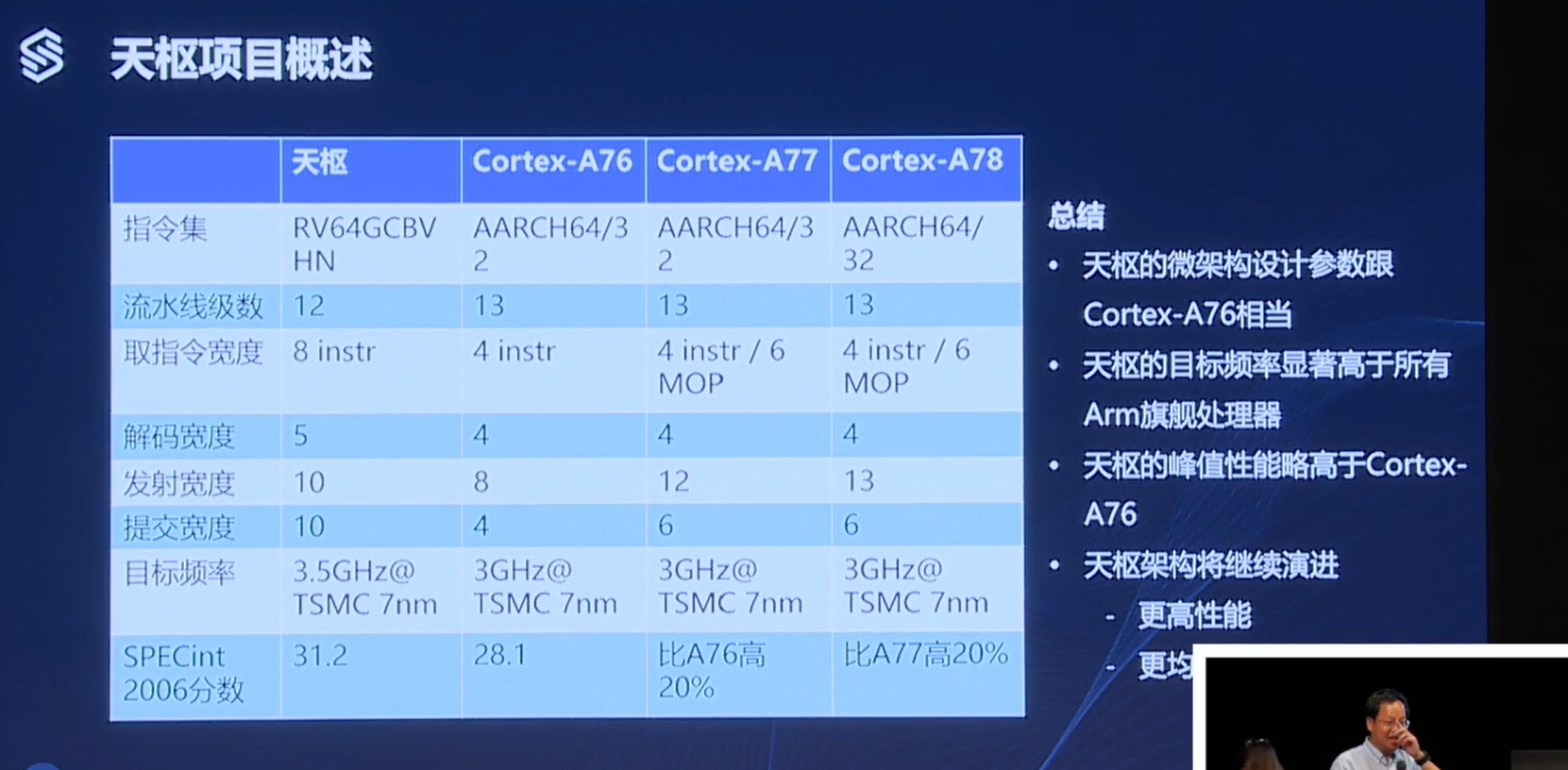

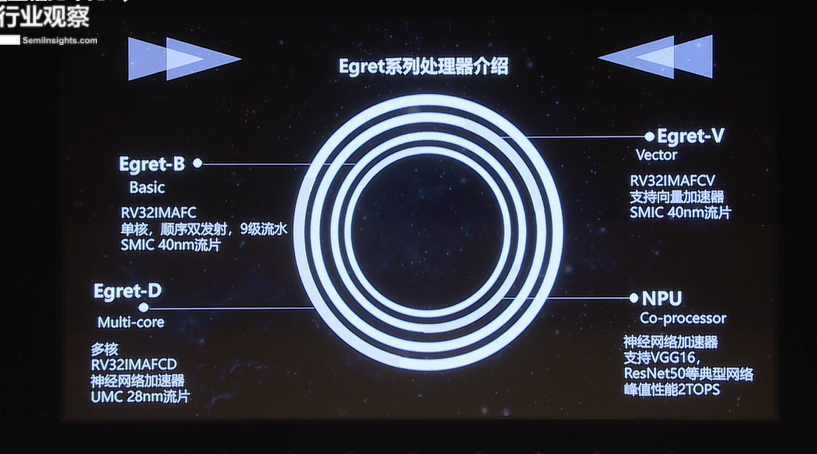

首屆risc-v峰會在上海正式舉辦,以下內容是賽昉科技天樞項目的介紹,分別從微架構、應用場景以及典型用法幾個方面分析這款高性能RISC-V處理器。

2021-06-22 17:36:34 3855

3855

RISC-V雖然指令集開源,但從處理器IP的研發角度,整個行業屬于浪費性競爭,這也嚴重制約著目前RISC-V高性能處理器從0到1的發展過程。

2021-10-19 14:06:58 1921

1921

10月19日,在2021云棲大會上,阿里云智能總裁張建鋒宣布,平頭哥開源玄鐵RISC-V系列處理器,并開放系列工具及系統軟件。這是系列處理器與基礎軟件的首次全棧開源,將推動RISC-V架構走向成熟

2021-12-08 16:21:07 14

14 芯來科技將正式采用芯華章自主研發的新一代智能驗證系統穹景 (GalaxPSS)及數字仿真器穹鼎 (GalaxSim)等系列EDA驗證產品,加速新一代復雜RISC-V處理器IP的設計研發。

2022-03-03 10:32:25 2269

2269 RISC-V是這兩年才開始迅速發展的,因此關于RISC-V的學習參考資料目前還很少,特別是適合入門的資料,因此學習起來進度很緩慢,于是萌生了自己從零開始寫RISC-V處理器核的想法。 本人是一名FPGA小白,為了快速入門、深入掌握RISC-V,我開始了學習FPGA和verilog的"艱難&am

2022-03-17 09:46:39 116

116 Imperas 產品組合以及來自快速發展的 RISC-V 生態系統的其他工具,為您今天開始自己的開放式處理器設計提供了足夠的資源。

2022-06-01 10:00:27 2296

2296

為了保護 IoT 應用程序,PUFsecurity 利用芯片指紋技術來強化信任根,并開發了 PUFiot,這是一種具有廣泛安全邊界的安全協處理器,可以輕松集成到安全的 RISC-V 系統中。

2022-06-01 11:06:19 4279

4279

電子發燒友網報道(文/周凱揚)無論是x86、Arm還是新秀RISC-V,大家談及基于這些架構的處理器時,除了對比性能、功耗以外,不免會說到造就當下處理器差異化的另一大因素,那就是制造工藝。臺積電、中

2022-06-30 16:33:25 3419

3419 盡管由于開源架構設計新的微處理器在經濟上是可行的,但測試和驗證仍然是主要障礙。 隨著 RISC-V 等開源處理器架構的出現,芯片設計變得越來越大眾化,越來越多的組織敢于涉足處理器設計,從嵌入式微控制器

2022-07-29 10:02:00 958

958

展開新的合作,共同加速基于SiFive RISC-V處理器的SoC設計和驗證。基于該合作,雙方客戶可采用新思科技Fusion QuickStart設計實現套件(QIKs),以優化SiFive

2022-11-09 18:33:37 1646

1646 Codasip通過收購Cerberus增強RISC-V處理器設計的安全性 RISC-V的安全性問題需要得到高度重視 德國慕尼黑市,2022年11月 - 處理器設計自動化和RISC-V處理器硅知識產權

2022-11-16 19:37:05 843

843 Workbench for RISC-V 新版本將支持 NOEL-V,即 Gaisler 的 RISC-V 太空級處理器。

2022-12-20 17:42:05 1808

1808 IAR Embedded Workbench 將支持 RISC-V 太空級處理器 NOEL-V 嵌入式開發軟件和服務的全球領導者 IAR Systems和 CAES 的容錯處理器設計中心

2022-12-23 17:15:52 2748

2748 自從RISC-V 2015年公開發布以來,它作為一種開放、協作和可擴展的微處理器獲得了大量關注。相比其它專有處理器架構,RISC-V確保任何人都可以使用該架構來促進工程和計算社區的開發和增長。

2023-01-06 10:58:01 1559

1559 得到了RISC-V基金會的認可,相關技術已與RISC-V生態完成適配。 目前 openEuler 已經推出了多個基于 openEuler 開發的 RISC-V 架構的發行版。未來,openEuler將繼續探索在 RISC-V 架構處理器上的更多可能。 ?

2023-03-13 18:40:19 1934

1934 處理器驗證是一個全新的領域。我們知道 Arm 和 Intel 對處理器質量的期望設置了很高的標準。在 RISC-V 中,我們必須嘗試并遵循這一點。

2023-03-22 15:19:32 1002

1002 首選。據估計,在未來五年內仿真將逐漸被取代,僅用于子系統和系統級驗證。與此同時,形式化驗證方法已經開始處理一些系統級任務,隨著技術的不斷創新,形式化驗證將逐步開始處理更多系統級任務。 形式化驗證的普及 近五年來,更多機構和設計驗

2023-04-21 19:35:05 1240

1240

轉型RISC-V,大家才發現處理器驗證絕非易事。新標準由于其新穎和靈活性而帶來的新功能會在無意中產生規范和設計漏洞,因此處理器驗證是處理器開發過程中一項非常重要的環節。

2023-06-01 09:07:01 1193

1193

隨著RISC-V處理器的快速發展,如何保證其正確性成為了一個重要的問題。傳統的測試方法只能覆蓋一部分錯誤情況,而且無法完全保證處理器的正確性。因此,基于形式驗證的方法成為了一個非常有前途的方法,可以更加全面地驗證處理器的正確性。本文將介紹一種基于形式驗證的高效RISC-V處理器驗證方法。

2023-06-02 10:35:17 2127

2127 的客戶現在可以根據同一授權協議和合同去購買一系列精選的SmartDV外設IP的授權。這一合作伙伴關系支持使用Codasip RISC-V處理器的芯片設計人員,通過使用已驗證過兼容性和集成便捷性等特性

2023-07-03 16:13:04 1320

1320 在本文中,我們將以西門子EDA處理器驗證應用程序為例,結合Codasip L31這款廣受歡迎的RISC-V處理器IP提供的特性,來介紹一種利用先進的EDA工具,在實際設計工作中對處理器進行驗證的具體方法。

2023-07-10 10:28:41 1129

1129

RISC-V的開放性允許定制和擴展基于 RISC-V 內核的架構和微架構,以滿足特定需求。這種對設計自由的渴望也正在將驗證部分的職責轉移到不斷壯大的開發人員社群。然而,隨著越來越多的企業和開發人員轉型RISC-V,大家才發現處理器驗證絕非易事。

2023-07-10 09:42:08 1469

1469

2023年10月19日, 思爾芯(S2C) 宣布 北京開源芯片研究院(簡稱“開芯院”) 在其歷代“香山” RISC-V 處理器開發中采用了思爾芯的 芯神瞳 VU19P 原型驗證系統

2023-10-24 16:28:17 1500

1500 近年來,基于RISC-V架構的處理器逐漸嶄露頭角,引起了業內的廣泛關注。其中,由國人主導的“香山”RISC-V處理器備受關注。

2023-10-25 09:20:42 1798

1798 2023年10月19日,思爾芯(S2C)宣布北京開源芯片研究院(簡稱“開芯院”)在其歷代“香山”RISC-V處理器開發中采用了思爾芯的芯神瞳VU19P原型驗證系統,不僅加速了產品迭代,還助力多家企業

2023-10-25 08:24:04 1099

1099

新思科技全新32位和64位ARC-V處理器IP建立在其數十年的處理器開發經驗之上,為設計者提供更廣泛的RISC-V IP選擇空間

2023-11-10 12:50:33 1343

1343 systems建立合作伙伴關系。此次合作旨在協助開發人員利用功能安全認證處理器核 AndesCore N25F-SE和D25F-SE等RISC-V技術創建安全關鍵型解決方案。

2023-12-13 10:10:21 1452

1452 本土RISC-V CPU IP領軍企業——芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案,提供專業有效的信息安全保護以及加解密功能。

2024-03-11 11:01:21 2700

2700

FPGA(現場可編程門陣列)和RISC-V處理器在多個方面存在顯著的區別。

2024-03-27 14:21:11 2498

2498 RISC-V 是一個開放的 ISA,任何人都可以接受它并實現處理器。但RISC-V市場的領導者知道,僅僅因為他們不需要支付許可使用費,并不意味著RISC-V是便宜的選擇。

2024-04-15 11:34:17 1516

1516

專注于加速數據分析和生成式AI工作負載的RISC-V主要會員公司Rivos與32/64位RISC-V處理器內核的領先供貨商、RISC-V創始會員Andes晶心科技,宣布Rivos已獲得Andes晶心NX45 RISC-V處理器的授權,用于其產品中的關鍵控制功能。

2024-12-04 10:37:17 1245

1245 Andes晶心科技(TWSE:6533; SIN US03420C2089; ISIN:US03420C1099)是全球高效能、低功耗 32/64 位 RISC-V 處理器的領導廠商,也是

2024-12-26 10:54:03 1617

1617 引言RISC-V架構以其開放性和高度可定制的特性,正在重塑處理器設計格局。然而,這種靈活性也帶來了顯著的驗證挑戰,使其驗證復雜度遠超傳統固定架構處理器。RISC-V的驗證難點主要體現在四個方面:首先

2025-09-18 10:08:39 1910

1910

電子發燒友App

電子發燒友App

評論