2023年10月19日,思爾芯(S2C)宣布北京開源芯片研究院(簡稱“開芯院”)在其歷代“香山” RISC-V 處理器開發中采用了思爾芯的芯神瞳 VU19P 原型驗證系統,不僅加速了產品迭代,還助力多家企業基于“香山”開發各種高端芯片。

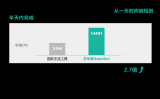

RISC-V,作為一種開放的指令集架構,已逐漸成為全球處理器開發的焦點。其中,“香山”被視為 RISC-V 的國際領先代表,是一款開源高性能RISC-V 處理器核。自 2019 年項目發布一代“雁棲湖”以來,在 GitHub 這一全球最大的開源項目托管平臺上,其獲得了超過 4000 個星標(Star)和 551 個分支(Fork),成為國際上最受關注的開源硬件項目之一。迄今為止,“香山”已經成功推出了兩代產品,第三代“昆明湖”正在研發中。其中,二代“南湖”采用了 14nm 制程技術。其核心頻率高達 2 GHz,并獲得了 10/GHz 的 SPECCPU 2006 評分,綜合性能還超越了 Arm 的 Cortex-A76。已有 18 家業界領軍企業正在基于“香山”核進行聯合研發,推動高端芯片的示范應用,以此加速 RISC-V 生態的建設和發展。

為推進“香山”項目,思爾芯提供了芯神瞳 VU19P 原型驗證系統,一個可以在真實硬件上測試軟件功能和性能的平臺,使“香山”的軟硬件工程師能夠并行工作,顯著加速進程。這一系統兼具靈活性和擴展性,滿足各種設計和應用要求。開芯院補充道:“由于 RISC-V 的多樣化,客戶在選擇時要對不同的 RISC-V 核心進行評估。思爾芯的系統使我們能有效展現處理器性能,順利完成 SPEC 跑分、IO 驗證及 BSP 驅動開發等工作,覆蓋了從硬件設計到軟件集成的全生命周期。方便我們的客戶選擇最適合的方案,并助推基于‘香山’核的后續聯合研發。” 圖為香山(南湖架構)在芯神瞳 VU19P 原型驗證系統上演示

圖為香山(南湖架構)在芯神瞳 VU19P 原型驗證系統上演示

1. SPEC 跑分驗證:

在硬件設計中,一旦有了原型或早期版本的設計,就可以使用 SPEC 基準測試進行跑分,從而驗證預期的性能是否得到實現。基于思爾芯的芯神瞳,“香山”團隊運行了 SPEC 基準測試,通過結合顯卡運行 Linux 和圖形界面,以直觀地評估其性能。這為團隊提供了寶貴的反饋,可以據此進行優化以達到或超過預期的性能標準。目前,第二代“香山”(南湖架構)的 SPEC2006 得分為20分,超越了 2018 年的 Arm Cortex-A76。

2. IO 驗證:

IO(輸入/輸出)驗證是確保芯片與外部環境(如其他芯片、系統等)之間的通信是正確的和高效的過程。思爾芯的芯神瞳便為“香山”提供了一個實際的環境,用于測試和驗證所有輸入/輸出通信通道。這確保了“香山”與其他硬件組件,如內存、存儲和其他接口的完美集成和通信。在整個驗證系統的搭建中,“香山”團隊使用了思爾芯的 PPM、GMAC、PCIe 等子卡和接口,系統整體運行速率為 50MHz,各接口按照它們各自的標準頻率與“香山”系統進行了對接。

3. BSP驅動開發:

BSP(Board Support Package)驅動開發是確保軟硬件順暢交互的關鍵橋梁。利用原型驗證技術,開發者可以直接在真實硬件上進行 BSP 的開發和測試,保證軟硬件的緊密協同,從而提高開發效率和準確性。隨著“香山”處理器的硬件設計在思爾芯原型驗證系統上穩定實現,其軟件團隊立即展開了 BSP 驅動開發。這不僅讓軟硬件團隊實現了并行開發,而且確保軟件在真實硬件環境中得以優化。這種早期介入策略讓軟件團隊更深入地了解硬件特性和限制,為“香山”在最終流片前確保硬件設計并加速軟件開發奠定了基礎。

“香山”無疑是國際領先的高性能 RISC-V 處理器核。為保持這一地位,選擇合適的合作伙伴對至關重要。開芯院表示:“思爾芯的原型驗證系統無疑為我們香山項目的成功奠定了堅實的基礎。之所以選擇思爾芯,因為我們充分認可他們卓越的技術和服務:技術穩定持久,服務響應速度快,產品經過長時間驗證,穩定且成熟。這為我們的項目注入了巨大的推動力。”

思爾芯副總裁陳英仁先生對此也表示:“我們非常高興看到香山成功地應用了我們的‘芯神瞳’,加速了產品的迭代,并滿足了廣泛的目標市場需求。未來,我們將繼續與開芯院緊密合作,共同致力于擴大 RISC-V 社區,為推動 RISC-V 生態的繁榮和前景不懈努力。”

關于北京開源芯片研究院

近年來,RISC-V 快速發展,已經成為當前國際科技競爭的焦點。為提升我國集成電路設計水平,建設與國際開源社區對接的技術平臺,北京市和中科院高度重視 RISC-V 發展,組織國內一批行業龍頭企業和頂尖科研單位于 2021年12月6日發起成立北京開源芯片研究院。研究院以開源開放凝聚產業發展共識,以協同創新激發應用牽引潛力,著力推進 RISC-V 創新鏈和產業鏈的加速融合,加速科技創新成果產業化落地,加快打造全球領先的 RISC-V 產業生態。

關于思爾芯 S2C

思爾芯(S2C)自2004年設立上海總部以來始終專注于集成電路 EDA 領域。作為業內知名的 EDA 解決方案專家,公司業務已覆蓋架構設計、軟件仿真、硬件仿真、原型驗證、EDA 云等工具與服務。已與超過 600 家國內外企業建立了良好的合作關系,服務于人工智能、高性能計算、圖像處理、數據存儲、信號處理等數字電路設計功能的實現,廣泛應用于物聯網、云計算、5G 通信、智慧醫療、汽車電子等終端領域。

-

處理器

+關注

關注

68文章

20250瀏覽量

252212 -

RISC-V

+關注

關注

48文章

2887瀏覽量

52941 -

思爾芯

+關注

關注

0文章

150瀏覽量

1721

發布評論請先 登錄

思爾芯、MachineWare與Andes晶心科技聯合推出RISC-V協同仿真方案,加速芯片開發

開放協作,共筑生態——思爾芯參與上海開放處理器產業創新中心開業儀式暨RISC-V專利聯盟專利池入池儀式

開芯院采用芯華章高性能數字仿真器GalaxSim,RISC-V 驗證獲近3倍效率提升

直播預約 |開源芯片系列講座第30期:“一生一芯”計劃——從零開始設計自己的RISC-V處理器芯片

硬核加速,軟硬協同!混合仿真賦能RISC-V芯片敏捷開發

芯華章RISC-V敏捷驗證方案再升級

2025 RISC-V中國峰會|思爾芯以數字EDA賦能產業生態,加速商業創新

睿思芯科攜靈羽處理器亮相2025 RISC-V中國峰會

開芯院采用芯華章P2E硬件驗證平臺加速RISC-V驗證

思爾芯攜手Andes晶心科技,加速先進RISC-V 芯片開發

思爾芯與玄鐵合作IP評測,加速RISC-V生態發展

思爾芯原型驗證助力香山RISC-V處理器迭代加速

思爾芯原型驗證助力香山RISC-V處理器迭代加速

評論