JESD204B 同步時鐘。此設計可提供多通道 JESD204B 時鐘,采用 TI LMK04828 時鐘抖動清除器和帶有集成式 VCO 的 LMX2594 寬帶 PLL,能夠實現低于 10ps 的時鐘間偏差。此

2018-10-15 15:09:38

你好:LMK04828 spi 回讀不通。配置寄存器情況以及抓取的情況如下圖:

0x0000 0x90

0x0000 0x00

0x0149 0x02

回讀0x0149 寄存器,結果為0xff。結果圖下圖,感覺sdio不能拉低。謝謝

2024-11-12 08:23:41

因為lmk04828一個寄存器是24bit,而spi控制器只支持16/8bit,我一次性傳輸發現沒有反應。手冊只顯示了單個寄存器的順序圖,是否代表不能實現這種傳輸

2024-11-11 08:01:56

= lmk04828_SPI_readReg(0x1FFF53);

lmk04828_SPI_WriteReg (0x000306); data = lmk04828_SPI_readReg(0x000306);

我按照如上寄存器配置對芯片進行配置,芯片沒有時鐘信號輸出

2024-11-11 06:14:04

EVAL BOARD FOR LMK04828

2023-03-29 22:53:42

請問LMK04828SNKDTEPEP 這個和LMK04828BISQ這個 是不是就是溫度的區別,使用都是一樣的,看資料里面沒有太明顯差異,簡單說是否可以在原來使用LMK04828BISQ的板子上直接焊接LMK04828SNKDTEP。謝謝。

2024-11-12 07:24:13

我使用LMK04828產生jesd204b需要的時鐘,輸入clkin0 = 150MHz,需要產生150MHz DCLK和10MHz SDCLK,分別使用了Dual-Loop Mode

2024-11-13 06:01:30

參考adc12dl3200evm設計的,晶振輸入幅值和adc12dl3200evm的晶振基本一樣,但lmk04828的時鐘輸出幅值只有20mv.

2024-11-12 08:14:27

你好:將LMK04828配置為 0-delay模式,oscin 時鐘輸入,采用single loop mode,只配置PLL2 0-delay模式,沒有配置成功。

有沒有相關例程,配置如下圖:

2024-11-13 06:30:56

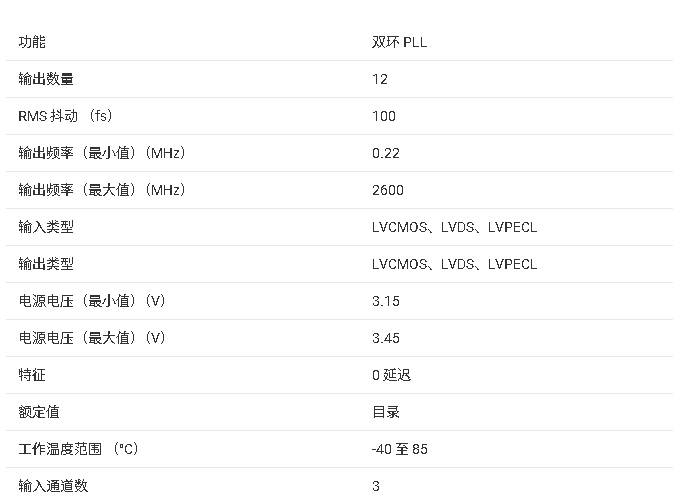

`LMK04832-SP是具有JEDEC JESD204B支持的高性能時鐘調節器,適用于太空應用。可以將PLL2的14個時鐘輸出配置為使用器件和SYSREF時鐘來驅動七個JESD204B轉換器或其他

2021-03-24 16:13:02

我們目前使用的lmk04828芯片,芯片在正常工作的情況下RESET/GPO管腳是高電平還是低電平?

我們外部是否需要對此RESET/GPO管腳控制。

RESET/GPO管腳僅作為復位管腳。無其他復用功能

2024-11-08 07:20:41

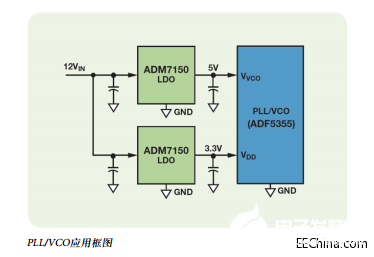

超低噪聲調節器是怎樣為VCO和PLL供電的

2021-04-06 08:05:27

。EVM上包括LMX2581時鐘合成器和LMK04828 JESD204B時鐘生成器,可以配置為為完整的JESD204B子類1時鐘解決方案提供超低抖動ADC設備時鐘和SYSREF。ADC12J2700

2020-04-09 09:44:08

ADS 2011.10版本無法加載lmk04828 IBIS模型

2024-11-13 07:06:09

簡化高速數據鏈路- 典型應用:5G射頻單元、衛星通信2. LMK04828(時鐘發生器+DDS)- 亮點:- 集成低噪聲PLL和DDS,實現靈活時鐘合成- 相位同步精度<1ps- 適用于

2025-08-08 09:53:07

LD39150DT33-R DPAK超低壓BiCMOS電壓調節器的典型應用。 LD39150是一款快速超低壓降線性穩壓器,采用2.5至6 V輸入電源供電。提供多種輸出選項。低壓降,低噪聲和超低靜態

2019-05-21 09:18:33

嗨,我們使用ZC706板來控制TI時鐘調節器IC。ZC706中的FPGA為XC7Z045FFG900,時鐘調節器為LMK03200。我們使用HR Bank IO(輸出)之一來控制LMK

2020-07-28 09:02:25

我們最近在使用LMK04828芯片的時候遇見了這樣的問題:

使用場景,使用了控制芯片為zynq 7045 的SPI xai ip做的控制,使用SPI四線模式來完成讀寫,使用管腳(MISO)為

2024-11-08 07:11:59

我們在使用LMK04828配置完成后,將相應信息配置到芯片后未完成鎖屏,鎖屏狀態未上拉,下面是我們的配置,能幫我看看是什么地方配置出現了問題嗎?

配置一:

配置二:

配置三:

、

謝謝!!!!!!!

2024-11-08 06:32:59

在使用ADC 3000 GUI配置 adc34jxx 的LMK04828時鐘芯片時候遇到了無法產生sysref 信號的問題:

設定了sysref deivider 后,在sysref

2025-01-02 07:04:22

使用SPI接口讀寫LMK04828 沒有任何反應,上電后測試第4組DCLKOUT有315MHz時鐘輸出,OSCin有122.88MHz時鐘輸出。目前SPI無法配置LMK04828導致項目無法往下走

2024-11-13 07:52:24

在datasheet上看到LMK04828支持LCPECL,請問什么是LCPECL,LCPECL和LVPECL的區別是什么呢?

2024-11-12 06:42:35

NCV8703 300 mA,超低靜態電流,IQ 12 A,超低噪聲,LDO電壓調節器的典型應用。 NCV8703是一款低噪聲,低功耗和低壓差線性穩壓器

2020-07-26 19:03:49

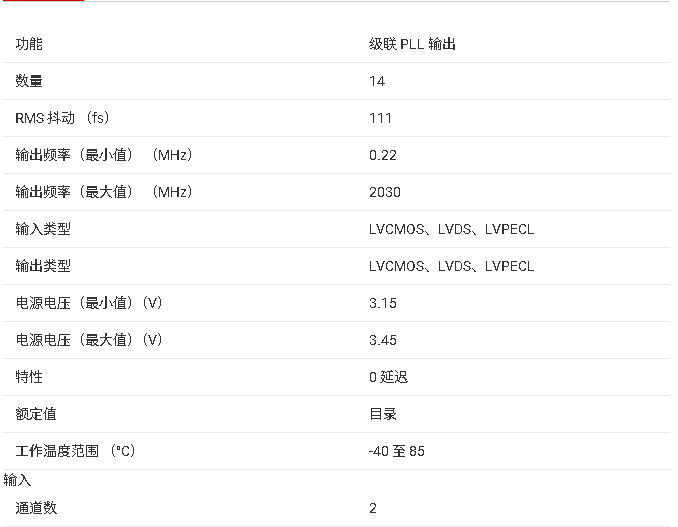

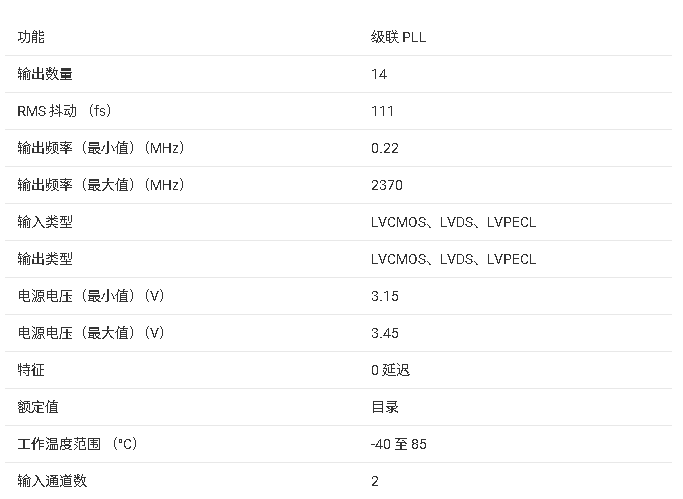

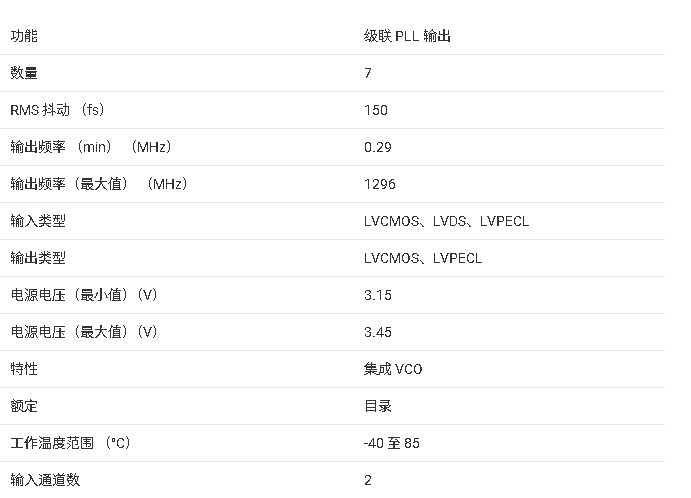

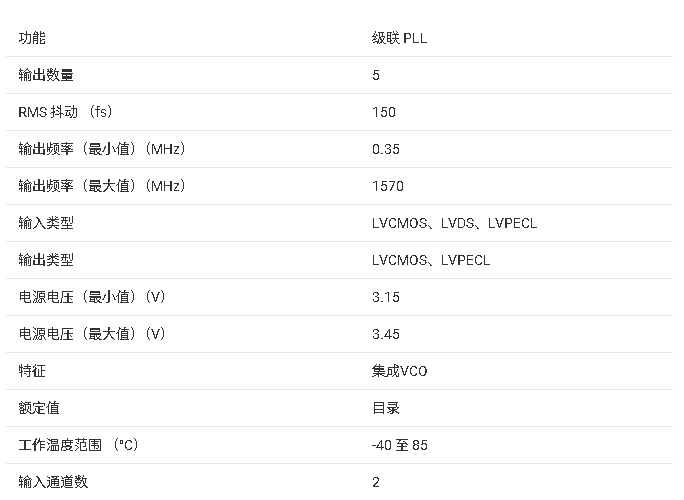

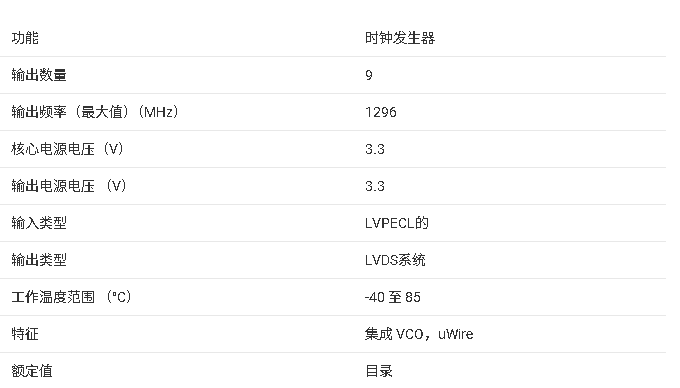

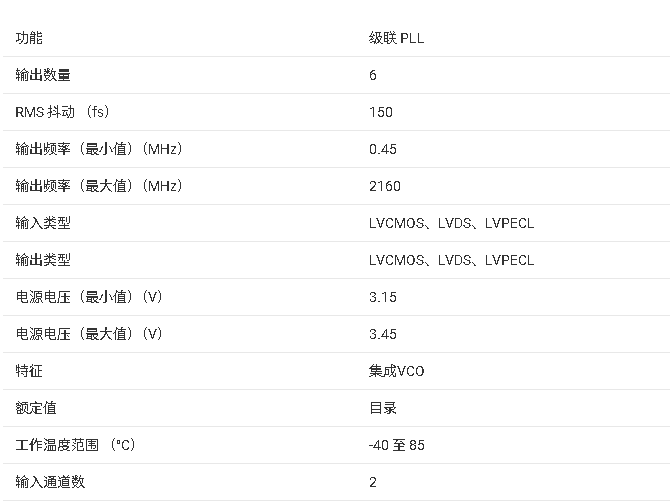

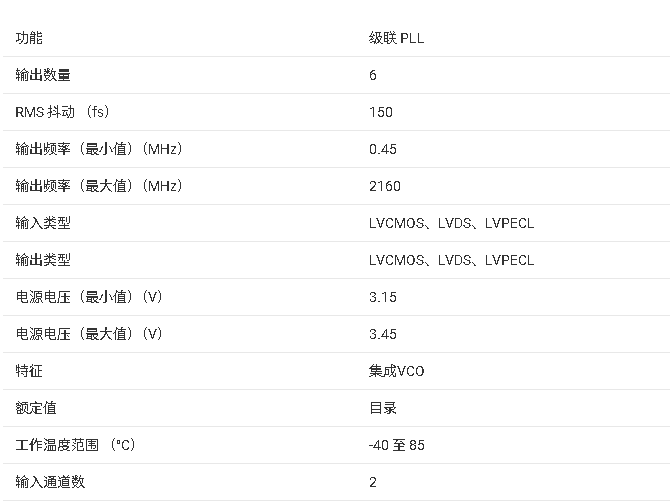

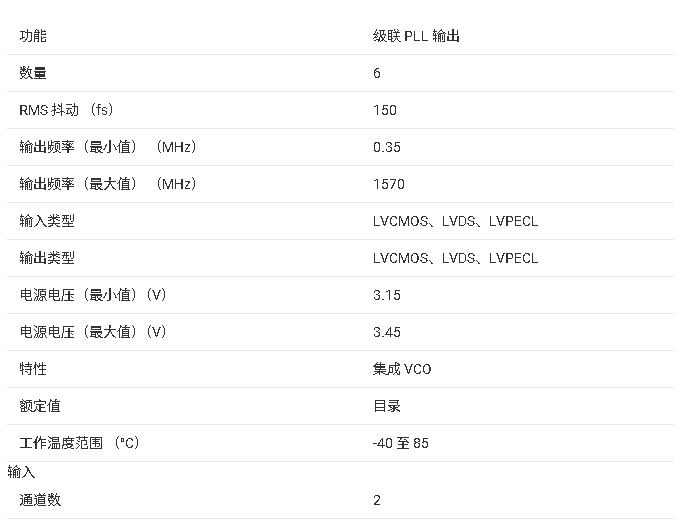

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

的差分時鐘。但是這對于ADS54J42EVM上122.88Mhz晶振時鐘來說有些難以產生。請問有方法正確配置LMK04828產生我需要的芯片嗎?如果可以的話,希望有供ADS54Jxx GUI軟件使用的.cfg文件。感謝!

2024-11-14 07:12:54

我們有多顆LMK04828需要做到輸出所有時鐘的相位穩定,用于后級RFSOC-AD/DA同步。

多片LMK04828輸入為Buffer芯片扇出的多路100MHz時鐘信號(該信號頻率可調節)和經

2024-11-08 16:09:38

請教一下各位大佬,我在使用lmk04828 DCLKX模擬延遲功能時,發現在該功能下時鐘輸出不穩定。我的配置如下:

1)DCLKx輸出時鐘2.56GHz,電平為LVPECL16

2)VCO設置

2024-11-12 06:35:01

您好,我想要用輸出4路時鐘,請問可以用ADC32RFXX EVM GUI界面能直接調出LMK04828輸出的4路時鐘嗎

2024-11-12 07:30:06

您好,請問通過ADC32RF42 EVM GUI 能直接配置出lmk04828的14路時鐘嗎?如果直接可以,請問我要怎么配置,我試過很多種配置都行不通。

2024-11-22 09:54:32

多通道 JESD204B 時鐘,采用 TI LMK04828 時鐘抖動清除器和帶有集成式 VCO 的 LMX2594 寬帶 PLL,能夠實現低于 10ps 的時鐘間偏斜。此設計經過 TI

2018-12-28 11:54:19

????????? ????低噪聲ldo電壓調節器SPX3819SPX3819? 是一個正電壓調節器,具有低退出電壓和低噪聲輸出功能。另外,該設備提供一個低電流800微米,100MA輸出

2018-05-11 16:19:04 5105

5105

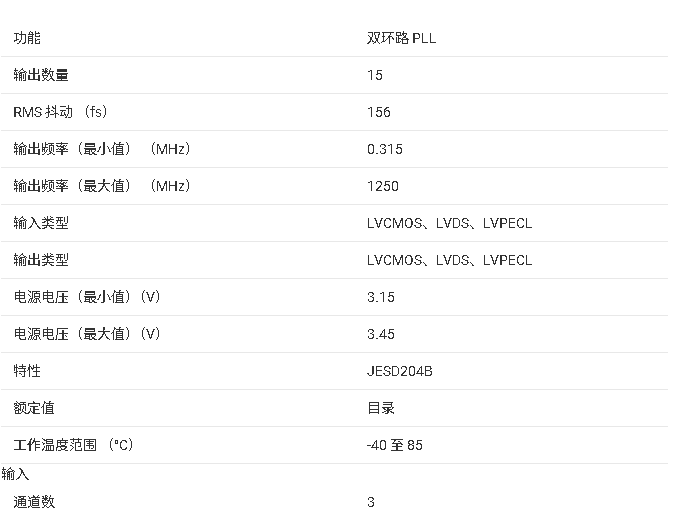

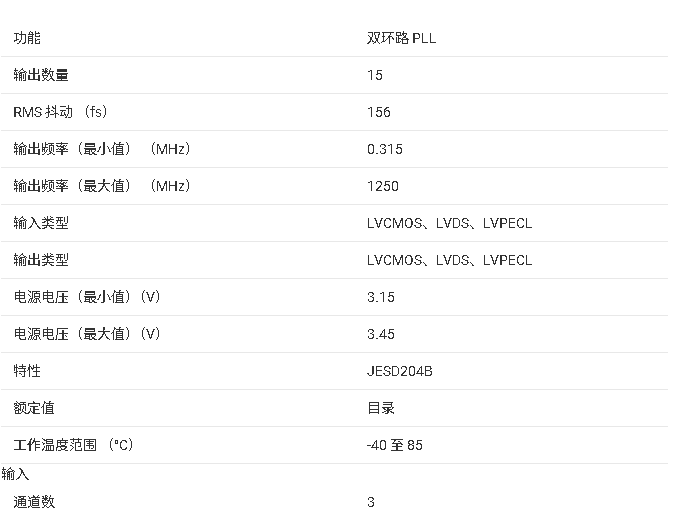

ADS42JB69EVM包括LMK048 28抖動清除時鐘解決方案。該應用筆記提供了EVM的不同時鐘配置的概述,并演示了如何在使用LMK04828對ADS42JB9計時時獲得最佳的信噪比(SNR)。LMK048 28是一個雙環鎖相環和頻率合成器,支持JESD204B接口。

2018-05-16 17:41:16 63

63

LT3042 是一款高性能低壓差線性穩壓器,其采用 LTC 的超低噪聲和超高 PSRR 架構以為對噪聲敏感的 RF 應用供電。LT3042 被設計為后隨一個高性能電壓緩沖器的高精度電流基準,其可容易地通過并聯以進一步降低噪聲、增加輸出電流和在 PCB 上散播熱量。

2018-06-29 19:18:51 1445

1445 具有可編程電流limit_zh的低噪聲軌到軌負調節器

2019-08-14 06:08:00 3678

3678 電子發燒友網為你提供TI(TI)LMK04828相關產品參數、數據手冊,更有LMK04828的引腳圖、接線圖、封裝手冊、中文資料、英文資料,LMK04828真值表,LMK04828管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-04-18 22:48:10

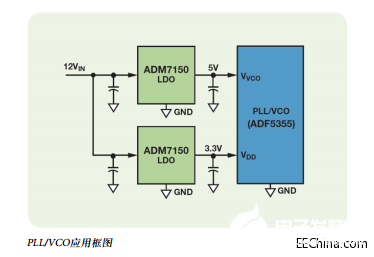

該12 V系統軌由感應開關元件生成,該元件會在軌上引起波紋和噪聲。為了獲得干凈的供電軌,需要超低噪聲調節器來生成5 V供電軌,為寬帶PLL和VCO供電。在5 V供電軌上出現的任何噪聲或波紋都會使PLL或VCO性能下降。

2021-03-15 15:35:10 2584

2584

ADP150:超低噪聲、150mA CMOS線性調節器

2021-03-18 20:59:46 1

1 ADP151:超低噪聲、200 mA CMOS線性調節器

2021-03-18 21:06:49 8

8 ADP320:三倍、200 mA、低噪聲、高電源抑制比電壓調節器

2021-04-17 10:42:33 11

11 ADP1765:5 A,低VIN,低噪聲,CMOS線性調節器數據表

2021-05-07 16:32:15 9

9 UG-811:評估ADP7159超低噪聲、2A、輸出可調、RF線性調節器

2021-05-10 13:11:53 9

9 LTC1682:帶低噪聲線性調節器的倍增電荷泵數據表

2021-05-20 14:22:19 7

7 本電路利用低噪聲、低壓差(LDO)線性調節器為寬帶集成PLL和VCO供電。寬帶壓控振蕩器(VCO)可能對電源噪聲較為敏感,因此,為實現最佳性能,建議使用超低噪聲調節器。圖1所示電路使用完全集成的小數

2021-06-06 11:25:50 2

2 LMK0482X系列是德州儀器推出的高性能時鐘調節芯片系列,該芯片目前有三種,分別為LMK04821、LMK04826以及LMK04828,該系列芯片都支持最新的JESD204B協議。本次調試主要以LMK04821為例,對調試過程中出現的一些問題進行總結說明。

2023-01-05 11:03:25 2165

2165 LT1964是一款微功率低噪聲、低壓差負調節器。能夠提供200mA的輸出電流,壓降為340mV。低靜態電流(30μA工作和3μA停機)使LT1964調節器成為電池供電應用的選擇。并且靜態電流在跌落時得到很好的控制。

2023-06-20 11:36:22 2506

2506

? 全芯時代,國產好芯不定期推薦。今日為大家介紹一款國產超低噪聲時鐘調節器,pin to pin替代TI的LMK04828 一、概述 該芯片是高性能時鐘調節器,支持JEDEC JESD204B。當

2023-06-25 10:15:26 1404

1404 高性價比的時鐘解決方案——SC6301,兼容LMK04828

2024-04-12 10:06:24 1574

1574

電子發燒友網站提供《低噪聲開關電容升壓調節器LM2750數據表.pdf》資料免費下載

2024-04-19 09:45:43 0

0 電子發燒友網站提供《LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-20 10:37:26 0

0 電子發燒友網站提供《LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-20 10:39:30 0

0 電子發燒友網站提供《LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-20 09:52:49 0

0 電子發燒友網站提供《LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-20 09:32:15 0

0 電子發燒友網站提供《LMK04828-EP時鐘調節器數據表.pdf》資料免費下載

2024-08-20 09:11:58 0

0 電子發燒友網站提供《LMK03200系列精密延遲時鐘調節器數據表.pdf》資料免費下載

2024-08-21 10:27:05 0

0 電子發燒友網站提供《LMK02000集成PLL的精密時鐘調節器數據表.pdf》資料免費下載

2024-08-21 10:29:42 0

0 電子發燒友網站提供《LMK04000系列低噪聲時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-21 09:56:12 0

0 電子發燒友網站提供《LMK02002精密時鐘調節器數據表.pdf》資料免費下載

2024-08-21 09:54:42 0

0 電子發燒友網站提供《LMK03002/LMK03002C精密時鐘調節器數據表.pdf》資料免費下載

2024-08-21 09:59:07 0

0 電子發燒友網站提供《LMK03000系列精密時鐘調節器數據表.pdf》資料免費下載

2024-08-21 09:57:08 0

0 電子發燒友網站提供《LMK03318超低噪聲抖動時鐘發生器系列數據表.pdf》資料免費下載

2024-08-21 09:53:40 0

0 電子發燒友網站提供《LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-21 09:19:01 1

1 電子發燒友網站提供《帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-21 09:20:21 0

0 電子發燒友網站提供《LMK04906帶6路可編程輸出的,超低噪聲時鐘抖動清除器和乘法器數據表.pdf》資料免費下載

2024-08-21 09:21:31 0

0 電子發燒友網站提供《具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表.pdf》資料免費下載

2024-08-21 09:12:01 0

0 電子發燒友網站提供《LMK04208具有雙環PLL的低噪聲時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-22 11:22:10 0

0 電子發燒友網站提供《LMK04816具有雙環PLL的三輸入低噪聲時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-22 12:21:23 0

0 電子發燒友網站提供《LMK0480x低噪聲時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-22 11:16:04 0

0 電子發燒友網站提供《LMK04616超低噪聲和低功耗時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-22 11:42:40 0

0 電子發燒友網站提供《LMK04610超低噪聲和低功耗時鐘抖動消除器數據表.pdf》資料免費下載

2024-08-22 10:11:59 2

2 對于數據處理速率與準確度需求較高,且功能較多、信息交互復雜的應用場景,往往需要時鐘芯片的存在,如通訊基站、交換機、數據中心服務器、汽車、工業控制等。今天給大家推薦一款國產時鐘芯片,可完全替代TI的LMK04828。

2024-09-14 15:03:49 2681

2681 電子發燒友網站提供《LMK04828作為ADS42JB69的時鐘源.pdf》資料免費下載

2024-10-17 09:22:58 2

2 隨著現代電子系統對高精度、高可靠性時鐘信號需求的不斷提升,時鐘抖動成為影響系統性能的關鍵因素。核芯互聯科技有限公司重磅推出CLF04828超低噪聲去抖時鐘,憑借其領先的雙PLL架構、超低相位噪聲和靈活的輸出配置,為多領域高性能應用提供了強大的技術支持。

2025-03-04 12:38:02 1465

1465

LMK04714-Q1 是一款高性能時鐘調節器,支持 JEDEC JESD204B/C,適用于太空應用。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個

2025-09-11 10:07:11 560

560

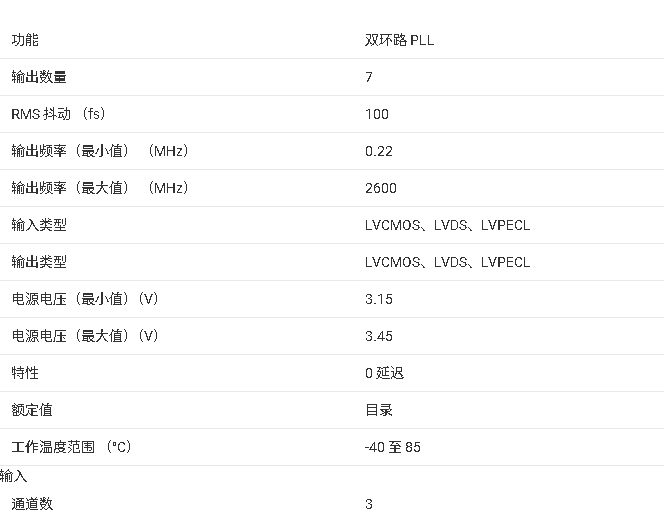

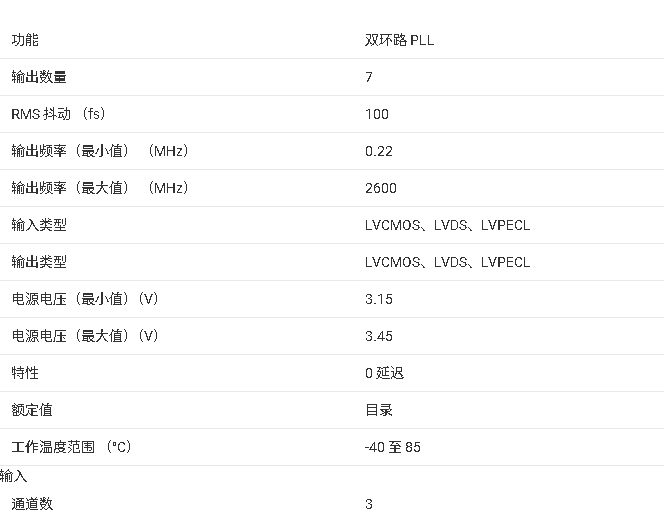

LMK04228 器件是業界高性能時鐘調節器,支持 JEDEC JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個JESD204B轉換器或其他邏輯器件

2025-09-12 15:02:13 613

613

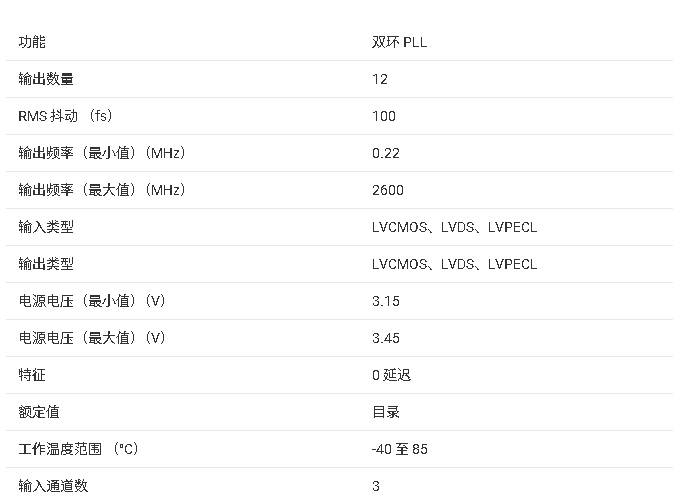

LMK04828-EP 器件是業界性能最高的時鐘調理器,支持 JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個JESD204B轉換器或其他邏輯器件

2025-09-12 16:13:11 832

832

LMK04208是一款高性能時鐘調節器,具有卓越的時鐘抖動清除功能, 生成和分發具有高級功能,以滿足下一代系統要求。 雙環路PLLatinum?架構能夠 使用低噪聲VCXO模塊的RMS抖動(12

2025-09-13 10:16:27 1116

1116

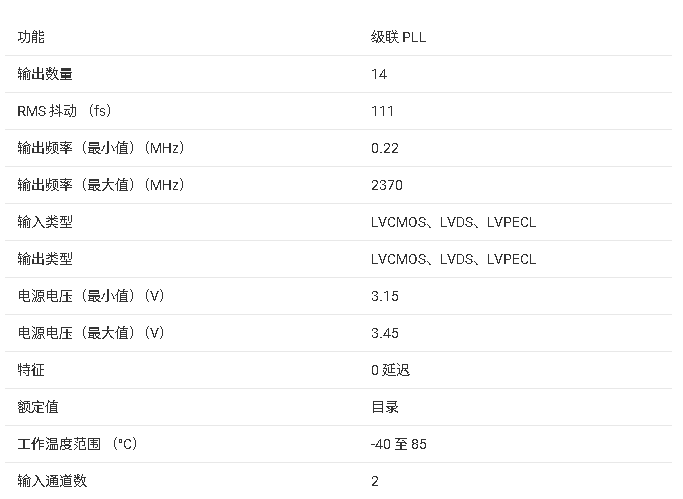

LMK0482x 系列是業界性能最高的時鐘調節器,支持 JEDEC JESD204B。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 7 個 JESD204B

2025-09-15 10:10:11 848

848

該LMK04906是業界性能最高的時鐘抖動衰減器,具有卓越的時鐘抖動清除、生成和分配功能,具有先進的功能,可滿足高性能時序應用需求。

該LMK04906接受 3 個 1 kHz 至 500

2025-09-15 11:13:27 668

668

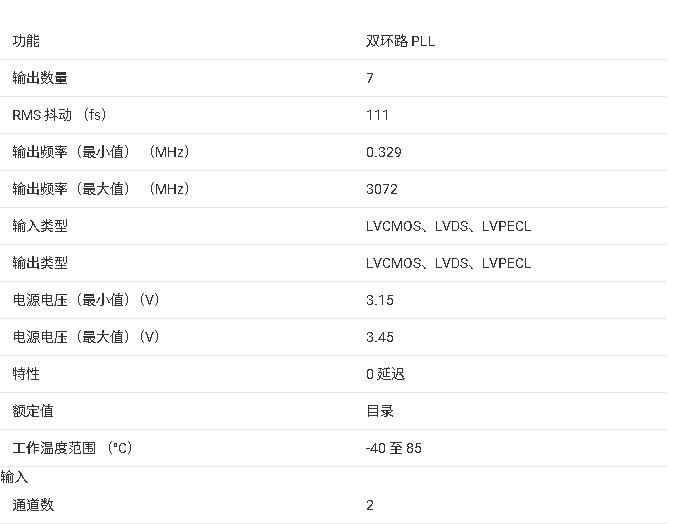

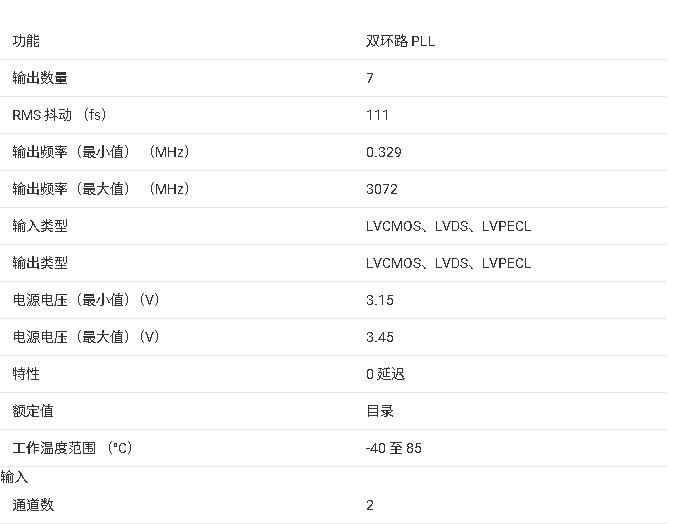

LMK04816 器件是業界性能最高的時鐘調理器,具有卓越的性能 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統要求。雙環路PLLATINUM架構支持111 fs RMS抖動(12

2025-09-15 11:20:50 676

676

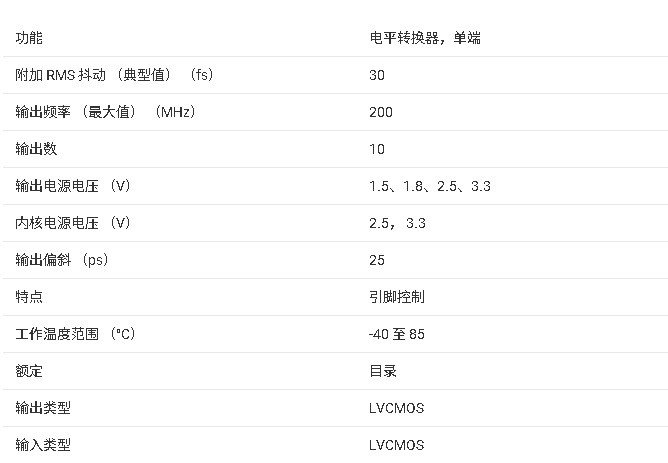

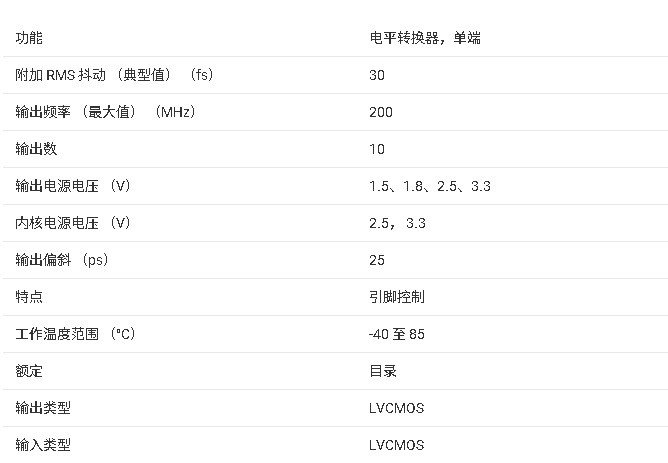

LMK00101是一款高性能、低噪聲的LVCMOS扇出緩沖器,可分配 10個來自差分、單端或晶體輸入的超低抖動時鐘。The LMK00101 支持同步輸出使能,實現無毛刺作。超低偏斜、低抖動和 高

2025-09-15 15:41:45 746

746

。該LMK03806集成了高性能整數N PLL、低噪聲VCO和可編程輸出分頻器,可從低成本晶體為SONET、以太網、光纖通道、XAUI、背板、PCIe、SATA和網絡處理器生成多個參考時鐘。

2025-09-16 09:45:23 661

661

LMK0480x 系列是業界性能最高的時鐘調節器,具有卓越的 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統要求。雙回路PLLatinum 該架構能夠使用低噪聲VCXO模塊實現111

2025-09-16 10:37:21 687

687

LMK0480x 系列是業界性能最高的時鐘調節器,具有卓越的 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統要求。雙回路PLLatinum 該架構能夠使用低噪聲VCXO模塊實現111

2025-09-16 10:42:44 728

728

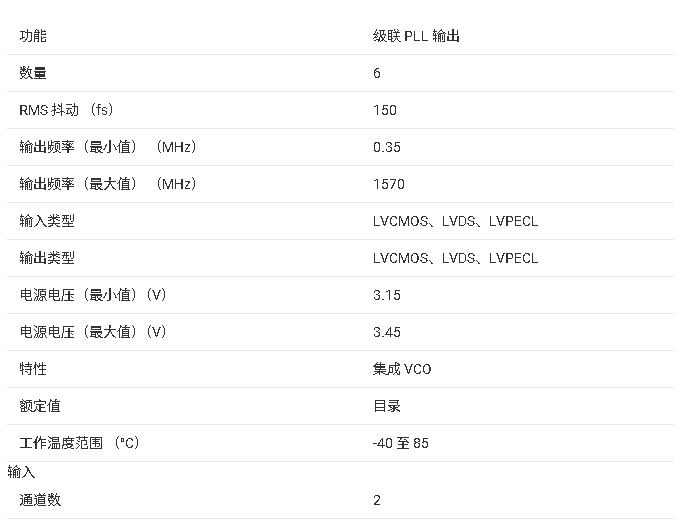

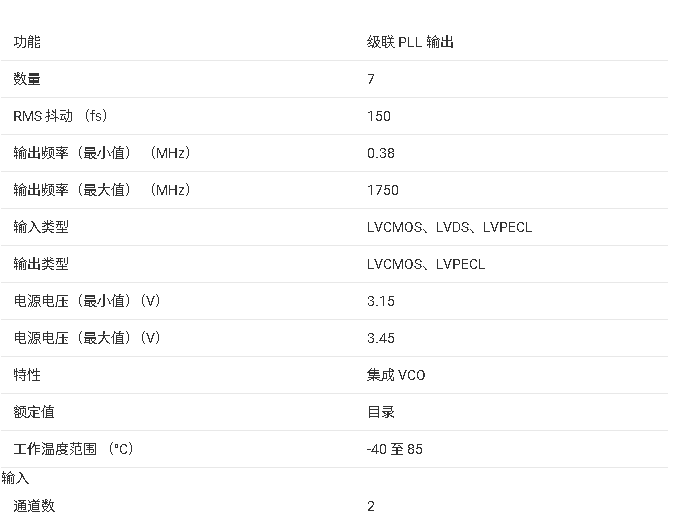

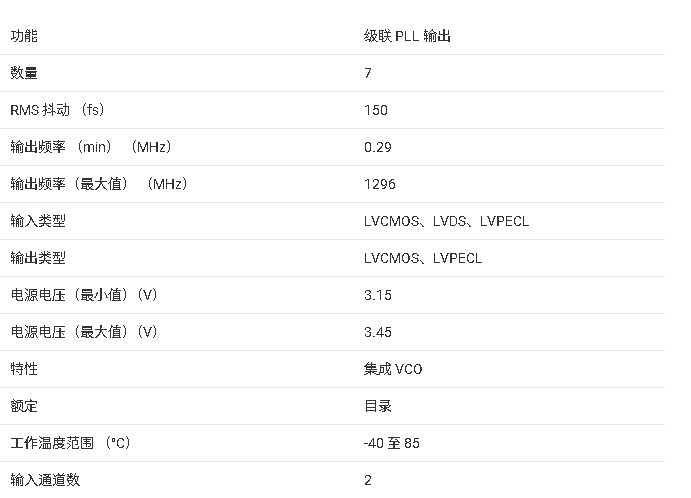

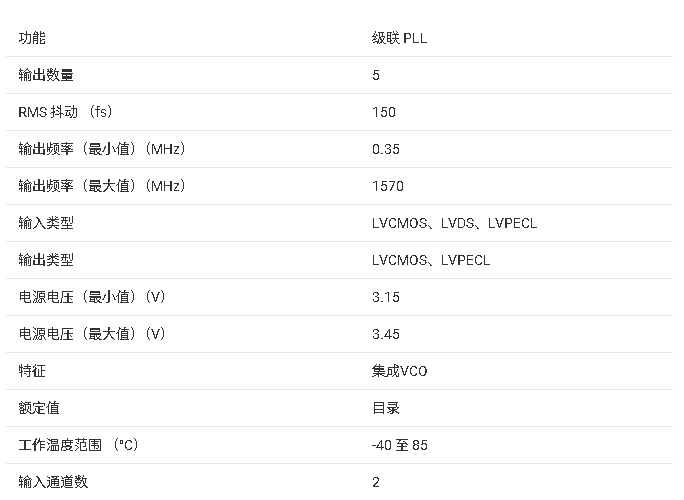

LMK04000系列精密時鐘調節器提供低噪聲抖動清除、時鐘乘法和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-17 09:22:37 643

643

LMK04000系列精密時鐘調節器提供低噪聲抖動清除、時鐘乘法和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-17 09:27:32 669

669

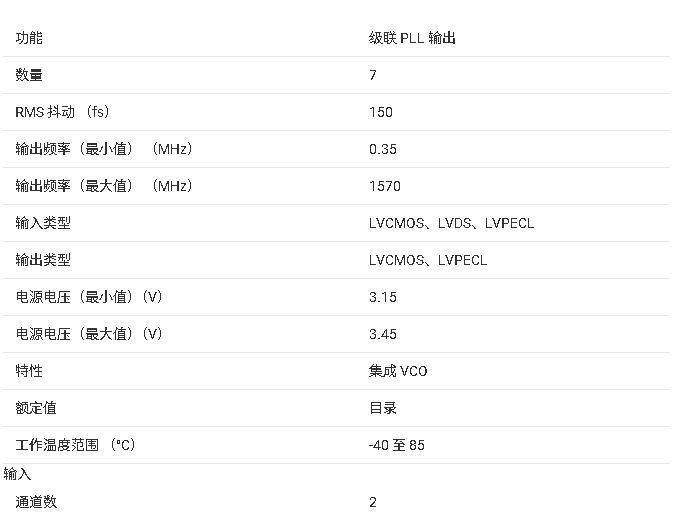

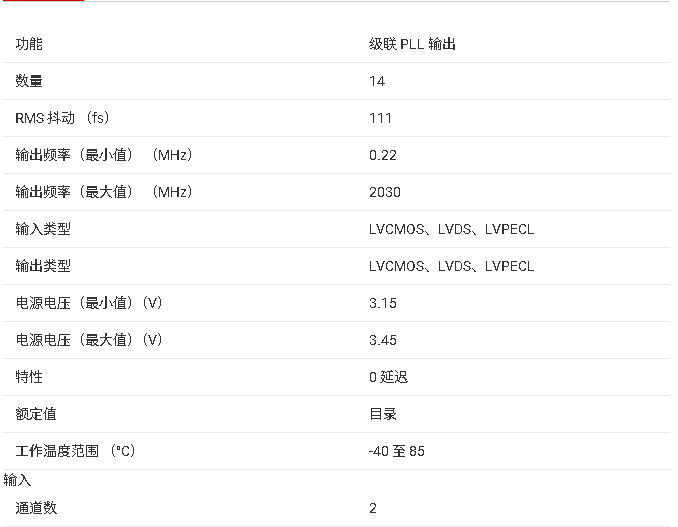

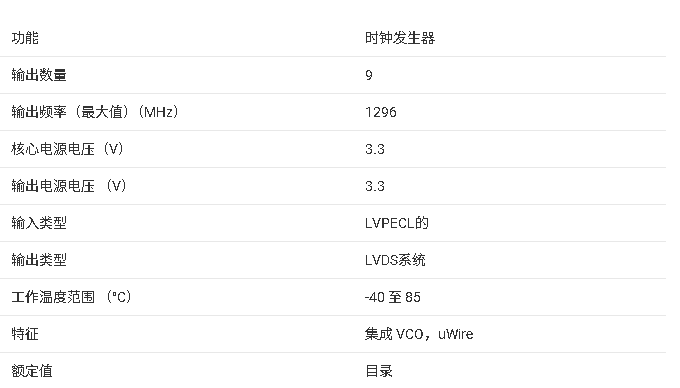

LMK03200系列精密時鐘調節器結合了抖動功能清潔/調節、乘法和參考時鐘的0延遲分布。器件集成了壓控振蕩器(VCO)、高性能整數N鎖相環(PLL)、部分集成環路濾波器,以及各種LVDS

2025-09-17 11:20:42 644

644

LMK04000系列精密時鐘調理器提供低噪聲抖動清除、時鐘倍增和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-18 09:55:12 645

645

LMK04000系列精密時鐘調理器提供低噪聲抖動清除、時鐘倍增和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-18 10:45:32 670

670

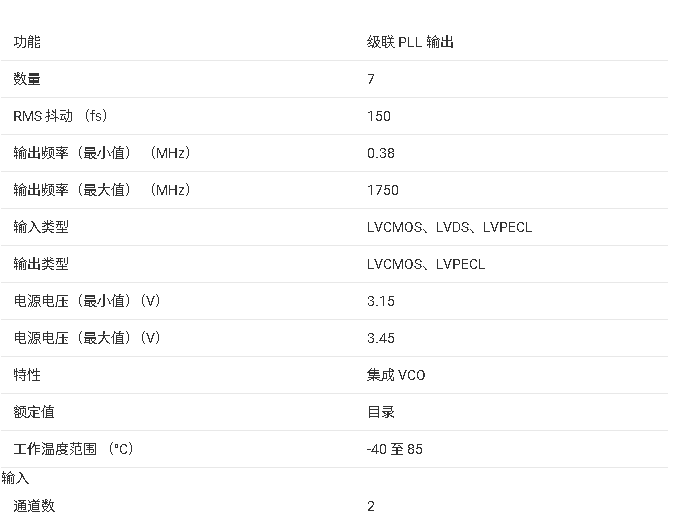

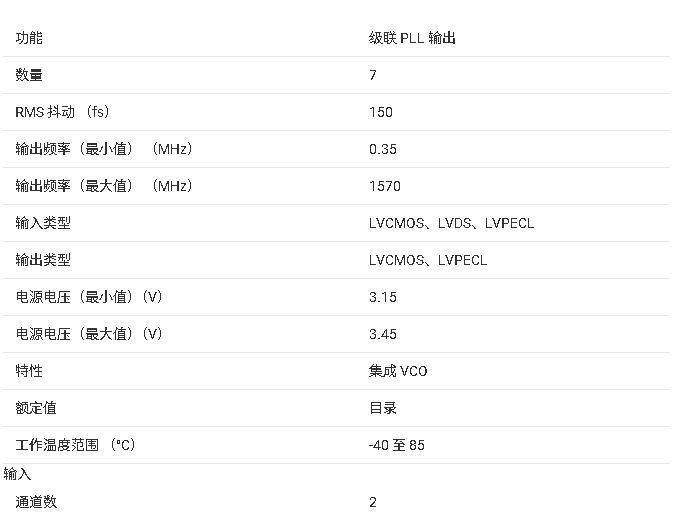

LMK03000系列精密時鐘調節器結合了抖動功能參考時鐘的清潔/再調節、乘法和分配。器件集成了壓控振蕩器 (VCO)、高性能 Integer-N 鎖相環(PLL)、部分集成環路濾波器以及各種 LVDS 和 LVPECL 中的多達 8 個輸出 組合。

2025-09-18 11:15:57 756

756

LMK04000系列精密時鐘調理器提供低噪聲抖動清除、時鐘倍增和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-18 11:33:20 596

596

LMK04000系列精密時鐘調理器提供低噪聲抖動清除、時鐘倍增和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

2025-09-18 14:06:01 580

580

LMK02002精密時鐘調節器結合了抖動清理/調節、乘法和參考時鐘分配的功能。該器件集成了高性能 Integer-N 鎖相環 (PLL) 和四個 LVPECL 時鐘輸出分配模塊。

每個時鐘分配

2025-09-18 15:18:33 526

526

LMK02000精密時鐘調節器結合了抖動清除/修復、乘法和參考時鐘分配的功能。該器件集成了高性能 Integer-N 鎖相環 (PLL)、三個 LVDS 和五個 LVPECL 時鐘輸出分配模塊

2025-09-19 10:37:45 648

648

可以使用直流和交流耦合來提供。不僅限于JESD204B應用,14個輸出均可單獨配置為傳統高性能時鐘系統輸出。 超低噪聲時鐘抖動消除器SC6301具有高性能

2024-02-19 09:41:40

電子發燒友App

電子發燒友App

評論