LMK04000系列精密時鐘調理器提供低噪聲抖動清除、時鐘倍增和分配,無需高性能壓控晶體振蕩器 (VCXO) 模塊。LMK04000 系列采用級聯 PLLatinum 架構,結合外部晶體和變容二極管,提供低于 200 飛秒 (fs) 的均方根 (RMS) 抖動性能。

*附件:lmk04031.pdf

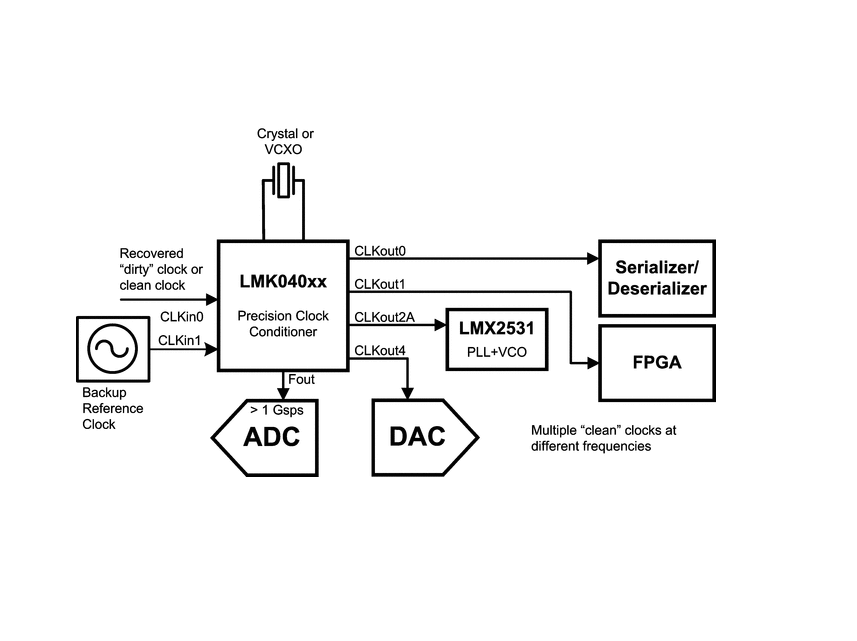

級聯架構由兩個高性能鎖相環 (PLL)、一個低噪聲晶體振蕩器電路和一個高性能壓控振蕩器 (VCO) 組成。第一個PLL (PLL1)提供低噪聲抖動清除器功能,而第二個PLL (PLL2)執行時鐘生成。PLL1 可以配置為與外部 VCXO 模塊配合使用,也可以使用帶有外部晶體和變容二極管的集成晶體振蕩器。當與非常窄的環路帶寬一起使用時,PLL1 使用 VCXO 模塊或晶體的卓越近相位噪聲(偏移低于 50 kHz)來清潔輸入時鐘。PLL1的輸出用作PLL2的干凈輸入基準電壓源,鎖定集成VCO。PLL2的環路帶寬可以優化,以清除遠相位噪聲(偏移量高于50 kHz),其中集成VCO的性能優于PLL1中使用的VCXO模塊或晶體。

LMK04000系列具有雙冗余輸入、五個差分輸出和可選的上電默認時鐘。輸入模塊配備了信號丟失檢測和參考時鐘的自動或手動選擇。每個時鐘輸出由一個可編程分頻器、一個相位同步電路、一個可編程延遲和一個LVDS、LVPECL或LVCMOS輸出緩沖器組成。CLKout2 上提供默認啟動時鐘,可用于為現場可編程門陣列 (FPGA) 或微控制器提供初始時鐘,在系統上電過程中對抖動清除器進行編程。

特性

- 級聯 PLLatinum PLL 架構

- PLL1

- 相位檢測器速率高達 40 MHz

- 集成低噪聲晶體振蕩器電路

- 帶LOS的雙冗余輸入參考時鐘

- PLL2

- 歸一化 [1 Hz] PLL 本底噪聲為 -224 dBc/Hz

- 鑒相器速率高達 100 MHz

- 輸入倍頻器

- 集成低噪聲VCO

- 超低RMS抖動性能

- 150 fs RMS 抖動 (12 kHz – 20 MHz)

- 200 fs RMS 抖動 (100 Hz – 20 MHz)

- LVPECL/2VPECL、LVDS和LVCMOS輸出

- 支持高達 1080 MHz 的時鐘速率

- 上電時默認時鐘輸出 (CLKout2)

- 五個專用通道分頻器和延遲模塊

- 引腳兼容系列時鐘設備

- 工業溫度范圍:-40 至 85 °C

- 3.15 V 至 3.45 V 工作電壓

- 封裝:48 引腳 LLP (7.0 x 7.0 x 0.8 mm)

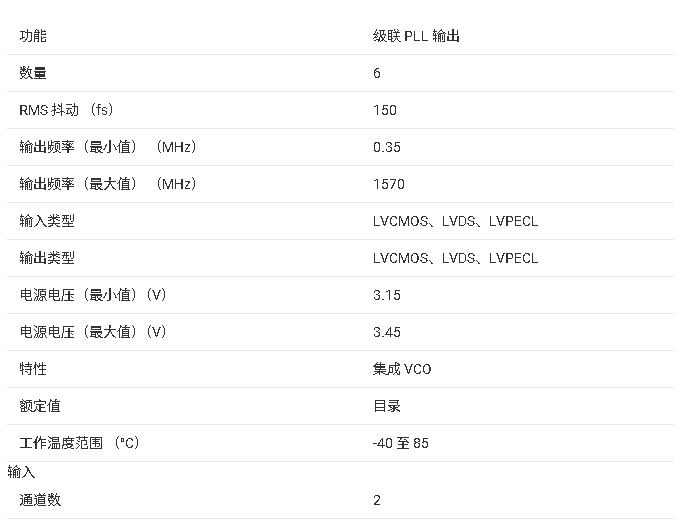

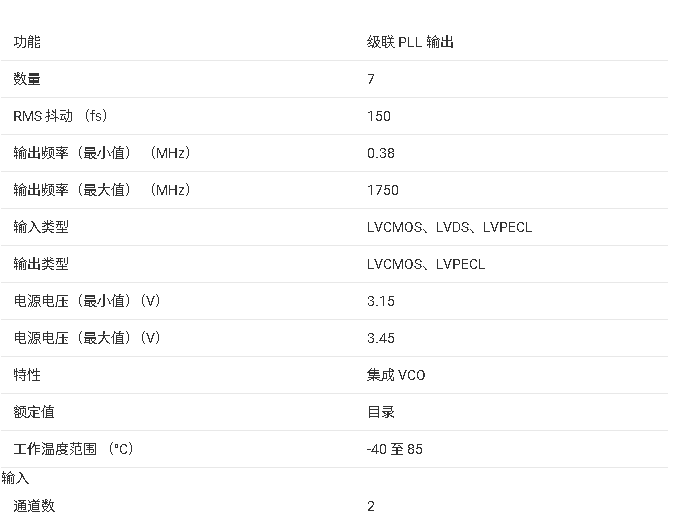

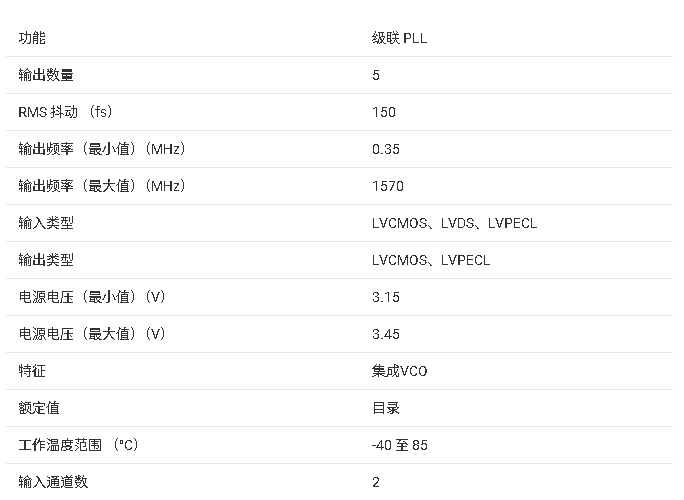

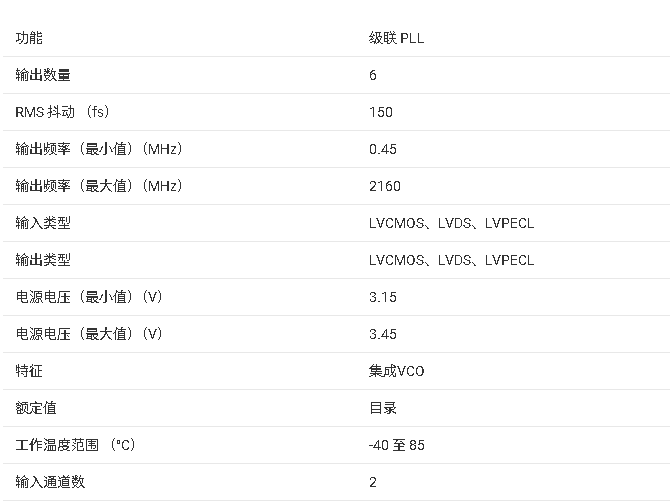

參數

方框圖

?1. 產品概述?

LMK04031是TI(德州儀器)推出的LMK04000系列精密時鐘調節器成員,采用級聯PLLatinum?架構,專為超低抖動時鐘生成與分配設計。核心特性包括:

- ?雙PLL級聯架構?:PLL1(最高40MHz相位檢測率)用于參考時鐘清潔,PLL2(最高100MHz相位檢測率)負責時鐘生成,結合外部晶體/VCXO實現亞200飛秒(fs) RMS抖動性能。

- ?輸出類型?:支持LVPECL/2VPECL、LVDS和LVCMOS輸出,頻率最高達1080MHz。

- ?應用領域?:數據轉換器時鐘、無線基礎設施、網絡設備(SONET/SDH)、醫療及軍事航空等。

?2. 關鍵特性?

- ?超低抖動?:12kHz–20MHz帶寬下150fs RMS,100Hz–20MHz下200fs RMS。

- ?靈活配置?:5個獨立可編程通道(分頻/延遲/使能控制),支持冗余參考輸入(CLKin0/1)和自動切換模式。

- ?集成功能?:內置VCO(1430–1570MHz)、晶體振蕩電路、頻率倍增器及可編程環路濾波器(支持3/4階)。

?3. 架構與功能?

- ?PLL1?:清潔輸入時鐘,窄帶寬(10–200Hz)優化近端相位噪聲。

- ?PLL2?:寬帶寬(50–200kHz)抑制遠端噪聲,集成VCO提供低噪聲時鐘源。

- ?時鐘分配?:各通道支持分頻(2–510)、相位延遲(0–2250ps,步進150ps)及同步控制(SYNC*引腳)。

?4. 電氣特性?

- ?工作條件?:3.15–3.45V供電,工業溫度范圍(-40°C至85°C)。

- ?相位噪聲?:典型值-110dBc/Hz @1kHz偏移(250MHz輸出)。

- ?封裝?:48引腳WQFN(7.0×7.0×0.8mm),帶裸露焊盤增強散熱。

?5. 設計支持?

- ?外部元件?:需配置PLL1/PLL2環路濾波器,推薦使用高質量VCXO或晶體(6–20MHz)。

- ?熱管理?:建議PCB設計包含散熱過孔和銅層,確保結溫≤125°C。

- ?編程接口?:通過Microwire串行接口(CLKuWire/DATAuWire/LEuWire)配置寄存器。

?6. 典型應用電路?

?7. 性能優化建議?

- 選擇低相位噪聲VCXO以優化整體抖動。

- 使用內部集成濾波器組件減少外部元件數量。

- 通過頻率倍增器(EN_PLL2_REF2X)提升PLL2比較頻率,降低帶內噪聲。

?文檔范圍?

涵蓋器件功能、寄存器配置、電氣參數、應用電路及布局指南,適用于高頻低抖動時鐘系統設計。

-

晶體

+關注

關注

2文章

1442瀏覽量

37650 -

變容二極管

+關注

關注

3文章

82瀏覽量

17221 -

晶體振蕩器

+關注

關注

9文章

749瀏覽量

33359 -

RMS

+關注

關注

2文章

158瀏覽量

37799 -

精密時鐘

+關注

關注

0文章

8瀏覽量

1270

發布評論請先 登錄

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

LMK04832-SEP符合JESD204B/C標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

LMK04368-EP符合JESD204B/C標準的超低噪聲、雙環路時鐘抖動清除器數據表

LMK04832-SP符合JESD204B標準的航天級、超低噪聲、雙環路時鐘抖動清除器數據表

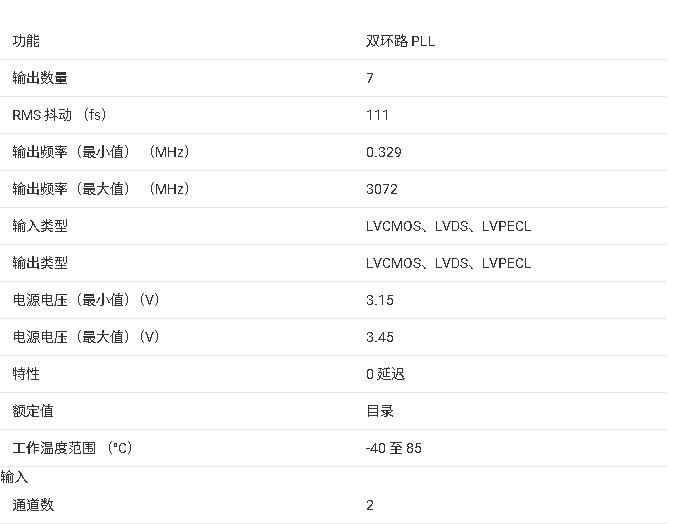

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

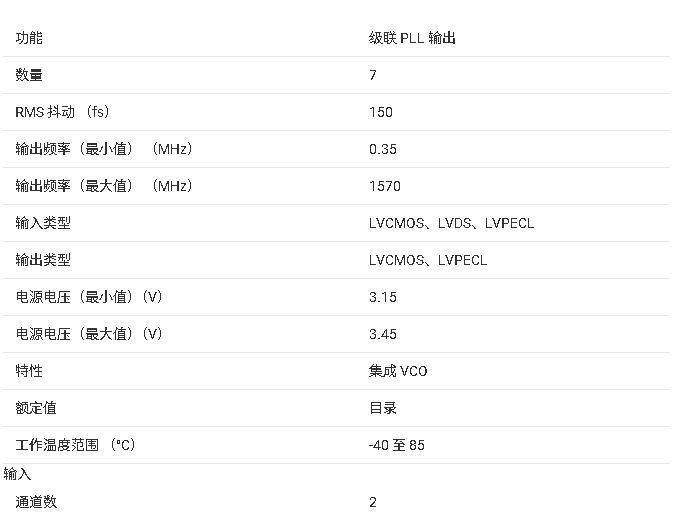

LMK04906帶6路可編程輸出的,超低噪聲時鐘抖動清除器和乘法器數據表

具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表

?LMK04031 低噪聲時鐘抖動清除器技術文檔總結

?LMK04031 低噪聲時鐘抖動清除器技術文檔總結

評論