【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

“封測廠已經跟不上晶圓代工的腳步了,摩爾定律都開始告急了,我們與其在里面干著急,不如做到外面去”,2011年,臺積電的余振華面對媒體如是說。2011年,臺積電宣布將會做先進封裝。經過兩年時間,臺積電開發出了CoWoS技術。但由于價格昂貴,只有Xilinx使用,為了拿下蘋果這個客戶,臺積電開發出了一種精簡的設計,能夠將CoWoS結構盡量簡化,并且價格壓到原來的五分之一。這個技術就是后來的InFO技術。

自此,臺積電的先進封裝分成了兩部分,更為經濟的InFO封裝技術,成為收集客戶采用的首選,這也是臺積電拿下蘋果這個客戶的原因。而專注于高階客戶市場的CoWoS技術也因為人工智能的發展,得到進一步發展與應用。

2012年臺積電在與賽靈思合作推出Virtex-7 HT系列FPGA的過程中(由4顆28nm FPGA芯片并排安裝在硅中介層)便開發了TSV、μBump及RDL技術,并將這一系列技術命名為CoWoS(Chip-on-Wafer-on-Substrate)。隨后公司研發出InFO封裝,大幅降低了封裝體積。2018年,臺積電又公布了系統整合單芯片(SoIC)技術,標志著臺積電已具備直接為客戶生產3DIC的能力。

一、CoWoS工藝技術的介紹

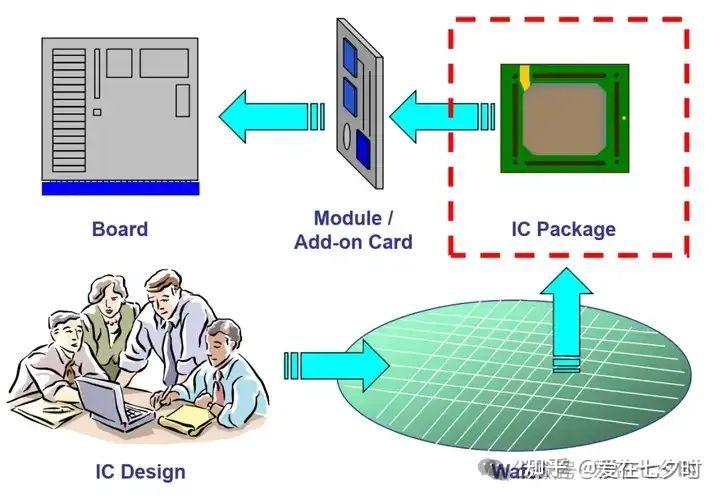

CoWoS,英文全稱:Chip-on-Wafer-on-Substrate,它是一種先進的半導體封裝工藝技術,廣泛應用于高性能計算、人工智能、數據中心等領域。

CoWoS工藝技術概念,簡單來說是先將半導體芯片(像是處理器、記憶體等),一同放在硅中介層上,再透過Chip on Wafer(CoW)的封裝制程連接至底層基板上。換言之,也就是先將芯片通過Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把CoW 芯片與基板連接,整合成CoWoS;利用這種封裝模式,使得多顆芯片可以封裝到一起,透過Si Interposer 互聯,達到了封裝體積小,功耗低,引腳少的效果。

1、CoWoS的關鍵技術點

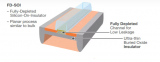

講到這里,我們就不得不回顧一下2.5D封裝了,所謂的2.5D 封裝,主要的概念是將處理器、記憶體或是其他的芯片,并列排在硅中介板(Silicon Interposer)上,先經由微凸塊(Micro Bump)連結,讓硅中介板之內金屬線可連接不同芯片的電子訊號;接著再透過硅穿孔(TSV)來連結下方的金屬凸塊(Solder Bump),再經由導線載板連結外部金屬球,實現芯片、芯片與封裝基板之間更緊密的互連。

而RDL(Redistributionlayer)再分布層則是在晶圓水平上,觸點再分布可以很高效的進行。再分布層用于使連線路徑重新規劃,落到我們希望的區域,也可以獲得更高的觸點密度。再分布的過程,實際上是在原本的晶圓上又加了一層或幾層。首先淀積的是一層電介質用于隔離,接著我們會使原本的觸點裸露,再淀積新的金屬層來實現重新布局布線。UBM在這里會被用到,作用是支撐焊錫球或者其他材料的接觸球。

講到的Interposer硅中介層指的是焊錫球和晶粒之間導電層。它的作用是擴大連接面,使一個連接改線到我們想要的地方。與再分布層作用類似。簡單來說,硅中介層是CoWoS技術的核心組件,提供了高密度的互連網絡。中介層上的微米級金屬線和通孔(TSV,Through-Silicon Via)實現了芯片間的高速數據傳輸。

最后講的就是TIM(hermal interface material)熱界面材料,由于薄膜通常包含在高級封裝中,所以有了TIM以幫助降低從有源die到周圍環境的總熱阻。(對于非常高功率的器件,通常應用兩層 TIM 材料層——die和封裝蓋之間的內層以及封裝和散熱器之間的一層。)

而CoWoS工藝技術則是一種2.5D的整合生產技術,先將芯片通過Chip on Wafer(CoW)的封裝制程連接至硅晶圓,再把CoW芯片與基板(Substrate)連接,整合成CoWoS。

嚴格的來說,CoWoS 是一種 2.5D、3D 的封裝技術,可以分成「CoW」和「WoS」來看。 「CoW(Chip-on-Wafer)」是晶片堆疊; 「WoS(Wafer-on-Substrate)」則是將芯片堆疊在基板上。 CoWoS 就是把芯片堆疊起來,再封裝于基板上,最終形成 2.5D、3D 的形態,可以減少芯片的空間,同時還減少功耗和成本。 下圖為CoWoS封裝示意圖,將邏輯芯片及HBM(高帶寬記憶體)先連接于中介板上,透過中介板內微小金屬線來整合左右不同芯片的電子訊號,同時經由「砂穿孔(TSV)」技術來連結下方基板,最終透過金屬球銜接至外部電路。

而2.5D與3D封裝技術則是差別在堆疊方式。 2.5D 封裝是指將芯片堆疊于中間層之上或透過硅橋連接芯片,以水平堆疊的方式,主要應用于拼接邏輯運算芯片和高帶寬存儲器; 3D 封裝則是垂直堆疊芯片的技術,主要面向高效能邏輯芯片、SoC 制造。

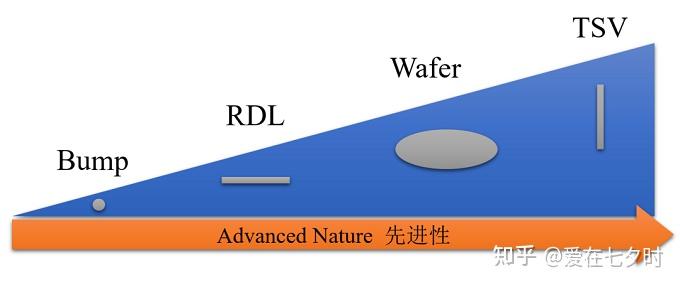

但作為先進封裝工藝技術,我們要明白:一說到先進封裝,首先想到的會是臺積電而非傳統封測大廠,因為先進封裝已經面臨到 7nm 以下,而傳統封裝廠研發速度已無法跟進晶圓制程的腳步,其中 CoWoS 中的 CoW 部分過于精密,只能由臺積電制造,所以才會造就這番景象。 同時,臺積電擁有許多全世界的高階客戶,為此「一條龍」的服務更能同時維持制程與封裝部分的良率,未來面對高階客戶的交付工作也將更為極致。

2、CoWoS技術的分支

CoWoS 可細分為 S、R、L 三類,分別對應硅中介層(Si Interposer)、重布線層(RDL)與局部硅互聯技術(LSI)。目前市面上主流為 CoWoS-S,不論是 AI 伺服器、高效能運算產品皆使用 CoWoS-S,但缺點是生產成本過高。

所以,目前臺積電會提供以上這三種CoWoS封裝服務,但隨著英偉達Blackwell系列GPU的大規模生產,臺積電將從2025年第四季度開始從CoWoS-S過渡到CoWoS-L工藝,使CoWoS-L成為臺積電CoWoS技術的主要工藝。

CoWoS-S類

通過采用單片矽中介層和矽通孔(TSVs)實現晶片與基板之間高速電信號的直接傳輸,不過其單片矽中介層存在容易出現良率問題的不足。它面向高性能計算應用,具備同類最佳的性能以及最高的集成密度。作為晶圓級系統集成平臺,CoWoS-S 能夠提供廣泛的內插器尺寸、豐富的 HBM 立方體數量以及多樣的封裝尺寸,并且可達成比 2 倍掩模版尺寸(約 1,700mm2)更大的內插器,從而可以將領先的 SoC 芯片與四個以上的 HBM2/HBM2E 立方體集成在一起。

CoWoS-R類

CoWoS-R隸屬于 CoWoS 高級封裝家族,運用 InFO 技術,以有機中介層替換 CoWoS-S 的矽中介層。該有機中介層含有精細間距的 RDL(重新布線層),能夠為 HBM 與 SoC 晶片或者晶片與基板之間構建高速連接通道。有機中介層由聚合物和銅線組成,憑借自身柔韌性充當壓力緩沖器,可有效減少因基板與中介層之間熱膨脹系數不匹配所引發的可靠性問題。

CoWoS-R 不僅可靠性優越、良率良好,還能助力新的封裝擴展尺寸,以適應更復雜的功能需求。其 RDL 內插器由聚合物和銅跡線構成,機械方面相對靈活,有助于增強 C4 關節的完整性,進而使封裝能夠進一步擴大規模,滿足更為復雜的功能要求,在 HBM 和 SoC 異構集成等小芯片之間的互連方面有著重要作用。

CoWoS-R技術的主要特點包括:

(1)RDL內插器最多由6L銅層組成,用于最小布線。間距為4微米(2微米線寬/間距)。

(2)RDL互連提供了良好的信號和電源完整性性能,路由線路的RC值更低,以實現高傳輸數據速率。帶有六個RDL互連的共面GSGSG和層間接地屏蔽提供了出色的電氣性能。

(3)由于SoC和相應襯底之間的CTE失配,RDL層和C4/UF層提供了良好的緩沖效果。C4凸起使應變能密度大大降低。

CoWoS-L類

CoWoS-L 是臺積電當前的最新技術,屬于 CoWoS 平臺中的后置晶片封裝,它融合了 CoWoS-S 和 InFO 技術的優勢,借助帶有 LSI(局部矽互連)晶片的中介層,實現極為靈活的整合,用于晶片間的互連以及 RDL 層的電源和信號傳輸。它保留了 CoWoS-S 中的矽通孔(TSVs)這一特征,以此減少了因使用大矽中介層在 CoWoS-S 里出現的良率問題。

作為 CoWoS 平臺中重要的芯片級封裝之一,CoWoS-L 結合 CoWoS-S 和 InFO 技術優點,運用內插器與 LSI 芯片達成最靈活的集成方式,服務于管芯到管芯的互連,并依靠 RDL 層完成功率和信號傳遞。該產品起始便具備 1.5 倍掩模版插入器尺寸,能實現 1 倍 SoC + 4 倍 HBM 立方體的配置,后續還可進一步拓展外殼尺寸,以便集成更多芯片。此外,它在矽中介層中加入主動元件 LSI,提升了晶片設計及封裝彈性,可堆疊多達 12 顆 HBM3,成本比 CoWoS-S 更低,預計 2024 年推出,有望成為未來 CoWoS 技術主流,新一代 AI 晶片有機會應用此項技術。

在部分實際案例中,可能會采用絕緣通孔(TIVs)替代 TSVs,目的是減少插入損耗。其封裝從 1.5 倍光罩尺寸的中介層起步,配置 1 個 SoC 和 4 個 HBM 方塊,并可進一步擴展到更大尺寸以整合更多晶片。

CoWoS-L服務的主要特點包括:

(1)大規模集成電路芯片,用于通過多層亞微米銅線實現高布線密度的管芯間互連。大規模集成電路芯片可以在每個產品中采用多種連接架構(例如,SoC到SoC、SoC到小芯片、SoC到HBM等),也可以在多個產品中重復使用。相應的金屬類型、層數和間距與CoWoS-S的產品一致

(2)基于模制的內插器在正面和背面都具有寬間距的RDL層,并且用于信號和功率傳輸的TIV(直通內插器通路)在高速傳輸中提供了低損耗的高頻信號。

(3)能夠在片上系統芯片的正下方集成額外的元件,例如獨立的IPD(集成無源器件),以更好的PI/SI支持其信號通信。

芯片的布局設計,遂成為延續摩爾定律的新解方,異構整合(Heterogeneous Integration Design Architecture System,HIDAS)概念便應運而生,同時成為IC 芯片的創新動能。

所謂的異構整合,廣義而言,就是將兩種不同的芯片,例如記憶體+邏輯芯片、光電+電子元件等,透過封裝、3D 堆疊等技術整合在一起。換句話說,將兩種不同制程、不同性質的芯片整合在一起,都可稱為是異構整合。

3、CoWoS的技術優勢

提升帶寬和性能

通過減少芯片之間的互連距離,CoWoS技術顯著提高了數據傳輸帶寬和速度,降低了延遲。適用于需要快速數據處理和高吞吐量的應用場景。

功耗優化

緊密的芯片集成和高效的互連設計降低了系統的整體功耗,延長了設備的使用壽命。

靈活的設計和制造

CoWoS技術支持不同工藝節點和不同類型芯片的集成,設計靈活性大。可以根據具體需求進行定制化設計,滿足多樣化的市場需求。

相比第三代技術,第五代CoWoS-S的晶體管數量將增加20倍,中介層面積也會提升3倍。第五代封裝技術還將封裝8個128G的HBM2e內存和2顆大型SoC內核。

2010 年開始 2.5D Interposer 的研發,2011 年推出 2.5D Interposer 技術 CoWoS(Chip on Wafer on Substrate)。第一代 CoWoS 采用 65 納米工藝,線寬可以達到 0.25μm,實現 4 層布線,為 FPGA、GPU 等高性能產品的集成提供解決方案。

真正引爆 CoWoS 的產品是人工智能(AI)芯片。2016 年,英偉達(Nvidia)推出首款采用 CoWoS 封裝的繪圖芯片 GP100,為全球 AI 熱潮拉開序幕;2017 年 Google 在 AlphaGo 中使用的 TPU 2.0 也采用 CoWoS 封裝;2017 年英特爾(Intel)的 Nervana 也不例外的交由臺積電代工,采用 CoWoS 封裝。因成本高昂而坐冷板凳多年 CoWoS 封測產能在 2017 年首度擴充。

二、CoWoS工藝技術的制備流程

先將芯片通過Si interposer與下面的wafer堆疊在一起,其中連接部分叫ubump,是一對Cu piller中間焊Solder,填入underfill保護芯片與連接的結構。

1、將芯片連接在載板上,然后進行CMP將Si interposer減薄,接著加入RDL與Solder ball。

2、將wafer從載板上轉移到膠帶上,切割wafer,將芯片從膠帶上取下來倒置安裝在基板上。

3、最后加上保護結構并使用熱界面金屬(TIM)填充保護蓋與芯片中間的空隙。

三、CoWoS工藝技術在市場上的應用現狀

因 CoWoS-S 面臨中介層面積進一步擴大、多芯片翹曲等挑戰,在此基礎上迭代升級難度大幅增加,所以臺積電著重發力 CoWoS-L 技術。CoWoS-L 具備諸多優勢,它無需掩膜拼接,能有效解決大型硅中介層的良率問題,還可帶來更高的靈活性。其中介層由多個局部硅互連(local silicon interconnect,LSI)芯片和全局重布線(global redistribution layers)構成,形成重組的中介層(reconstituted interposer,RI),以此替代 CoWoS-S 中的單片硅中介層。

LSI 芯片保留了硅中介層的優秀特性,像亞微米銅互連、硅通孔(TSV)以及嵌入式深溝槽電容器(eDTC)等,這確保了良好的系統性能,同時規避了單個大型硅中介層的良率損失問題。并且,在 RI 中引入了絕緣體通孔(TIV)作為垂直互連,相比 TSV 有著更低的插入損耗。目前,臺積電已成功實現具備 3 倍掩膜版尺寸中介層的 CoWoS-L 結構,該結構能夠搭載多個 SoC 芯片和 8 個 HBM,穩定的可靠性結果與卓越的電氣性能顯示,CoWoS-L 架構有望延續 CoWoS-S 的擴展態勢,以滿足未來 2.5D SiP 系統在高性能計算(HPC)和 AI 深度學習方面的需求。基于這些優勢,CoWoS-L 將成為下一階段的主要封裝類型。

除了 CoWoS-L 的推進,采用 CoWoS 技術的芯片堆棧版本預計在 2027 年準備就緒,屆時 CoWoS 技術會整合 SoIC、HBM 及其他元件,構建出一個運算能力強大,可媲美資料中心服務器機架甚至整臺服務器的晶圓級系統。而到 2027 年后,3D 版的 CoWoS 技術也將登上歷史舞臺,進一步拓展 CoWoS 技術在市場中的應用范圍與影響力。

四、CoWoS工藝技術的應用領域

高端芯片走向多個小芯片、內存,堆疊成為必然發展趨勢,CoWoS 封裝技術應用的領域廣泛,包含高效能運算 HPC、AI 人工智能、數據中心、5G、物聯網、車用電子等等,可以說在未來的各大趨勢,CoWoS 封裝技術會扮演著相當重要的地位。

過去的芯片效能都仰賴半導體制程的改進而提升,但隨著元件尺寸越來越接近物理極限,芯片微縮難度越來越高,要保持小體積、高效能的晶片設計,半導體產業不僅持續發展先進制程,同時也朝晶片架構著手改進,讓芯片從原先的單層,轉向多層堆疊。 也因如此,先進封裝也成為延續摩爾定律的關鍵推手之一,在半導體產業中引領浪潮。

高性能計算(HPC):需要處理大量數據和復雜計算的領域,如科學計算、金融建模等。

人工智能(AI):AI加速器和深度學習處理器需要高帶寬和低延遲的數據傳輸。

數據中心:服務器和網絡處理器等需要高效的數據處理能力和快速的存儲訪問。

臺積電的CoWoS工藝技術通過將多個芯片緊密集成在一個封裝中,并利用硅中介層提供高速互連,顯著提升了系統的性能、帶寬和能效,適用于需要高性能和高帶寬的計算和數據處理應用。

五、CoWoS工藝技術未來展望

2021 年臺積電發布的第 5 代 CoWoS 技術(CoWoS-S5)使效能得到大幅提升。

在集成能力方面,CoWoS-S5 將插層尺寸擴大到 3 倍 rectile limit(2500 mm2),單個插層上可集成 3 個或更多邏輯芯片組以及 8 個 HBM,相比上一代,結合更大尺寸與先進節點頂層芯片,晶體管集成數量多了近 20 倍,內存堆棧數量從 4 個增加到 8 個。在散熱解決方案優化上,CoWoS-S5 具備環型封裝與帶散熱器的蓋型封裝兩種熱解決方案。環型封裝讓裸片背面暴露可直接接觸散熱器;蓋型封裝在蓋和裸片間插入熱界面材料(TIM),以往常用的凝膠型 TIM 因熱導率和可靠性覆蓋退化問題無法滿足 HPC 和人工智能領域高功率要求,所以采用了新型非凝膠 TIM,其導熱系數大于 20 W/K,TIM 覆蓋率達 100%,經多項測試后無明顯衰減,可靠性測試后熱阻衰減小于 10%。

臺積電在 2024 年歐洲技術論壇上表示,CoWoS 和 SoIC 兩項先進封裝的產能在 2026 年底前會持續快速增長。其中,CoWoS 計劃在 2023 年底到 2026 年底的 3 年間實現 60% 的產能復合年增長率,意味著 2026 年底其產能將達到 2023 年底的 4 倍左右。而 SoIC 計劃在同期實現 100% 的產能復合年增長率,2026 年底產能將達到 2023 年底的 8 倍左右。

除臺積電外,日月光等 OAST 企業也在持續擴大類 CoWoS 封裝的產能,以滿足市場需求。而CoWoS 作為業界主流的 HBM 高帶寬內存芯片同計算芯片集成技術,已廣泛應用于英偉達 AI GPU 等產品中。臺積電預估未來幾年面向 AI 和 HPC 等應用的芯片系統會同時采用 CoWoS 和 SoIC 兩項技術,為滿足復雜處理器制造需求,臺積電將同步提高這兩種先進封裝的產能。同時,臺積電還在積極擴展 CoWoS 的細分類別,未來計劃推出如整體面積更大的 CoWoS-L 等變體,進一步豐富產品形態,滿足多樣化的市場需求。

寫在最后的話

總體來看,臺積電在CoWoS技術上的大膽擴張,將為公司帶來更大的市場份額和收益,也為合作伙伴提供更多機會。這一技術的進步,不僅使得臺積電在全球半導體行業占據更強大的位置,也為未來的技術創新提供了新的契機。

隨著2026年即將到來,半導體市場的競爭將更加激烈。消費者也許會在不久的將來看到一系列基于CoWoS技術的新產品,這些產品將極大地改變人們對于高性能計算設備的認知。對于那些尋求極致性能和高效能產品的用戶而言,臺積電的最新進展無疑是一個值得關注的亮點。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

封裝

+關注

關注

128文章

9297瀏覽量

148874 -

半導體芯片

+關注

關注

61文章

945瀏覽量

72749 -

CoWoS

+關注

關注

0文章

170瀏覽量

11521

發布評論請先 登錄

AI芯片發展關鍵痛點就是:CoWoS封裝散熱

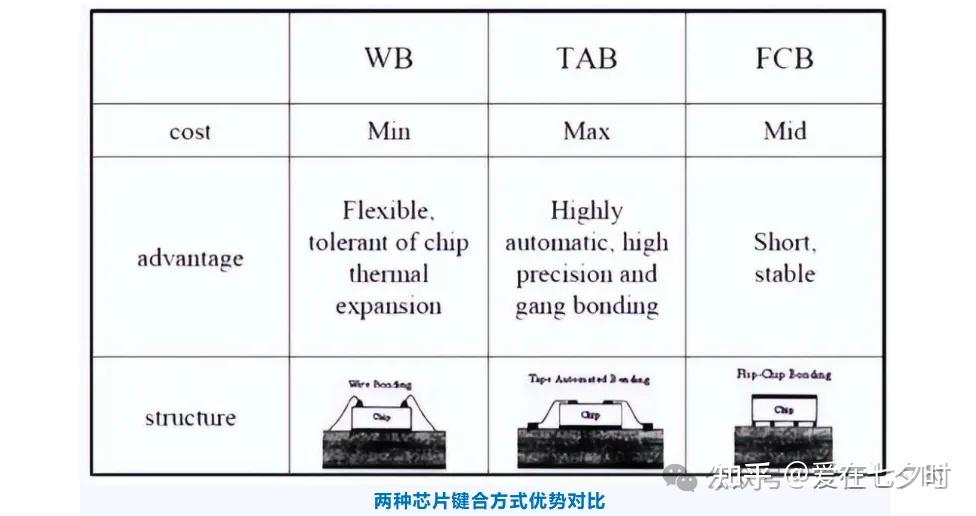

半導體芯片制造技術——“芯片鍵合”工藝技術的詳解;

熱壓鍵合工藝的技術原理和流程詳解

半導體封裝Wire Bonding (引線鍵合)工藝技術的詳解;

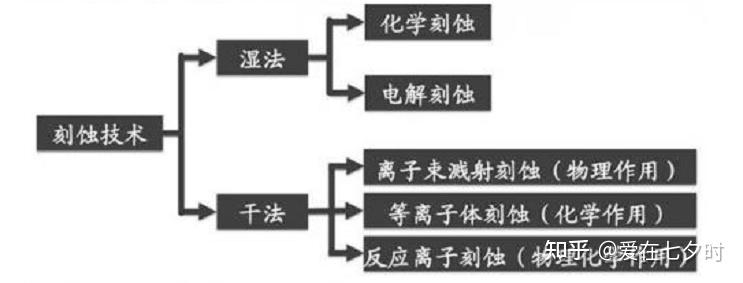

半導體“刻蝕(Etch)”工藝技術的詳解;

半導體先進封裝“Bumping(凸點)”工藝技術的詳解;

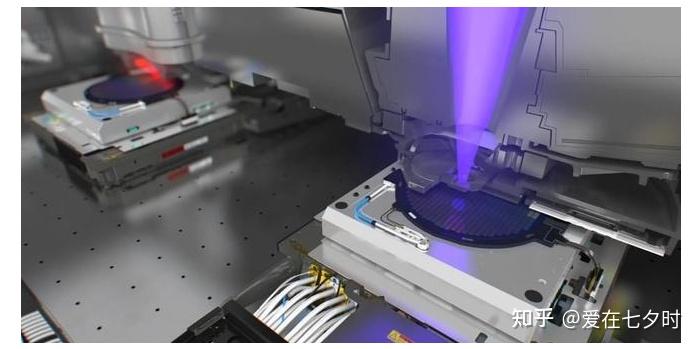

半導體“光刻(Photo)”工藝技術的詳解;

SOI工藝技術介紹

半導體后道制程“芯片鍵合(Die Bonding)”工藝技術的詳解;

半導體芯片封裝“CoWoS工藝技術”的詳解;

半導體芯片封裝“CoWoS工藝技術”的詳解;

評論