【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

內外行的朋友都知道:半導體制造過程復雜,工藝流程頗多,特別是前道的“流片”,更是繁瑣中的繁瑣。本章節要跟大家分享的就是關于“刻蝕”工藝,講到“刻蝕”工藝我想到一篇古文《核舟記》,描寫了一個微雕:

“通計一舟,為人五;為窗八;為箬篷,為楫,為爐,為壺,為手卷,為念珠各一;對聯、題名并篆文,為字共三十有四;而計其長曾不盈寸。

蓋簡桃核修狹者為之。

嘻,技亦靈怪矣哉!”

想想覺得和芯片制造中“刻蝕”有著異曲同工之妙!在完成顯影檢查的步驟之后,掩模版的圖形就被固定在光刻膠膜上;刻蝕就是通過物理或者化學手段將晶圓表面未被光刻膠保護的材料去除,將掩膜版圖形轉移到基材的工藝。

一、“刻蝕”工藝的介紹

刻蝕,英文為Etch,它是半導體制造工藝,微電子IC制造工藝以及微納制造工藝中的一種相當重要的步驟。是與光刻相聯系的圖形化(pattern)處理的一種主要工藝。所謂刻蝕,實際上狹義理解就是光刻腐蝕,先通過光刻將光刻膠進行光刻曝光處理,然后通過其它方式實現腐蝕處理掉所需除去的部分。刻蝕是用化學或物理方法有選擇地從硅片表面去除不需要的材料的過程,其基本目標是在涂膠的硅片上正確地復制掩模圖形。隨著微制造工藝的發展,廣義上來講,刻蝕成了通過溶液、反應離子或其它機械方式來剝離、去除材料的一種統稱,成為微加工制造的一種普適叫法。

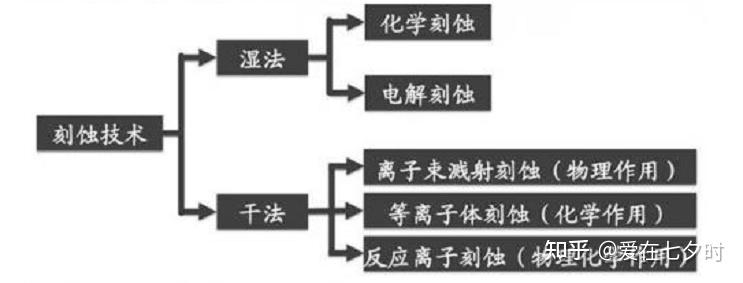

二、“刻蝕”工藝的分類

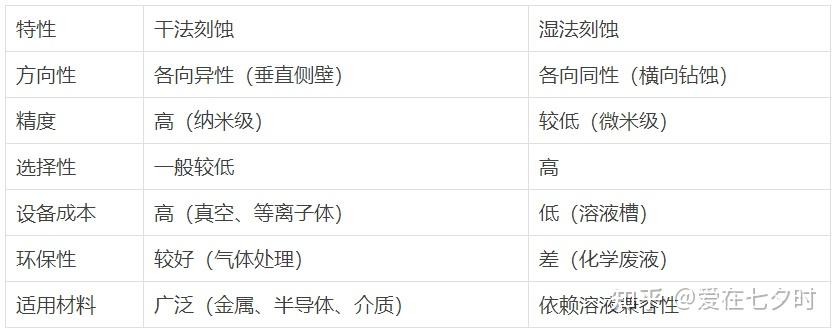

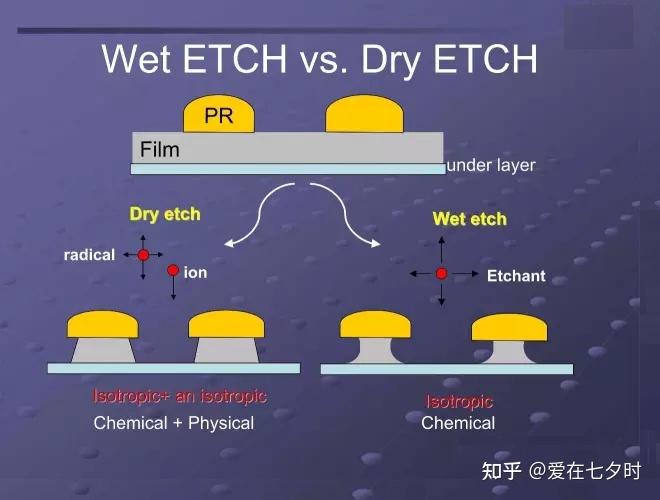

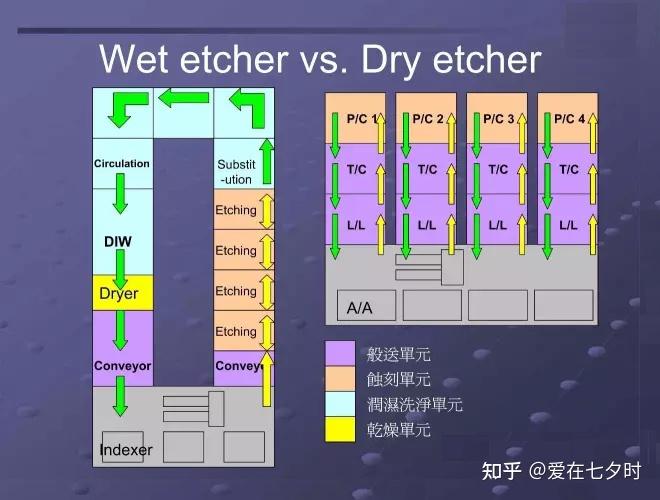

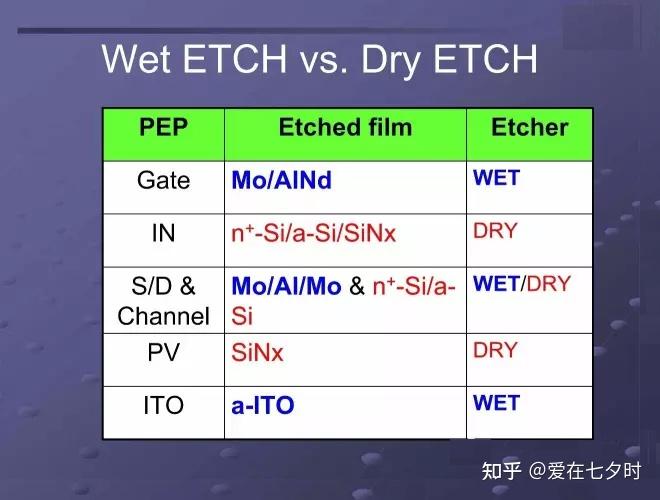

刻蝕按大類來分,主要分為:濕法刻蝕和干法刻蝕兩種,下面表格簡單對兩種刻蝕方法進行對比:

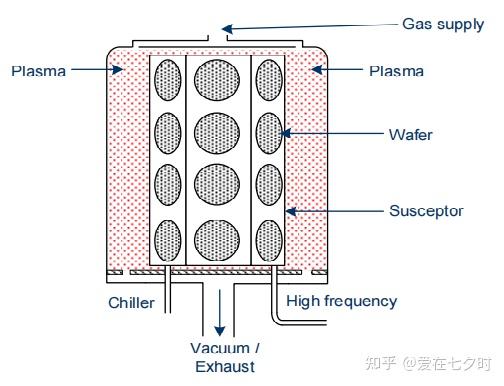

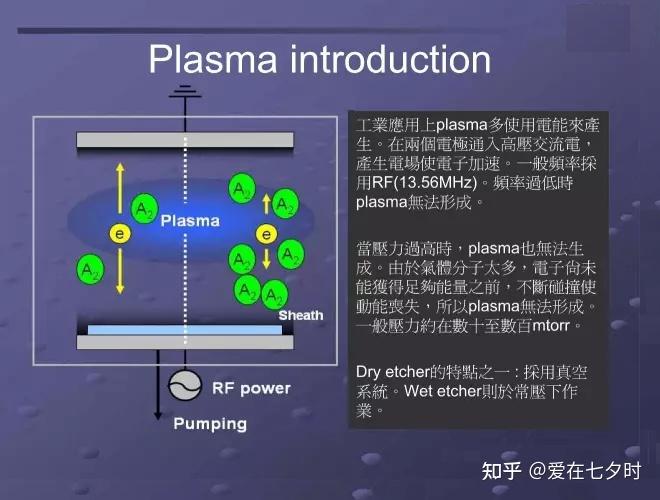

其中,在干法蝕刻中,氣體受高頻(主要為 13.56 MHz 或 2.45 GHz)激發。在 1 到 100 Pa 的壓力下,其平均自由程為幾毫米到幾厘米。

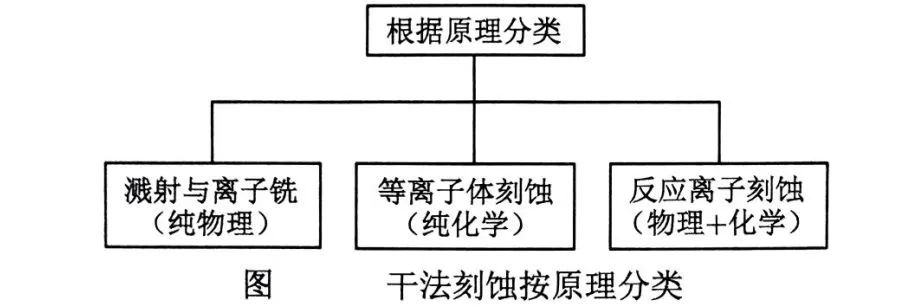

主要有三種類型的干法蝕刻:

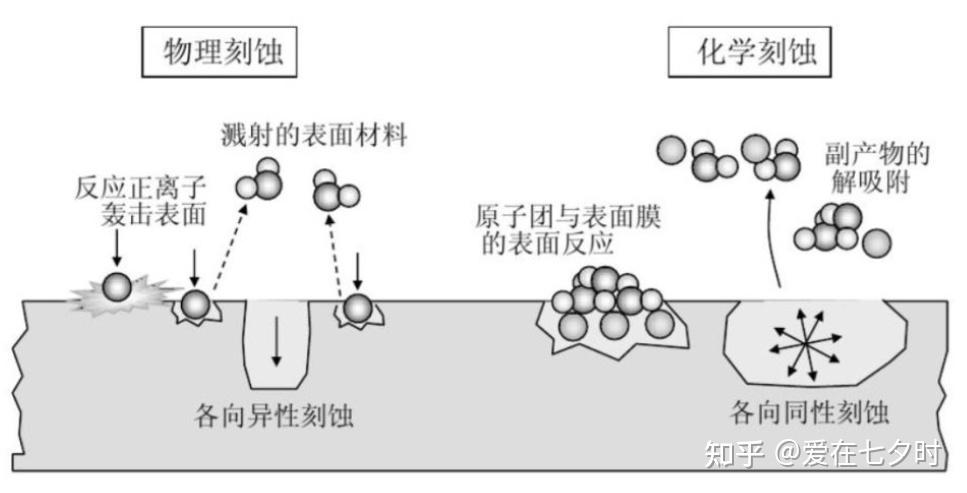

? 物理干法蝕刻:加速粒子對晶圓表面的物理磨損;

? 化學干法蝕刻:氣體與晶圓表面發生化學反應;

? 化學物理干法蝕刻:具有化學特性的物理蝕刻工藝;

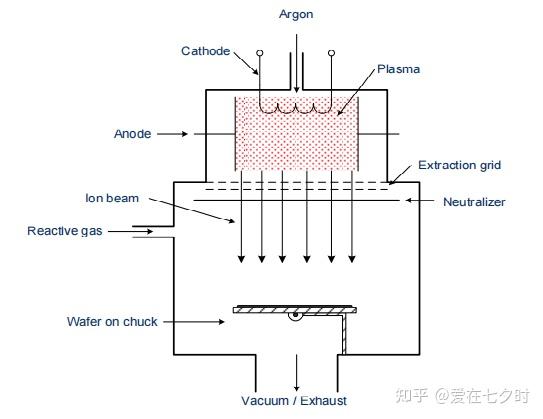

1、離子束蝕刻

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對各向異性的。選擇性低,因為其對各個層沒有差異。氣體和被打磨出的材料被真空泵排出,但是,由于反應產物不是氣態的,顆粒會沉積在晶片或室壁上。

為避免顆粒,將第二種氣體引入腔室。該氣體與氬離子發生反應并引起物理化學蝕刻過程。部分氣體與表面反應,但也與打磨出的顆粒反應形成氣態副產物。幾乎所有材料都可以用這種方法蝕刻。由于垂直輻射,垂直壁上的磨損非常低(高各向異性)。然而,由于低選擇性和低蝕刻速率,該工藝在當今的半導體制造中很少使用。

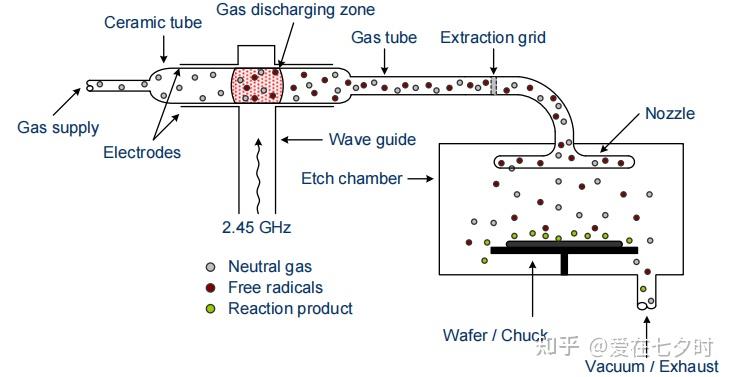

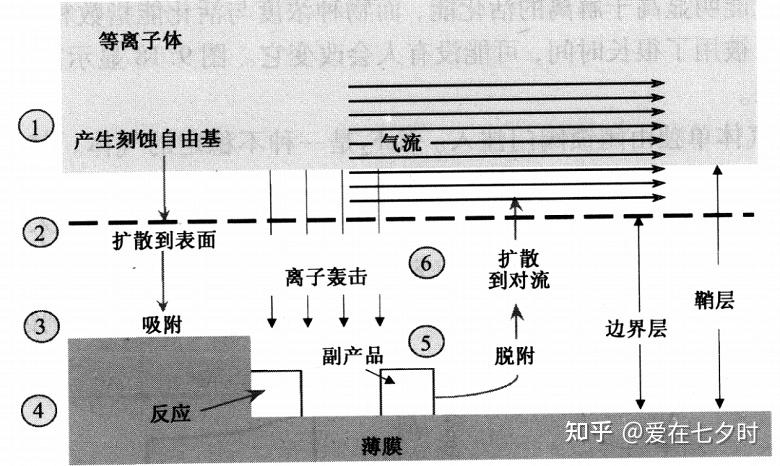

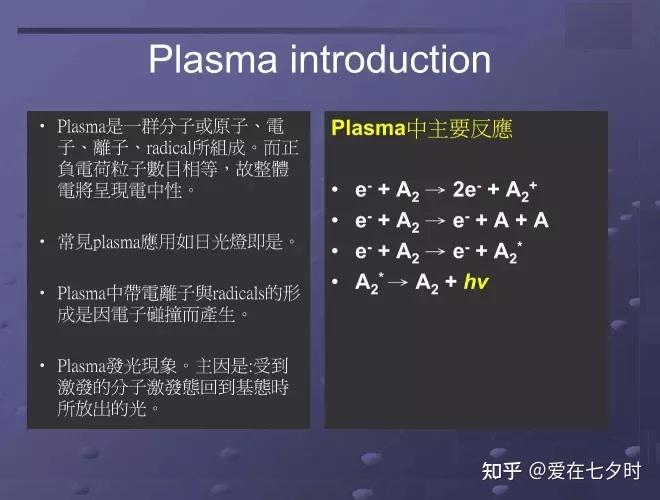

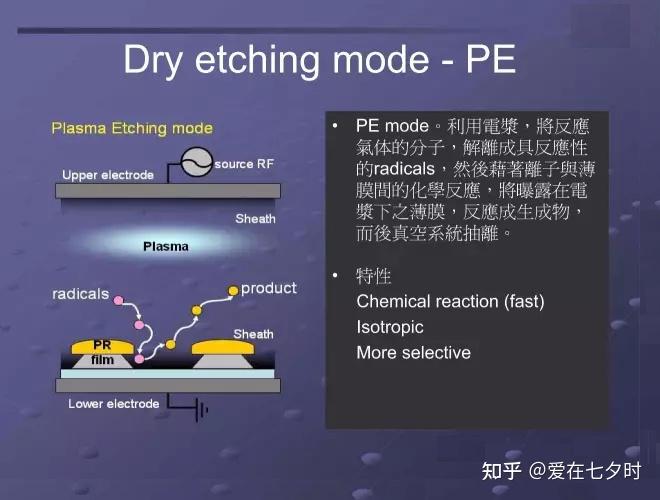

2、等離子刻蝕

等離子刻蝕(Plasma etch)是一種絕對化學刻蝕工藝(化學干法刻蝕,Chemical dry etch)。優點是晶圓表面不會被加速離子損壞。由于蝕刻氣體的可移動顆粒,蝕刻輪廓是各向同性的,因此該方法用于去除整個膜層(如熱氧化后的背面清潔)。

一種用于等離子體蝕刻的反應器類型是下游反應器。從而通過碰撞電離在2.45GHz的高頻下點燃等離子體,碰撞電離的位置與晶片分離。

在氣體放電區域,由于沖擊存在各種顆粒,其中有自由基。自由基是具有不飽和電子的中性原子或分子,因此非常活潑。作為中性氣體,例如四氟甲烷CF4被引入氣體放電區并分離成CF2和氟分子F2。類似地,氟可以通過添加氧氣 O2 從 CF4 中分離出來:

2 CF4 + O2 --->2 COF2 + 2 F2

氟分子可以通過氣體放電區的能量分裂成兩個單獨的氟原子:每個氟原子都是一個氟自由基,因為每個原子都有七個價電子,并希望實現惰性氣體構型。除了中性自由基之外,還有幾個部分帶電的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通過陶瓷管進入蝕刻室。帶電粒子可以通過提取光柵從蝕刻室中阻擋或者在它們形成中性分子的途中重新組合。氟自由基也有部分重組,但足以到達蝕刻室,在晶圓表面發生反應并引起化學磨損。其他中性粒子不是蝕刻過程的一部分,并且與反應產物一樣被耗盡。

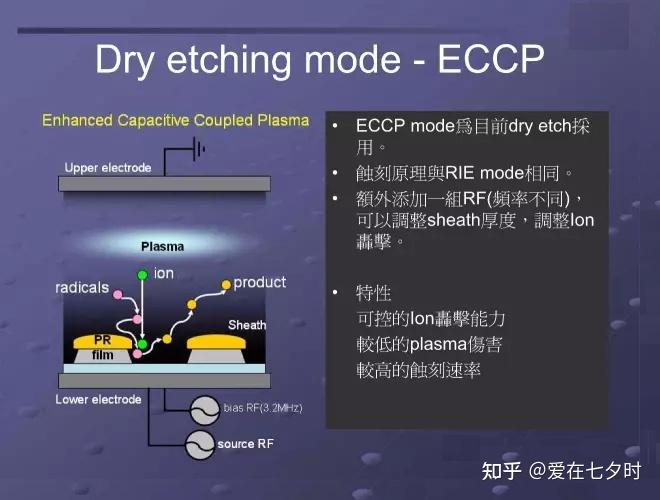

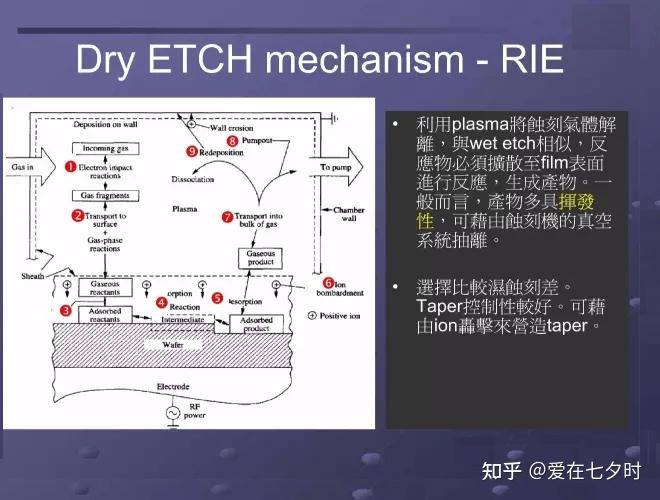

可在等離子蝕刻中蝕刻的薄膜示例: ? 硅: Si + 4F---> SiF4 ? 二氧化硅: SiO2 + 4F---> SiF4 + O2 ? 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反應離子蝕刻蝕刻特性: 選擇性、蝕刻輪廓、蝕刻速率、均勻性、可重復性 - 均可以在反應離子蝕刻 (Reactive ion etch) 中非常精確地控制。各向同性蝕刻輪廓以及各向異性是可能的。因此,RIE 工藝是一種化學物理蝕刻工藝,是半導體制造中用于構造各種薄膜的最重要工藝。 在工藝室內,晶圓放置在高頻電極(HF電極)上。通過碰撞電離產生等離子體,其中出現自由電子和帶正電的離子。如果 HF 電極處于正電壓,則自由電子會在其上積聚,并且由于它們的電子親和力而無法再次離開電極。因此,電極充電至 -1000 V(偏置電壓)。不能跟隨快速交變場的慢離子向帶負電的電極移動。

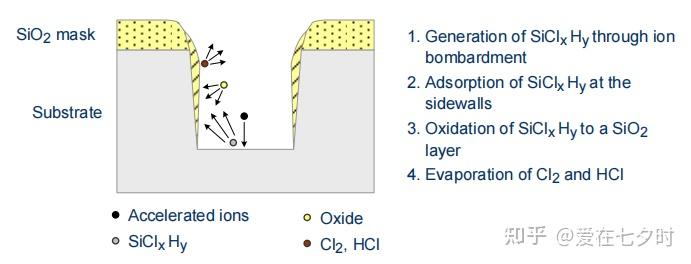

如果離子的平均自由程高,則粒子以幾乎垂直的方向撞擊晶片表面。因此,材料被加速離子(物理蝕刻)從表面擊出,此外,一些粒子與表面發生化學反應。橫向側壁不受影響,因此沒有磨損并且蝕刻輪廓保持各向異性。選擇性不是太小,但是,由于物理蝕刻進程,它也不是太大。此外,晶圓表面會被加速離子損壞,必須通過熱退火進行固化。 蝕刻工藝的化學部分是通過自由基與表面以及物理銑削材料的反應來完成的,這樣它就不會像離子束蝕刻那樣重新沉積到晶圓或腔室壁上。通過增加蝕刻室中的壓力,顆粒的平均自由程減少。因此會有更多的碰撞,因此粒子會朝著不同的方向前進。這導致較少的定向蝕刻,蝕刻過程獲得更多的化學特性。選擇性增加,蝕刻輪廓更加各向同性。通過在硅蝕刻期間側壁的鈍化,實現了各向異性的蝕刻輪廓。因此,蝕刻室內的氧氣與磨出的硅反應形成二氧化硅,二氧化硅沉積垂直側壁。由于離子轟擊,水平區域上的氧化膜被去除,使得橫向的蝕刻進程繼續進行。

蝕刻速率取決于壓力、高頻發生器的功率、工藝氣體、實際氣體流量和晶片溫度。各向異性隨著高頻功率的增加、壓力的降低和溫度的降低而增加。蝕刻工藝的均勻性取決于氣體、兩個電極的距離以及電極的材料。如果距離太小,等離子體不能不均勻地分散,從而導致不均勻性。如果增加電極的距離,則蝕刻速率降低,因為等離子體分布在擴大的體積中。對于電極,碳已證明是首選材料。由于氟氣和氯氣也會攻擊碳,因此電極會產生均勻的應變等離子體,因此晶圓邊緣會受到與晶圓中心相同的影響。

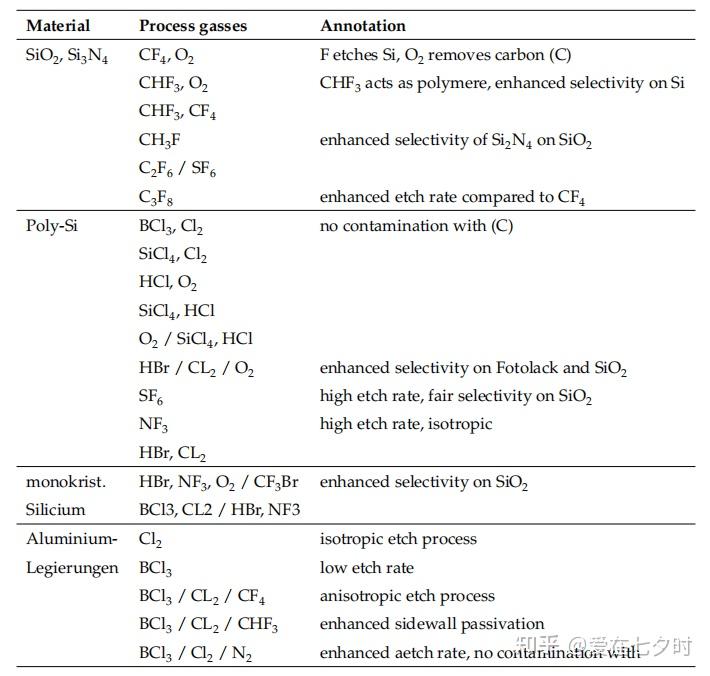

選擇性和蝕刻速率在很大程度上取決于工藝氣體。對于硅和硅化合物,主要使用氟氣和氯氣。

蝕刻工藝不限于一種氣體、氣體混合物或固定工藝參數。例如,可以首先以高蝕刻速率和低選擇性去除多晶硅上的原生氧化物,而隨后以相對于下方層的更高選擇性蝕刻多晶硅。

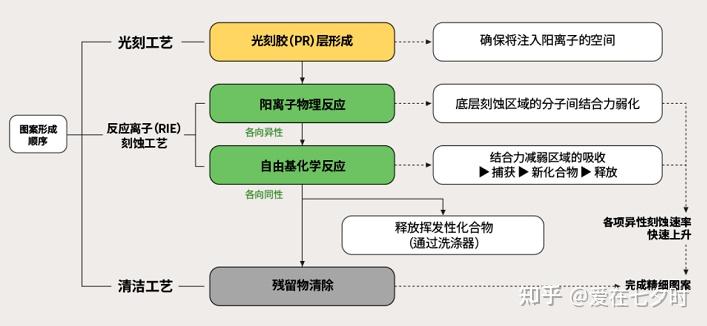

三、“刻蝕”工藝的原理

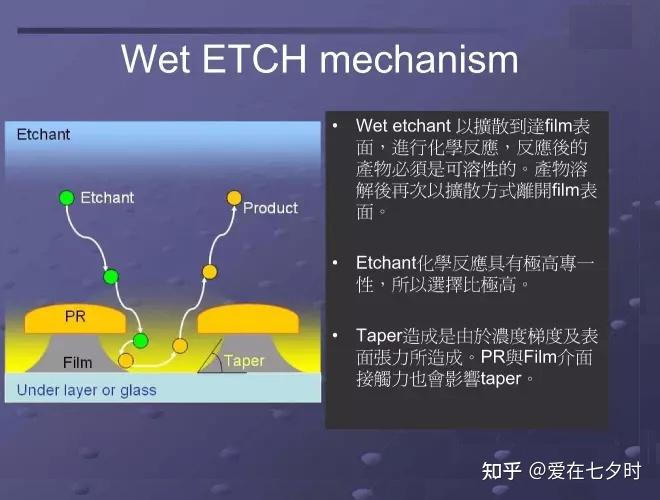

1、濕法刻蝕

(1)原理

利用化學溶液與半導體材料之間的化學反應來去除材料。將晶圓放入特定的化學試劑中,試劑與晶圓表面的物質發生反應,生成可溶解的產物,從而達到刻蝕的目的。例如,對于硅材料的刻蝕,常用的化學試劑可以是氫氧化鉀(KOH)溶液。硅與KOH和水反應,生成硅酸鉀和氫氣。

(2)特點

濕法刻蝕具有成本低、設備簡單的優點。但它對材料的選擇性相對較差,在刻蝕過程中可能會對不需要刻蝕的部分也產生一定的侵蝕,并且難以精確控制刻蝕的深度和圖案的邊緣質量。

2、干法刻蝕

(1)原理

主要依靠等離子體與半導體材料反應進行刻蝕。在低壓環境下,通過射頻電源激發氣體,產生等離子體。等離子體中的活性粒子(如離子、自由基等)與晶圓表面的材料碰撞,發生反應,生成揮發性物質,這些物質被抽氣系統帶走,實現材料的去除。例如,采用氟基氣體(如CF?)進行硅刻蝕時,氟自由基與硅反應生成四氟化硅氣體。

(2)特點

干法刻蝕的優點是刻蝕速度快、分辨率高、各向異性好,能夠實現非常精細的圖案刻蝕,并且對材料的選擇性可以通過調整氣體組分和工藝參數來控制。但是干法刻蝕設備復雜、成本高。

四、“刻蝕”工藝的歷史發展

1、早期階段(1950s-1960s)

濕法刻蝕主導:使用酸/堿溶液(如HF、HNO?)進行簡單圖形化。

局限性:各向同性刻蝕導致鉆蝕,難以滿足高精度需求。

2、干法刻蝕興起(1970s-1980s)

等離子體刻蝕(1970s):引入射頻(RF)激發氣體等離子體(如CF?/O?),實現各向異性刻蝕。

反應離子刻蝕(RIE, 1980s):結合物理離子轟擊與化學反應,提升刻蝕精度和深寬比。

應用驅動:集成電路(IC)向微米級發展,濕法無法滿足需求。

典型應用: CMOS工藝

3、高精度與新材料(1990s-2000s)

高密度等離子體刻蝕(HDP):如ICP(電感耦合等離子體)、ECR(電子回旋共振),實現更高刻蝕速率和均勻性。

新型刻蝕氣體:開發Cl?、HBr等氣體以適配銅互連、低介電常數材料。

典型應用:3D NAND存儲芯片。

挑戰:深硅刻蝕(如MEMS器件)需求推動Bosch工藝(交替沉積/刻蝕)。

4、納米時代(2010s至今)

原子層刻蝕(ALE):逐原子層去除,實現超高精度(<1nm)。

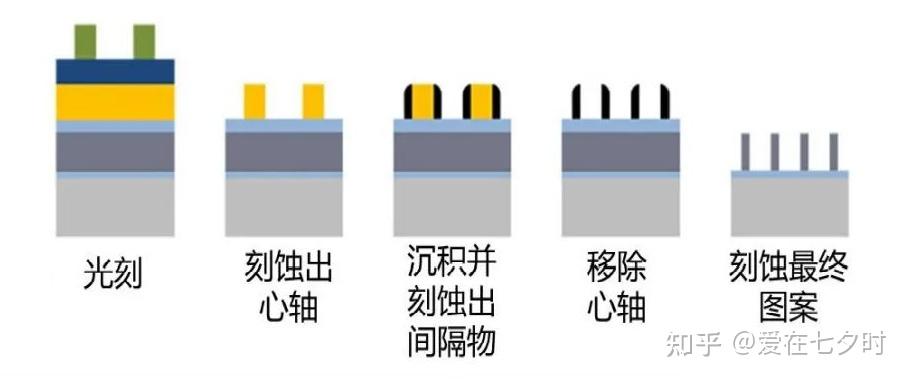

定向自組裝(DSA):結合光刻與刻蝕,突破傳統分辨率限制。

典型應用:5nm邏輯芯片、SiC功率器件。

綠色刻蝕:減少全氟化合物(PFCs)排放,發展環保工藝。

五、“刻蝕”工藝的作用

1、形成電路圖案

半導體器件是由各種復雜的電路圖案組成的,刻蝕工藝可以將光刻工藝定義的圖案精確地轉移到晶圓上。例如,在制造集成電路時,需要將設計的電路圖案從光刻版轉移到晶圓表面的光刻膠上,然后通過刻蝕工藝去除未被光刻膠保護的部分,從而形成與設計圖案一致的電路結構。

2、決定器件性能

刻蝕工藝的質量直接影響半導體器件的性能。如果刻蝕深度控制不準確,可能會導致器件的電學性能下降。例如,在制造MOS(金屬 - 氧化物 - 半導體)晶體管時,柵極氧化層的厚度需要精確控制,而這依賴于刻蝕工藝對氧化層厚度的精確處理。如果氧化層過厚或過薄,都會影響晶體管的閾值電壓和電流特性。

3、影響良率

精確的刻蝕工藝對于提高半導體制造的良率至關重要。在大規模生產中,任何微小的刻蝕缺陷都可能導致大量的芯片失效。例如,刻蝕過程中的不均勻性可能會造成芯片局部區域的尺寸偏差,導致芯片在后續測試中無法正常工作,從而降低良率。

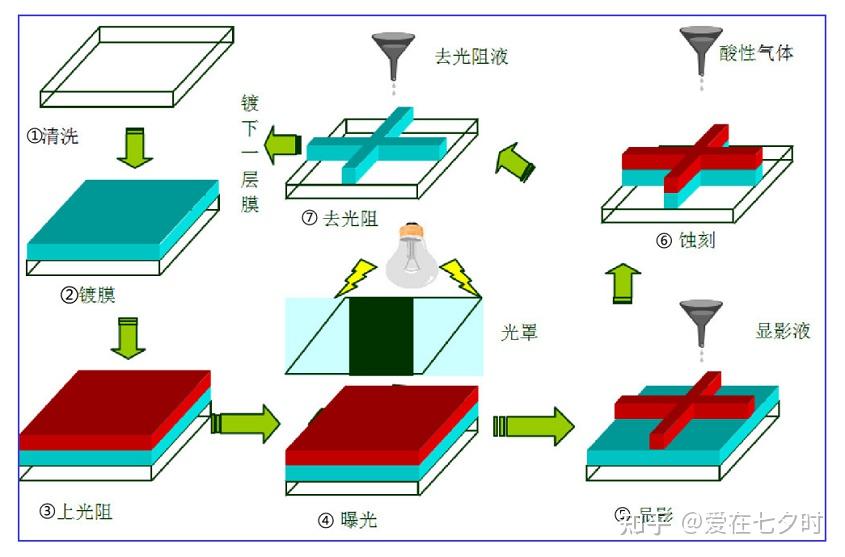

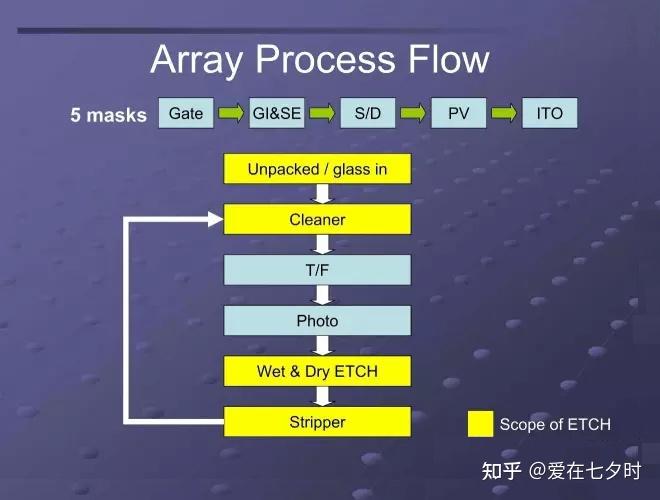

六、“刻蝕”工藝的流程

1、預處理

在進行刻蝕之前,需要對晶圓進行清洗和預處理,以去除表面的雜質和自然氧化層。清洗過程通常包括多個步驟,如使用化學溶劑清洗、超純水沖洗等,確保晶圓表面干凈、平整。

2、光刻

光刻是刻蝕工藝的前序步驟。在晶圓表面涂上一層光刻膠,然后使用光刻機將設計好的圖案曝光在光刻膠上。曝光后的光刻膠在顯影液中進行處理,未曝光的部分被溶解掉,露出晶圓表面需要刻蝕的區域。

3、刻蝕

根據選擇的刻蝕方式(濕法或干法),將晶圓放入相應的刻蝕設備中進行刻蝕。在刻蝕過程中,需要嚴格控制刻蝕的時間、溫度、壓力、氣體流量(針對干法刻蝕)等參數,以確保刻蝕的效果符合要求。

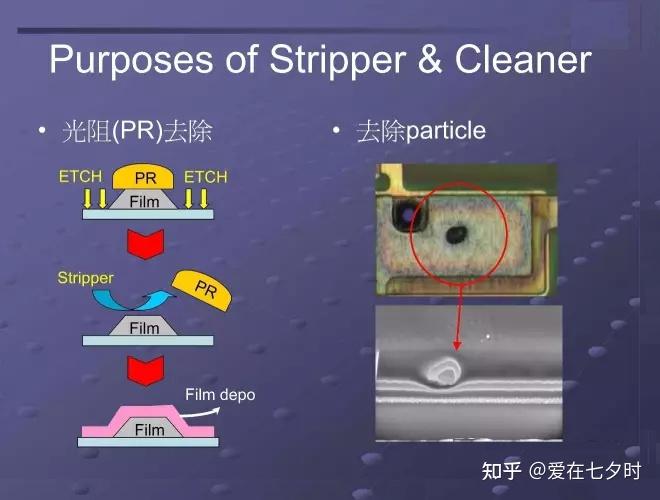

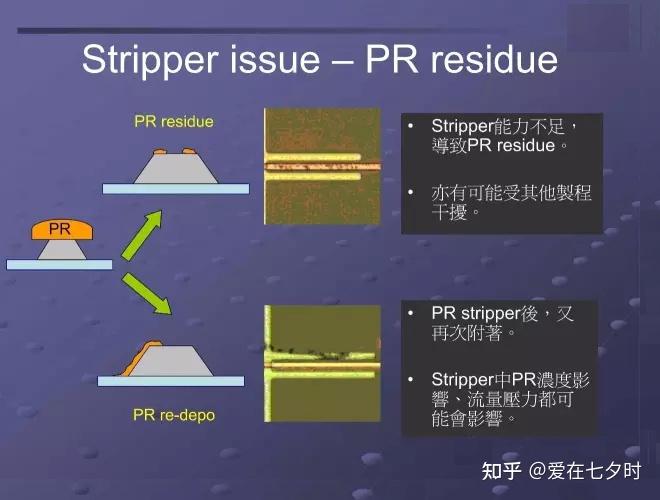

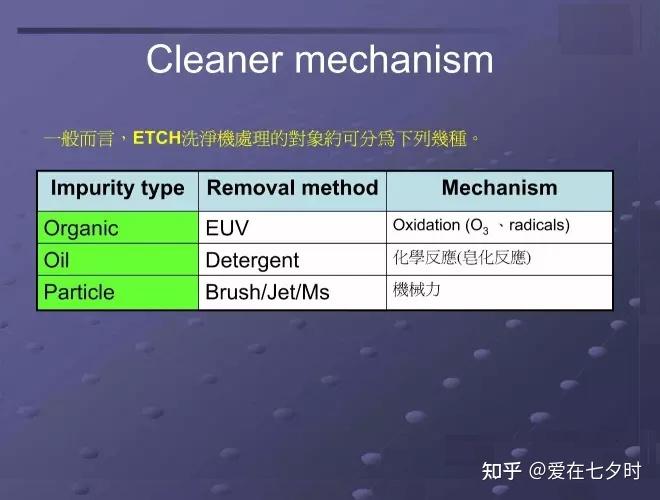

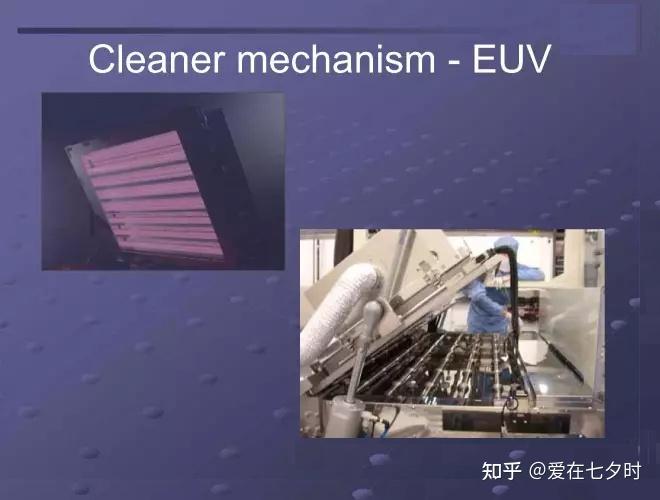

4、后處理

刻蝕完成后,需要對晶圓進行清洗和檢測。清洗過程主要是去除殘留的光刻膠和刻蝕產物,檢測過程包括對刻蝕深度、圖案尺寸和形狀等參數的測量,確保刻蝕后的圖案符合設計要求。

七、“刻蝕”工藝的參數

1、刻蝕速率(Etch Rate)

定義:單位時間內材料被去除的厚度(如 nm/min 或 ?/min)。

影響因素:

干法:等離子體功率、氣體流量、壓力、離子能量。

濕法:溶液濃度、溫度、攪拌速度。

重要性:速率過高可能導致過刻蝕,過低則影響生產效率。

2、刻蝕均勻性(Uniformity)

定義:刻蝕速率在晶圓表面或圖形間的差異(通常用百分比表示,如 ±5%)。

影響因素:

干法:等離子體分布、氣體流動均勻性、腔體設計。

濕法:溶液攪拌、晶圓旋轉、浸泡時間。

關鍵指標:片內均勻性(WIW)和片間均勻性(WTW)。

3、選擇性(Selectivity)

定義:刻蝕目標材料與掩膜或下層材料的刻蝕速率比(如 Si:SiO? = 50:1)。

影響因素:

干法:氣體化學(如 Cl? 對 Si 高選擇性)、離子能量。

濕法:溶液成分(如 HF 對 SiO? 高選擇性)。

重要性:高選擇性保護掩膜和底層結構,減少損傷。

4、各向異性(Anisotropy)

定義:刻蝕的垂直方向與橫向刻蝕的比例(完全各向異性 = 無橫向刻蝕)。

影響因素:

干法:離子轟擊方向(如 RIE)、側壁鈍化(如 Bosch 工藝)。

濕法:通常各向同性(橫向鉆蝕明顯)。

應用場景:高深寬比結構(如 TSV、FinFET)需高各向異性。

5、刻蝕剖面(Etch Profile)

定義:刻蝕后結構的側壁形貌(如垂直、錐形、倒梯形)。

關鍵參數:

側壁角度:90°為理想垂直剖面。

粗糙度:側壁光滑度(影響器件性能)。

控制方法:調整離子能量、氣體化學、溫度。

6、負載效應(Loading Effect)

定義:刻蝕速率因圖形密度或面積不同而變化的現象。

類型:

宏觀負載效應:晶圓間刻蝕速率差異。

微觀負載效應:圖形密集區與稀疏區速率差異。

解決方案:優化等離子體均勻性、調節氣體流量。

7、殘留物與聚合物(Residue/Polymer)

定義:刻蝕后殘留的副產物(如碳氟聚合物)。

來源:

干法:氣體反應不完全(如 CF? 刻蝕 Si 產生 SiF? 和 C?F?)。

濕法:金屬離子殘留(如 Al 刻蝕后 Cu 污染)。

清除方法:O? 等離子體灰化、濕法清洗(RCA)。

下面是干法刻蝕和濕法刻蝕的關鍵參數控制表格:

八、“刻蝕”工藝技術的詳細介紹

以下就是要跟大家分享的具體內容,希望感興趣的朋友可以加入我的“知識星球”,一起多多交流學習:

http://weixin.qq.com/r/QhAjO9TE64mUrZBY90VQ (二維碼自動識別)

因為本PPT章節太多,剩下部分如有朋友有需要,可加入我“知識星球”免費下載PDF版本。注意:此資料只可供自己學習,不可傳閱,平臺有下載記錄,切記!文末有加入“星球”方式,歡迎加入后一起交流學習。

九、“刻蝕”工藝當前面對的挑戰

1、3D NAND的高深寬比(HAR)刻蝕挑戰

(1)深孔/深槽刻蝕

128層及以上3D NAND需刻蝕深寬比>60:1的通道孔(如7μm深、<100nm寬),離子和反應物傳輸困難,易導致刻蝕不完全或側壁扭曲。

(2)掩膜消耗與選擇比

高能離子轟擊加速掩膜(如碳硬掩膜)消耗,需開發新型掩膜材料或優化刻蝕氣體配比。

2、先進制程的高精度要求

(1)納米級刻蝕控制

在5nm及以下制程中,刻蝕精度需達到原子級別(如<1nm),傳統刻蝕方法難以滿足要求。原子層刻蝕(ALE)雖能實現單原子層去除,但工藝復雜且成本高昂。

(2)關鍵尺寸(CD)均勻性

多重曝光技術(如EUV+SAQP)要求刻蝕后線寬誤差控制在±0.5nm以內,否則影響器件性能。

3、國產化技術瓶頸

(1)高端設備依賴進口

中國刻蝕設備的國產化率在2025年已達到約20%,但7nm以下刻蝕設備仍由泛林(Lam)、東京電子(TEL)壟斷,國產設備(如中微CCP)在5nm驗證中但市占率不足10%,

(2)關鍵零部件卡脖子

射頻電源、真空泵等核心部件依賴歐美日供應鏈。

十、“刻蝕”工藝未來的發展

刻蝕技術就像醫生手中的手術刀,其技術演化直接決定摩爾定律乃至后摩爾時代芯片制造的發展趨勢,新型材料和智能化Al的運用將形成新的驅動力推動刻蝕技術發展。

原子層刻蝕(ALE):單原子層精度控制。

AI工藝優化:通過大數據實時調節刻蝕參數。

新型等離子體源/新型氣體化學:如超低溫ICP(-50°C)減少損傷,NF?/Ar混合氣體提升SiC刻蝕速率(>2μm/min)。

總之,由于“刻蝕”工藝技術是緊隨光刻技術而來,它涉及使用化學或物理方法去除硅片上多余的材料,以形成所需的圖案。這一過程中,精確控制刻蝕的深度和位置至關重要。刻蝕技術的發展同樣對提高芯片質量和性能起著關鍵作用。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30806瀏覽量

264746 -

光刻

+關注

關注

8文章

364瀏覽量

31354 -

刻蝕

+關注

關注

2文章

220瀏覽量

13783 -

刻蝕工藝

+關注

關注

2文章

42瀏覽量

8809

發布評論請先 登錄

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

Sic mesfet工藝技術研究與器件研究

6英寸半導體工藝代工服務

蘇州華林科納半導體設備技術有限公司招賢納士

半導體工藝技術的發展趨勢

半導體工藝技術的發展趨勢是什么?

半導體行業之刻蝕工藝技術

等離子刻蝕工藝技術基本介紹

半導體“刻蝕(Etch)”工藝技術的詳解;

半導體“刻蝕(Etch)”工藝技術的詳解;

評論