【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

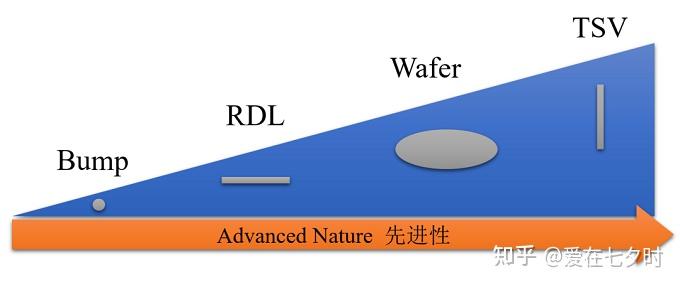

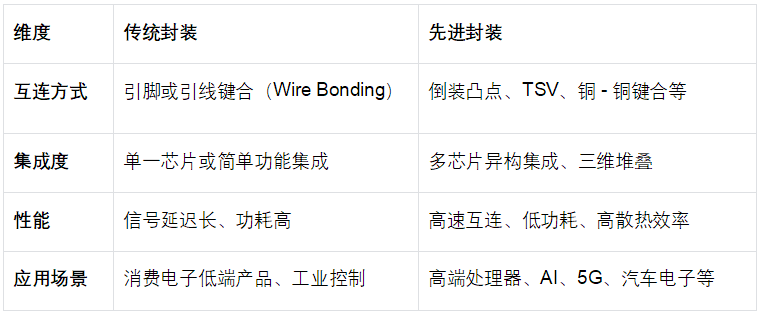

隨著電子設備向更小型化、更高性能的方向發展,傳統的芯片互連技術已經無法滿足日益增長的需求。在這樣的背景下,重布線層(RDL)工藝技術應運而生,因為與傳統封裝相比,當前先進封裝技術憑借三大核心優勢脫穎而出:顯著提升芯片功能密度、大幅縮短互聯距離、實現系統級重構。而這一技術飛躍的實現,很大程度上得益于重布線層(RDL)工藝技術的突破性應用,從而成為了先進封裝技術中的核心之一。

封裝中的重布線層(RDL)工藝是集成電路封裝設計中的一個重要層次,主要用于實現芯片內電氣連接的重新分配,并且在封裝中起到連接芯片和外部引腳之間的橋梁作用。重布線層(RDL)的設計和實現直接影響到封裝的電氣性能、可靠性和制造成本。

一、重布線層(RDL)工藝技術的概述

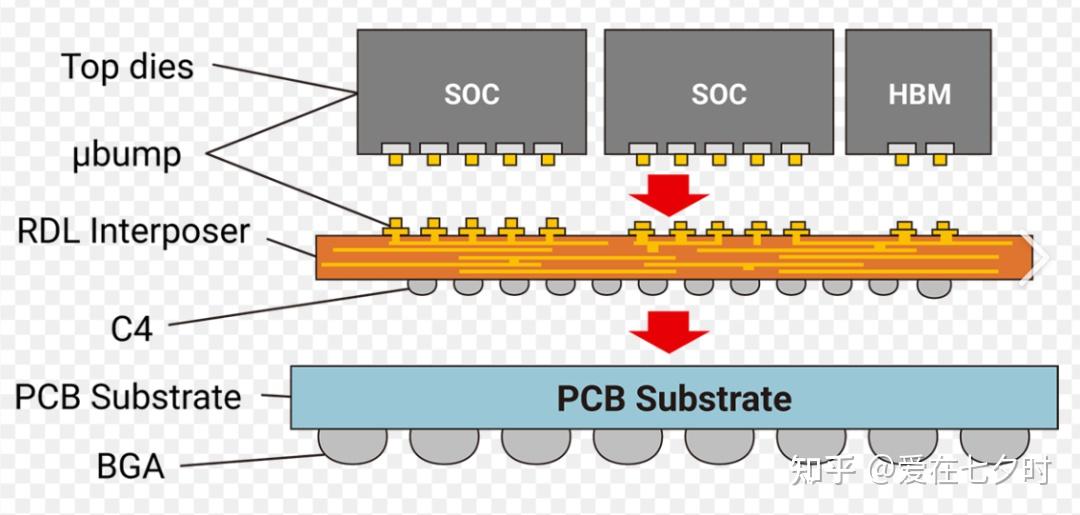

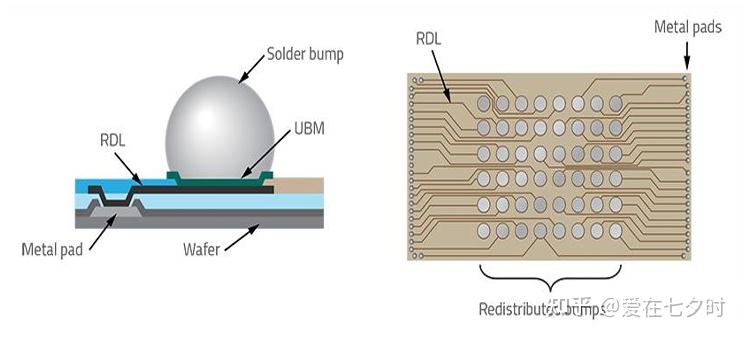

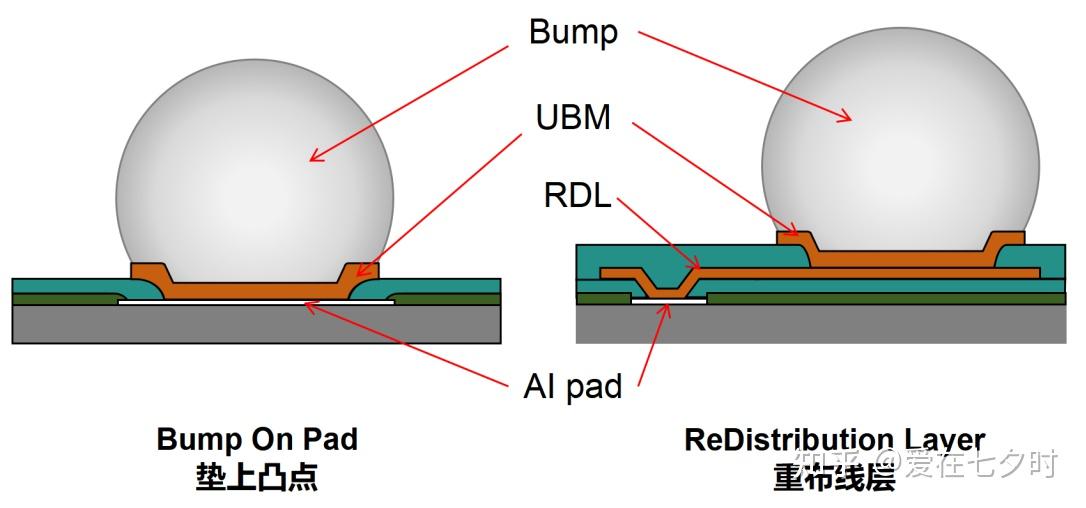

重布線層,英文全稱:Re-Distribution Layer,簡稱:RDL。它是先進封裝的關鍵互連工藝之一,其核心目的是將多個芯片集成到單個封裝中。該工藝通過在介電層頂部創建圖案化金屬層,將IC的輸入/輸出(I/O)重新分配到新位置(通常位于芯片邊緣),從而利用標準表面貼裝技術(SMT)實現IC與印刷電路板(PCB)的高效連接。RDL技術不僅使設計人員能夠以緊湊且高效的方式布局芯片,還能顯著減少器件的整體占地面積,成為實現高密度異構集成的核心技術支撐。

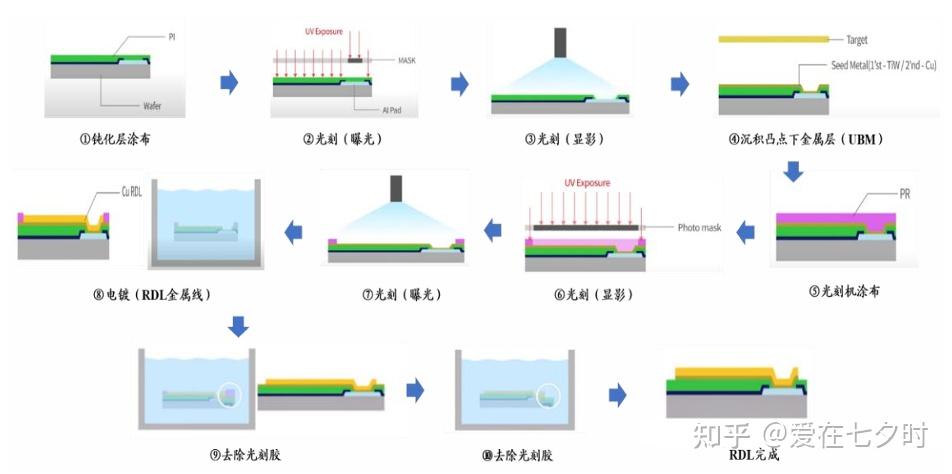

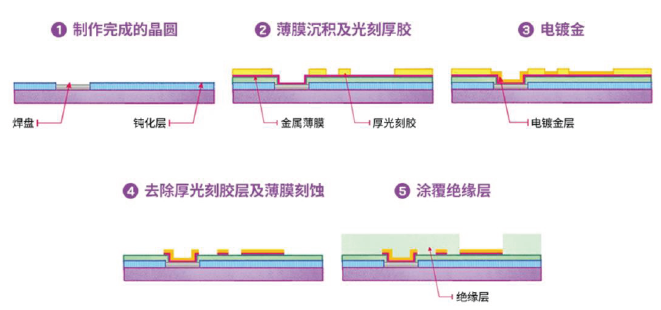

晶圓級金屬重布線制程在IC上涂布一層絕緣保護層,再以曝光顯影的方式定義新的導線圖案,然后利用電鍍技術制作新的金屬線路,以連接原來的芯片引腳和新的凸點,達到芯片引腳重新分布的目的。重布線層的金屬線路以電鍍銅材料為主,根據需要也可以在銅線路上鍍鎳金或者鎳鈀金材料,相關核心材料包括光刻膠、電鍍液、靶材、刻蝕液等。

二、IC輸入/輸出(I/O)數量的介紹

業內人都知道:想要在微縮化的芯片世界中,通過重布線層(RDL)工藝妙地重新布局IC輸入/輸出(I/O)焊盤,實現高性能與高可靠性的雙重飛躍就一定先要了解“輸入/輸出(I/O)”,那究竟什么是輸入/輸出(I/O)呢?

其實,輸入/輸出(I/O)的縮寫“I/O”是“Input/Output”的英文首字母。而輸入/輸出(I/O)數指的就是芯片上輸入輸出端口的數量,也可以說是引腳的數量。I/O數量越多,芯片可以同時傳輸的數據量就越大,處理速度越快。

1、重布線層(RDL)重塑輸入/輸出(I/O)的未來

重布線層(RDL)這個看似簡單的縮寫背后,承載著半導體封裝領域的一次革命性變革。在追求更高集成度、更快數據傳輸速度的今天,重布線層(RDL)工藝將芯片的輸入/輸出(I/O)焊盤從密集的中心區域遷移至邊緣,并在更廣闊的空間內重新分布。這一創新不僅極大地緩解了輸入/輸出(I/O)端口擁擠的問題,更為先進封裝技術如3D封裝、扇出型封裝(FOWLP)等提供了強有力的支持,使得芯片能夠擁有更多的輸入/輸出(I/O)數量,從而滿足日益增長的數據傳輸需求。

2、輸入/輸出(I/O)數量是速度與效率的雙重考量

輸入/輸出(I/O)數量是衡量芯片與外界通信能力的關鍵指標,直接關乎到芯片的數據吞吐量與處理速度。想象一下,一個擁有眾多輸入/輸出(I/O)端口的芯片,就像是一個四通八達的交通樞紐,能夠同時處理來自多個方向的數據流,實現信息的快速交換與處理。因此,隨著云計算、大數據、人工智能等技術的蓬勃發展,對芯片輸入/輸出(I/O)數量的需求也在不斷攀升。RDL工藝正是在這一背景下應運而生,它通過優化輸入/輸出(I/O)布局,讓芯片在有限的面積內實現更高的數據傳輸效率。

三、重布線層(RDL)技術的工藝流程

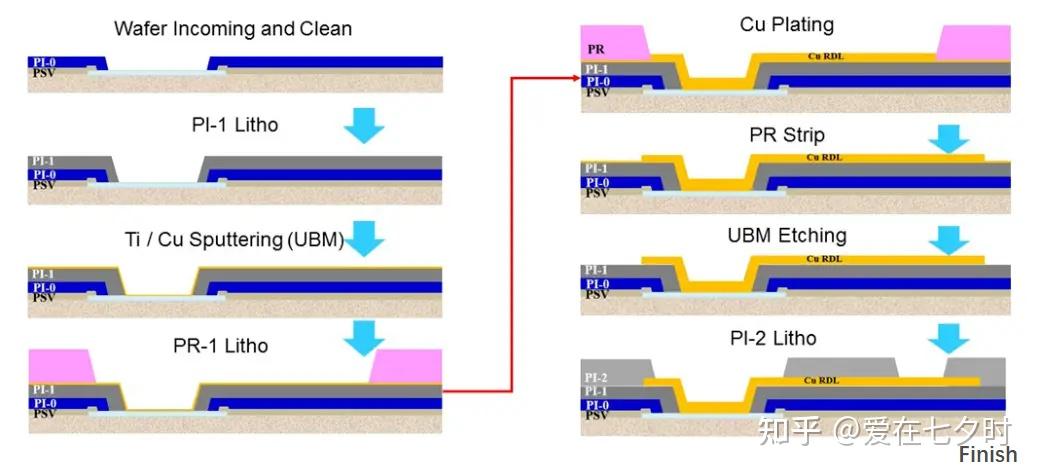

1、晶圓清洗

晶圓清洗是RDL工藝的第一步,通過物理和化學方法去除晶圓表面的雜質和顆粒,為后續的工藝步驟創造一個干凈、無污染的工作環境。這一步驟對于提高光刻膠和金屬沉積層的附著性至關重要。

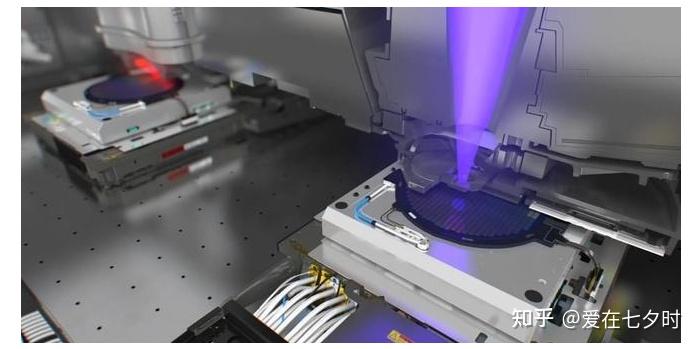

2、PI-1 Litho(第一層PI光刻)

在這一步中,利用PSPI(光敏性聚酰亞胺)光刻工藝,在晶圓上精確地制作出第一層鈍化層(PI-1)的圖案。PSPI作為一種高性能的光刻材料,能夠在紫外光照射下發生化學變化,從而實現圖案的精確轉移。這一過程為后續的金屬沉積提供了必要的保護屏障。

3、Ti/Cu Sputtering(鈦/銅濺射沉積)

緊接著,進行鈦/銅濺射沉積,形成底部金屬層(UBM)。鈦層作為緩沖層,能夠有效隔離銅層與鈍化層之間的直接接觸,防止銅原子擴散;而銅層則作為電鍍的種子層,為后續的電鍍工藝提供了均勻的基底。

4、PR-1 Litho(第一層光刻膠光刻)

在UBM層上涂布一層光刻膠,然后通過曝光和顯影工藝,精確地定義出RDL的圖案。這一層光刻膠就像一張精密的“地圖”,指引著銅電鍍的方向,保護著不需要電鍍的區域,同時在需要電鍍的區域暴露出銅層。

5、銅電鍍(Cu Plating)

在光刻膠露出的區域進行銅電鍍,形成RDL的導電層。這一步驟是RDL工藝的核心,通過電鍍的方式將銅沉積在暴露的UBM層上,形成連接芯片的焊盤和封裝外部引腳的導電通道。

6、光刻膠去除(PR Strip)

電鍍完成后,需要去除光刻膠,以便進行后續的工藝步驟。這一步通常采用化學方法,將光刻膠從晶圓表面剝離。

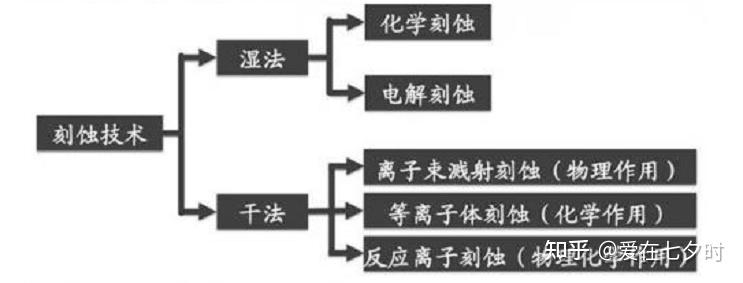

7、UBM層蝕刻(UBM Etching)

采用濕法刻蝕技術,去除不需要的UBM層,只保留在RDL電鍍區域下方的UBM層。這一步驟確保了RDL結構的精確性和完整性。

8、PI-2 Litho(第二層PI光刻)

最后,進行第二層PI光刻,為RDL提供額外的保護。這一層PI層不僅增強了RDL的機械強度,還提高了封裝的可靠性,確保芯片在惡劣環境下仍能穩定工作。

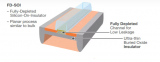

四、重布線層(RDL)工藝的構造材質

重布線層(RDL)的構造并非隨意為之,而是經過精心設計的材料組合。阻擋層通常采用Ti/Cu(鈦/銅)結構,鈦層作為緩沖層,能夠有效防止銅原子向鈍化層擴散,同時增強銅層與鈍化層之間的粘附力;銅層則作為電鍍的種子層,為后續的電鍍工藝提供堅實的基礎。互聯材料選用導電性能優異的銅,確保信號在重布線層(RDL)中的高效傳輸。而介質材料則多采用聚酰亞胺(PI),以其良好的絕緣性、耐熱性和機械強度,為重布線層(RDL)提供必要的保護與支撐。

五、重布線層(RDL)工藝的設計目標

1、信號分配

重布線層(RDL)的一個主要目標是將芯片的I/O(輸入/輸出)信號有效地分配到封裝的不同區域。這樣做可以優化信號傳輸路徑,減少信號延遲和串擾。

2、電源分布

除了信號線的布置外,重布線層(RDL)還負責電源層的布置,確保芯片和封裝基板之間的電流穩定傳輸,避免過高的電流密度導致過熱或燒毀問題。

3、尺寸與性能平衡

通過優化重布線層(RDL)的布局,設計師可以在保持小封裝尺寸的同時,滿足高性能的要求。這對于高集成度的芯片尤為重要。

六、重布線層(RDL)工藝的設計步驟

重布線層(RDL)的設計通常包括以下幾個步驟:

1、信號分配分析

在設計重布線層(RDL)之前,首先要評估芯片內部的信號連接方式,分析每個I/O引腳的功能和其需要的連接路徑。通過與芯片設計團隊協作,確保信號線的最優布局。

2、布線設計

根據需求進行具體的重布線層(RDL)布線設計。重布線層(RDL)通常采用多層結構,通過不同層次的線路進行信號和電源的分配。設計時需要考慮布線路徑、走線長度、寬度、間距等,以優化電氣性能并避免信號干擾。

3、電氣性能仿真

在設計完成后,通過仿真工具對重布線層(RDL)進行電氣性能驗證。這包括信號完整性(SI)和電源完整性(PI)分析,確保高頻信號不會因布線不當產生衰減,電源分布穩定。

4、熱力分析與優化

由于高功率芯片會產生大量熱量,重布線層(RDL)的設計還需要進行熱力學分析。通過模擬熱流和散熱路徑,確保封裝內的溫度不會過高,避免對芯片性能產生負面影響。

5、制造與測試驗證

重布線層(RDL)設計完成后,進入制造階段。制造時需要根據設計圖紙進行多層基板的制作,并通過各種測試方法驗證重布線層(RDL)的電氣連接性和機械穩定性,確保封裝可以順利通過后續的可靠性測試。

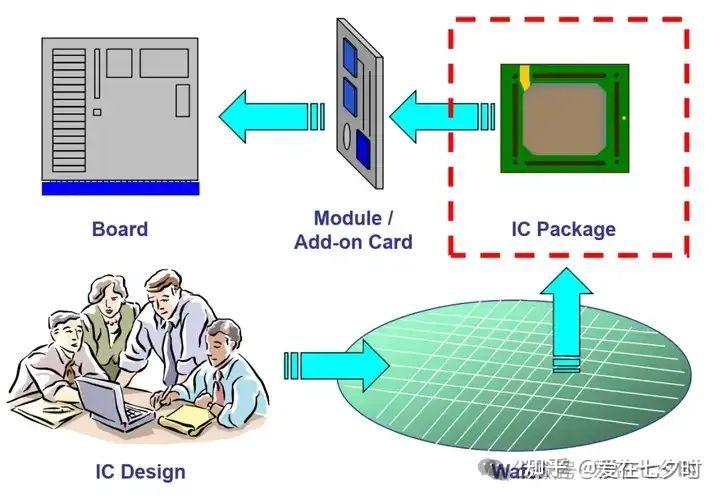

七、重布線層(RDL)工藝技術與封裝的關系

重布線層(RDL)層通常作為芯片封裝的核心組成部分,與其他封裝結構(如基板、外部引腳等)緊密配合。它不僅為芯片和封裝基板之間的連接提供了通路,還決定了封裝的電氣性能、散熱性能以及最終的封裝尺寸。

例如,像BGA(Ball Grid Array)或FCBGA(Flip Chip Ball Grid Array)封裝中,RDL負責將芯片的I/O引腳重分布到基板上的焊球位置,確保信號從芯片傳輸到封裝外部的電路板。

八、重布線層(RDL)工藝的技術挑戰

1、多層結構復雜性

重布線層(RDL)設計需要使用多層布線,這增加了設計的復雜性。設計師需要平衡信號傳輸質量、熱性能和機械穩定性等因素。

2、信號完整性問題

隨著芯片頻率和集成度的增加,重布線層(RDL)中的信號完整性問題變得愈發嚴重。如何減少信號的損失、避免信號串擾、提高抗干擾能力是重布線層(RDL)設計的關鍵。

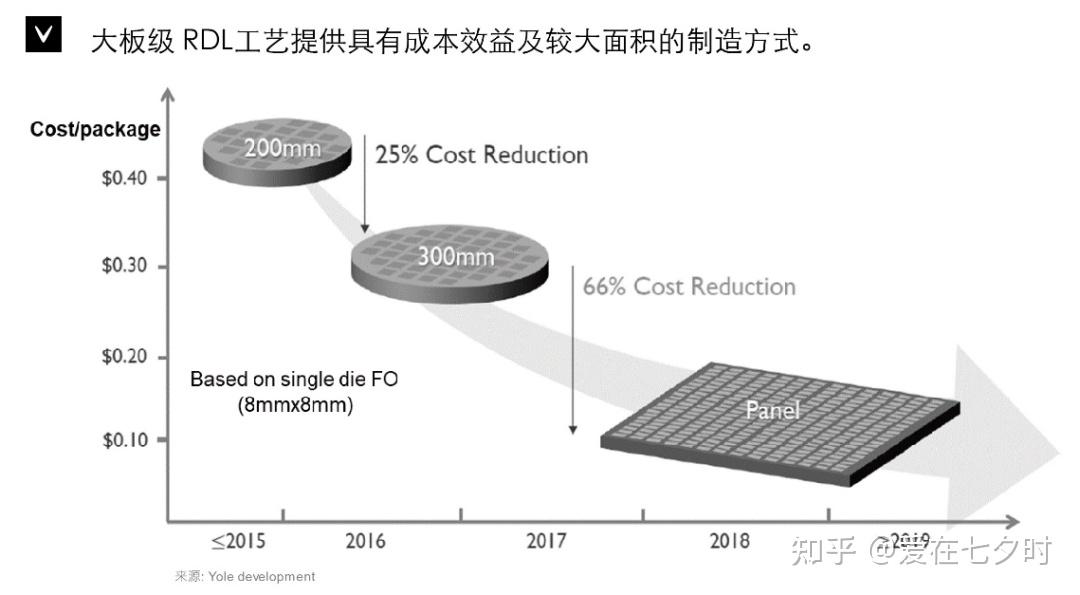

3、尺寸與成本控制

在保證性能的前提下,重布線層(RDL)的設計需要盡量減少封裝的體積和制造成本。因此,如何通過優化布線來減小封裝尺寸,并確保成本可控,是設計過程中必須考慮的因素。

九、重布線層(RDL)工藝的應用與發展趨勢

當前,重布線層(RDL)工藝的應用的應用領域主要有以下幾方面:

1、AI/HPC芯片

(1)2.5D封裝:CoWoS用RDL替代硅中介層連接GPU與HBM(成本降低30%)

(2)3D IC:混合鍵合前的臨時互聯層

2、移動設備

Fan-Out WLP:蘋果A系列處理器用重布線層(RDL)直接連接PCB,厚度減少40%

3、汽車電子

耐高溫重布線層(RDL):摻釕銅導線可在150℃下穩定工作

4、CIS傳感器

超細線路:0.8μm 重布線層(RDL)實現2000萬像素傳感器布線

重布線層(RDL)技術作為先進封裝的核心互連方案,通過重分布芯片I/O信號實現三大關鍵應用:在Flip Chip封裝中優化焊球布局(Redistribute I/Os for bump alignment),在WLP晶圓級封裝中重構布線路徑(Reconfigure routing paths),以及在SiP系統集成中搭建多芯片互連橋梁(Bridge multi-die interconnection)。這項"萬能布線"技術(Universal wiring solution)既能突破芯片原生I/O限制,又可實現微米級互連,同時降低30%以上封裝成本,已成為從2.5D/3D封裝到Chiplet集成的關鍵使能技術。

隨著集成電路技術的不斷進步,封裝的要求也越來越高。重布線層(RDL)工藝技術在高性能芯片封裝中起著越來越重要的作用。尤其在像5G、AI、汽車電子等領域,對封裝的要求更是不斷提高。未來,重布線層(RDL)工藝技術將朝著更高頻、更小尺寸、更低成本的方向發展,同時加強與熱管理、可靠性分析等其他封裝領域的協同設計。

總結一下

重布線層(RDL)工藝是集成電路封裝中不可或缺的設計層,負責芯片與封裝之間的電氣連接與信號分配。它不僅影響封裝的電氣性能,還與封裝的尺寸、熱管理、成本等多個因素密切相關。隨著技術的發展,重布線層(RDL)工藝技術設計正變得越來越復雜,要求設計師在保證性能的同時,還需優化尺寸、成本,并解決信號完整性等技術挑戰。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30725瀏覽量

264036 -

先進封裝

+關注

關注

2文章

533瀏覽量

1026

發布評論請先 登錄

鍵合玻璃載板:半導體先進封裝的核心支撐材料

熱壓鍵合工藝的技術原理和流程詳解

半導體封裝Wire Bonding (引線鍵合)工藝技術的詳解;

半導體芯片封裝“CoWoS工藝技術”的詳解;

關于先進碳化硅(Sic)功率半導體封裝工藝技術的詳解;

半導體“封裝過程”工藝技術的詳解;

半導體“刻蝕(Etch)”工藝技術的詳解;

半導體先進封裝“Bumping(凸點)”工藝技術的詳解;

半導體“光刻(Photo)”工藝技術的詳解;

SOI工藝技術介紹

半導體先進封裝“重布線層(RDL)”工藝技術的詳解;

半導體先進封裝“重布線層(RDL)”工藝技術的詳解;

評論